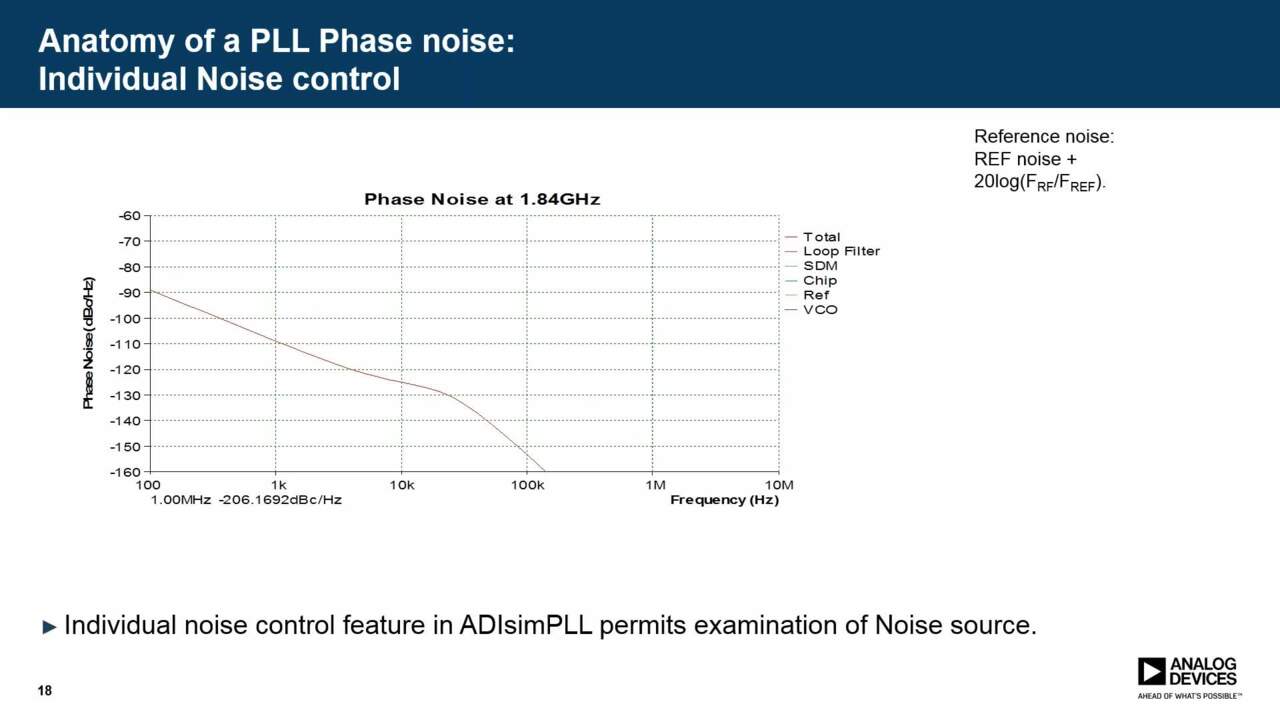

PLL Frequency Planning for Spurious Signal Elimination

Analog Devices developed a frequency planning technique, used in conjunction with Phase Locked Loop (PLL) devices, that can eliminate unwanted spurious signals in the output spectrum. Learn how the technique works, its benefits and how to apply it.

PLL Frequency Planning for Spurious Signal Elimination

| 圖片 | 製造商零件編號 | 說明 | 現有數量 | 價格 | 查看詳情 | |

|---|---|---|---|---|---|---|

|  | 129856-HMC704LP4E | EVAL BOARD FOR HMC704LP4E | 0 - 即時供貨 | See Page for Pricing | 查看詳情 |

|  | EKIT01-HMC703LP4E | EVAL BOARD FOR HMC703LP4E | 2 - 即時供貨 | $8,790.92 | 查看詳情 |

|  | EKIT01-HMC830LP6GE | EVAL BOARD FOR HMC830LP6GE | 0 - 即時供貨 | See Page for Pricing | 查看詳情 |

|  | EVAL01-HMC1031MS8E | EVAL BOARD FOR HMC1031MS8E | 0 - 即時供貨 | See Page for Pricing | 查看詳情 |

|  | EKIT01-HMC833LP6GE | EVAL BOARD FOR HMC833LP6GE | 0 - 即時供貨 | See Page for Pricing | 查看詳情 |