計時抖動與相位雜訊有何分別?

市場對於更快取得更多資料的需求日漸提升,為了因應此需求,序列數據傳輸率也跟著攀升。隨著數據傳輸率增加,時序餘裕減少,迫使設計人員必須將數據時序的不確定性降至最低程度。在指定數據時序的不確定性時,可採用兩種形式中的任一種,視您的專業背景而定。其中有兩個參數分別為抖動與相位雜訊。

相位雜訊與抖動都可指出訊號的時序穩定性,而且兩者彼此相關。總之,這是描述時脈或數據流時序不確定性的兩種方式。相位雜訊代表訊號頻率的不穩定性,以頻域表示;而抖動則代表時域中訊號波形的變化。

時域或頻域的選擇,通常取決於應用:RF 工程師一般會考慮相位雜訊,而數位設計人員則更可能採用抖動。

抖動與相位雜訊的定義及測量

抖動是訊號時序偏離理想狀態的變化,通常是用示波器進行測量。抖動的形式可能有幾種,包括邊緣或相位抖動 (稱為時間間隔誤差)、週期抖動,或逐週期抖動 (即相鄰週期之間的差異)。任何型態的抖動還可細分成兩個主要部分,即隨機抖動或確定性抖動。隨機抖動一般是無限值,亦即抖動峰值會隨時間增加而提高。確定性抖動元素則是有限值,不會隨時間而提高。每個主要部分都包含多個子部分,但不屬於本文的討論範圍。

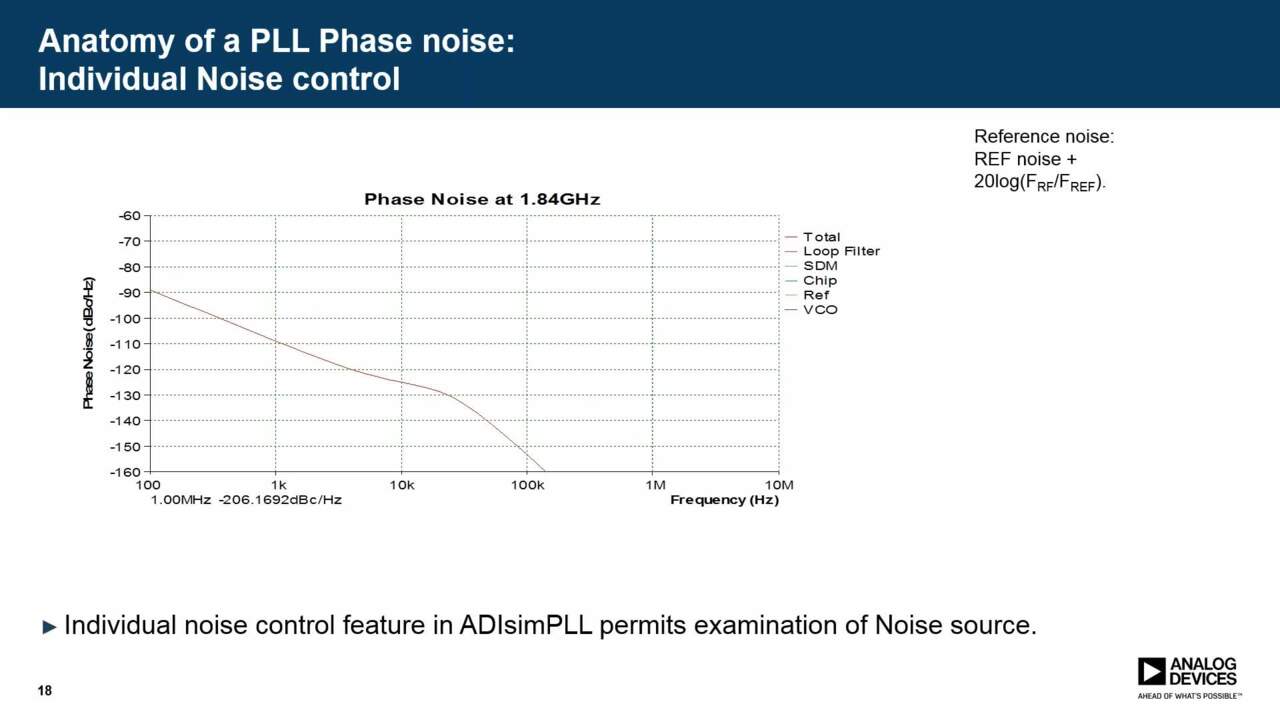

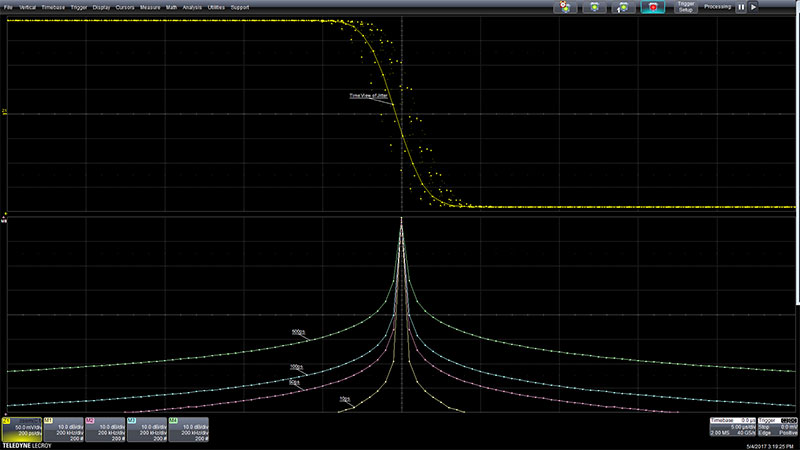

相位雜訊的重點在於頻域中時脈基頻鄰近的訊號功率。而訊號相位或頻率的變化,則會以譜線寬度的形式表現。時序的不穩定性越大,譜線就會越寬。圖 1 提供相關範例。

圖 1:時脈訊號之抖動 (上方軌跡) 與相位雜訊 (下方軌跡) 的比較圖。(圖片來源:DigiKey)

圖 1:時脈訊號之抖動 (上方軌跡) 與相位雜訊 (下方軌跡) 的比較圖。(圖片來源:DigiKey)

上方軌跡顯示出 100 MHz 時脈訊號的邊緣。此圖有啟用顯示持續性功能,以便查看邊緣位置的歷程。時脈邊緣隨著時間在水平方向移動,這個變化即為時脈邊緣抖動。在此情況下,大約有 100 ps 的峰對峰抖動。

下方軌跡是以功率密度顯示方法,針對 100 MHz 時脈訊號的頻譜所呈現的水平延伸圖。其中有四個重疊頻譜,顯示出 10、50、100 與 500 ps 邊緣抖動值在頻譜寬度上的差異。請注意,譜線因抖動量增加而變寬。相位雜訊一般是以頻譜分析儀或專用型相位雜訊測試組測量而得,而且通常是在與時脈基頻有固定頻率偏移的情況下出現。舉例來說,當載波偏移為 10 kHz 時,相位雜訊可能指定為 -96 dBc。

抖動與相位雜訊的控制

設計人員可以利用低相位雜訊時脈產生器,例如 Analog Devices 的 ADF4001BCPZ,來控制時脈分配鏈中的抖動與相位雜訊。本產品提供 200 MHz 頻寬,在與時脈頻率偏移 1 kHz 下,典型相位雜訊規格為 -99 dB/Hz (圖 2)。

圖 2:Analog Devices 的 ADF4001BCPZ 是一款 200 MHz 低相位雜訊時脈產生器,在與時脈頻率偏移 1 kHz 下,典型相位雜訊規格為 -99 dB/Hz。(圖片來源:Analog Devices)

圖 2:Analog Devices 的 ADF4001BCPZ 是一款 200 MHz 低相位雜訊時脈產生器,在與時脈頻率偏移 1 kHz 下,典型相位雜訊規格為 -99 dB/Hz。(圖片來源:Analog Devices)

若要將時脈分配給多個元件,需要使用零延遲時脈緩衝器。除了保證達到超低計時偏斜外,這些元件更可透過內部鎖相迴路 (PLL) 來降低抖動。舉例來說,Cypress Semiconductor 的 CY2308SXC-3T 零延遲緩衝器有兩排輸出,各有四個輸出端。工作頻率範圍為 10 至 133 MHz,輸出端的典型逐週期抖動為 60 ps (圖 3)。

圖 3:Cypress Semiconductor 的 CY2308SXC-3T 零延遲緩衝器採用 16-SOIC 封裝,輸出端的典型逐週期抖動為 60 ps。(圖片來源 Cypress Semiconductor)

圖 3:Cypress Semiconductor 的 CY2308SXC-3T 零延遲緩衝器採用 16-SOIC 封裝,輸出端的典型逐週期抖動為 60 ps。(圖片來源 Cypress Semiconductor)

結論

綜上所述,本文開頭的問題可以這樣回答:相位雜訊與抖動是關於時脈或數據時序穩定性的一體兩面。相位雜訊是用來檢視頻域,而抖動則是檢視時域。挑選良好的元件有助於減少相位雜訊與抖動。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum