鎖相迴路頻率合成器的的基礎知識

資料提供者:DigiKey 北美編輯群

2021-02-03

在高速序列通訊匯流排中提高數據傳輸率需要具有較高頻率、優異穩定性、更佳頻率解析度、更高訊號純度的系統時脈。直接數位合成器可提供這些特性,但僅限於低於 2 或 3 GHz 的頻率。高達數十 GHz 的頻率需要其他解決方案。

此解決方案首先採用鎖相迴路 (PLL) 基礎類比頻率合成器,可以生成高達 30 GHz 的時脈頻率。接著,整數 N 合成器 (以一個整數值乘以參考頻率) 和分數 N 合成器 (以非整數的分數值乘以參考頻率) 運用特殊技術,將相位雜訊和類似的訊號雜質降至最低。

本文說明採用 Analog Devices 範例元件的整數 N 和分數 N 頻率合成器設計。本文也同時提出讓這些元件可用於高速序列資料鏈路和機動頻率雷達的創新技術。

整數鎖相迴路合成器

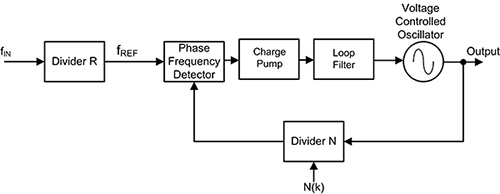

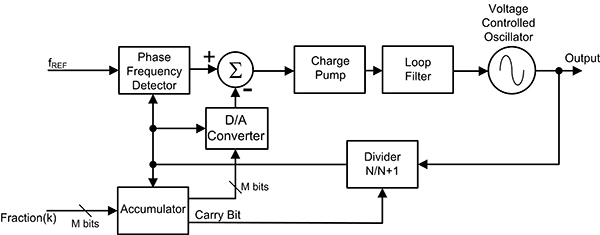

PLL 電路用於控制頻率與相位。PLL 可配置成時脈來源、頻率倍增器、解調器、追蹤產生器或時脈復原電路。這些應用都需要不同的特性,但全都使用同一個基本電路概念。圖 1 顯示一個配置為頻率倍增器的基本 PLL 方塊圖。

圖 1:傳統整數 N 鎖相迴路頻率合成器方塊圖。(圖片來源:DigiKey)

圖 1:傳統整數 N 鎖相迴路頻率合成器方塊圖。(圖片來源:DigiKey)

此電路的運作為所有鎖相迴路的典型方式。這其實是一個控制壓控振盪器 (VCO) 相位的回授控制系統。此輸入訊號施加於預調分頻器,將輸入頻率除以 R。此預調器的輸出為參考頻率,形成相位頻率偵測器 (PFD) 的一個輸入。

另一個 PFD 輸入則來自 N 分頻計數器輸出的回授訊號。在正常情況下,若 PLL 為鎖定,兩個訊號的頻率幾乎相同。相位偵測器的輸出是電壓,大小與兩個輸入的相位差成比例。在啟動或輸入有大幅瞬時頻移時,則迴路非鎖定,相位頻率偵測器便會導引 PLL 操作頻率至預期的設定。一旦達到預期頻率,PFD 會回歸相位偵測器模式,並且會有與參考頻率及回授訊號相位差成比例的輸出。

相位頻率偵測器驅動充電幫浦,此為雙極切換電流源。這表示其能輸出正和負電流脈衝至 PLL 的迴路濾波器。

此迴路濾波器會將相位錯誤訊號平滑化,並且決定 PLL 的動態特性。過濾後的訊號會控制 VCO。請注意,VCO 輸出的頻率是提供給頻率參考輸入至相位頻率偵測器輸入的 N 倍,並且是頻率輸入的 N/R 倍。此輸出訊號會透過 N 分頻計數器傳回相位偵測器。

通常,迴路濾波器的設計旨在符合 PLL 應用所要求的特性。如果 PLL 要擷取並追蹤訊號,迴路濾波器的頻寬會大於固定輸入頻率時的預期頻寬。PLL 接受並鎖定的頻率範圍稱為「擷取範圍」。一旦 PLL 鎖定並追蹤訊號,PLL 將遵循的頻率範圍稱為「追蹤範圍」。一般來說,追蹤範圍會大於擷取範圍。此外,PLL 迴路濾波器還會確定,訊號頻率變化最快且仍能保持鎖定的速度 (即最大迴轉率)。迴路濾波器頻寬越窄,相位誤差也就越小。代價則是回應速度變慢,擷取範圍縮小。在時脈應用中使用的 PLL 主要以固定頻率工作。一般而言,迴路濾波器的頻寬應比參考頻率小很多。

既然 PLL 輸出頻率為參考頻率的整數倍,其頻率解析度與參考頻率相等。要取得更精細的頻率解析度,需要降低參考頻率,這能藉由預調計數器 R 達成。

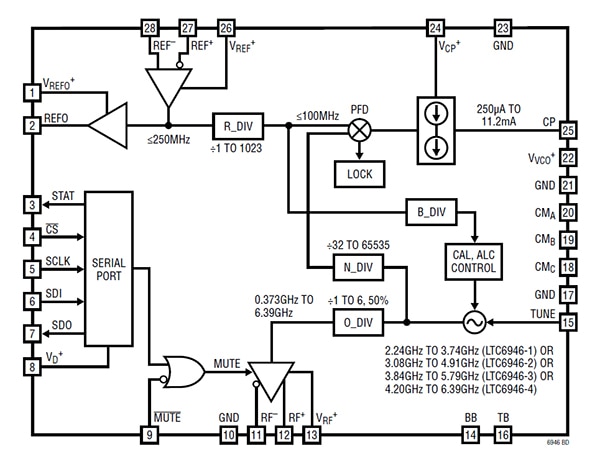

整數 N 頻率合成器的商用範例之一為 Analog Devices 的 LTC6946IUFD-3#PBF,這是低雜訊 0.64 至 5.790 GHz 合成器,具有整數 VCO 和優異的雜散效能 (圖 2)。此元件屬於四個合成器 IC 的一員,每個 IC 均有不同的頻率涵蓋範圍,介於 0.373 至 6.390 GHz。

圖 2:Analog Devices 的 LTC6946IUFD-3#PBF 整數 N 頻率合成器含整合式 VCO 方塊圖。(圖片來源:Analog Devices)

圖 2:Analog Devices 的 LTC6946IUFD-3#PBF 整數 N 頻率合成器含整合式 VCO 方塊圖。(圖片來源:Analog Devices)

此合成器需一個外部使用者供應迴路濾波器,藉此將特定應用最佳化。包含內部預調計數器分頻器,具有 1 至 1023 的相除範圍。迴路分頻器的範圍介於 32 至 65535。充電幫浦電流可調整,介於 250 mA 至 11.2 mA,可匹配迴路濾波器的需求。

分數 N 鎖相迴路合成器

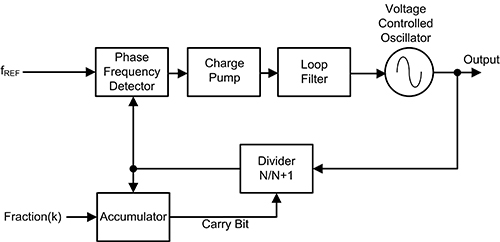

PLL 合成器的頻率解析度可藉由降低步進尺寸至低於整數值而提升,即在迴路分頻器中產生分數步進 (N)。這能透過動態變化或「顫動」倒數值達成。也就是在 PLL 輸出頻率為固定的循環下,將分頻器設定保持為 N 值,並且週期性步進至不同的值,例如 N+1。舉例而言,若分頻器在三個參考週期的設定值為 4、在第四個參考循環的值為 5,則有效的倒數值為 4.25。可使用累加器達成此效果,如圖 3 所示。

圖 3:使用累加器的分數 N PLL 合成器方塊圖,以調變分頻器計數。(圖片來源:DigiKey)

圖 3:使用累加器的分數 N PLL 合成器方塊圖,以調變分頻器計數。(圖片來源:DigiKey)

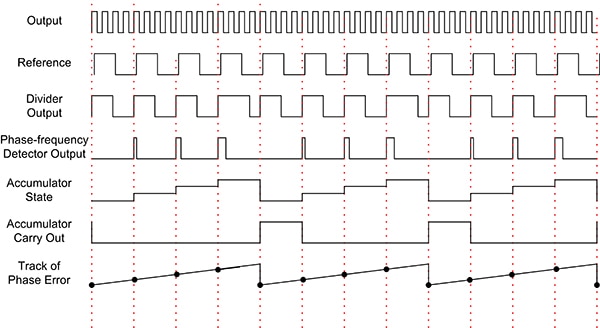

此累加器從分頻器計算輸出脈衝和每一個 M,其中,M 為累加器的模數,其輸出搭載會改變分頻器輸入的位元。圖 4 接著顯示設定分數分頻器設定至 4.25 的範例。

圖 4:使用累加器的分數 N 合成器計時圖。(圖片來源:DigiKey)

圖 4:使用累加器的分數 N 合成器計時圖。(圖片來源:DigiKey)

此累加器由分頻輸出驅動,並為模數四計數,即 M 等於四。每四個脈衝會產生一個搭載輸出,將分頻器計數增量一。累加器會重置然後再次進行計數。分頻器設定的增加會改變輸出頻率,造成累加相位偏移錯誤。相位錯誤的軌跡顯示脈衝值為時間的函數。

平均分頻器設定為 4.25,但合成器輸出經過相位調變,導致輸出雜波。累加器明顯顯示其追蹤相位錯誤。這能用於移除調變,如圖 5 所示。

圖 5:使用 D/A 轉換器累加器狀態消除分數 N 顫動造成的相位調變。(圖片來源:DigiKey)

圖 5:使用 D/A 轉換器累加器狀態消除分數 N 顫動造成的相位調變。(圖片來源:DigiKey)

累加器狀態透過數位類比 (D/A) 轉換器轉換為類比,並經過調整及從相位頻率偵測器輸出相減,可消除分數 N 顫動造成的相位調變。這必須謹慎處理,若修正訊號未精確匹配相位錯誤,就會在輸出會造成雜波。

加入三角積分調變器

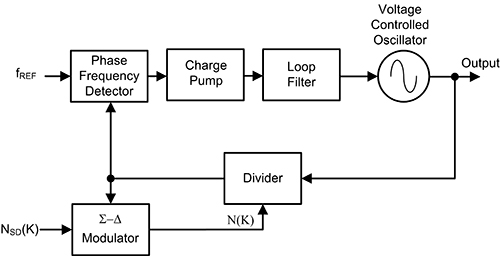

累加器的週期性是造成合成器雜散輸出的原因。若以三角積分調變器取代累加器,則數位計數可用於調變分頻器計數,這能將雜散響應和雜訊降至最低。圖 6 顯示此替代方式。

圖 6:以三角積分調變器替代累加器,能讓數位計數用於變化分頻器計數,以降低雜散響應。(圖片來源:DigiKey)

圖 6:以三角積分調變器替代累加器,能讓數位計數用於變化分頻器計數,以降低雜散響應。(圖片來源:DigiKey)

事實上,三角積分調變拓撲已採用兩種常用的數位技術。第一個技術為在較廣的範圍內增加 N 分頻器計數的數目,讓平均除頻因素產生預計的分數除頻器值。這會降低主要分數雜散。累加器架構合成器在兩個狀態中的計數會有所變化。這是第一階調變方式。n 階三角積分分數 PLL 會在 2n 的不同值之間調變 N 計數器。舉例而言,三階調變器會在八個不同的分頻器值之間交替,四階調變器會在 16 個不同的分頻器值之間交替。

第二個數位計數 (亦稱為顫動),將 2N 順序隨機化,使之偽隨機。這能在保有平均分數分頻器比率之下,轉換分數雜散為有形狀的隨機雜訊,進而能由 PLL 進行濾波。

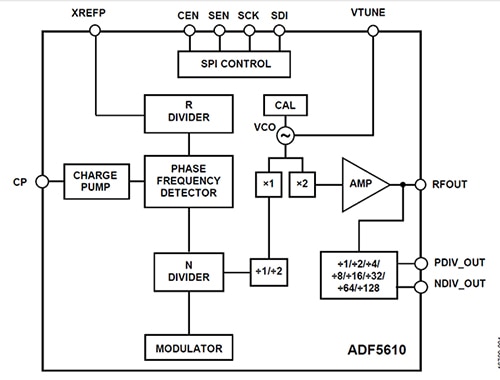

三角積分分數 N 合成器的商用型號之一為 Analog Devices 的 ADF5610BCCZ,此為低雜訊 0.57 MHz 至 14.6 GHz 分數 N 合成器,含整合式 VCO (圖 7)。

圖 7:Analog Devices 的 ADF5610BCCZ 方塊圖,此元件支援分數 N 或整數合成器配置。(圖片來源:Analog Devices)

圖 7:Analog Devices 的 ADF5610BCCZ 方塊圖,此元件支援分數 N 或整數合成器配置。(圖片來源:Analog Devices)

ADF5610 需外接參考振盪器和迴路濾波器。具有整合式 VCO,基頻為 3650 MHz 至 7300 MHz。這些頻率於內部加倍並路由到 RFOUT 引腳。具備一個差動輸出,能將加倍的 VCO 頻率除以 1、2、4、8、16、32、64、128,以產生低至 57 MHz 的 RF 輸出頻率。

ADF5610 使用先進的三角積分調變器,具有 24 位元分數模數,可達到極低的雜散訊號位準。如同使用三角積分調變器的所有合成器,此元件使用數位訊號處理技術以尋找合適的平均分數分頻器比率。此流程中,會以 PFD 頻率為時脈,產生輸出調變雜訊,稱為量化雜訊,具有高通頻率響應。外接低通迴路濾波器用於過濾此量化雜訊低於 VCO 相位雜訊的位準,避免此雜訊加入系統的整體相位雜訊。

ADF5610 亦包含一個準確的頻率模式,用於 0 Hz 頻率錯誤。此模式能夠產生介於相鄰整數 N 邊界步進的準確頻率,同時使用完整 24 位元相位累加器模數。這能達到準確的頻率步進,具有高相位偵測器比較率,在此模式下, PLL 可維持優異的相位雜訊和雜散效能。

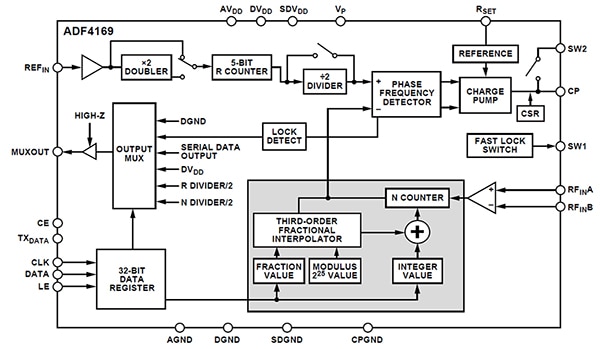

Analog Devices 的 ADF4169CCPZ-RL7 是 PLL 合成器的另一例,可配置為整數 N 或分數 N 元件。能以高達 13.5 GHz 的 RF 頻寬操作,具有調變和波形生成。採用外部參考頻率輸出、VCO、迴路濾波器。其三階三角積分調變器,用於分數 N 合成,可以解除使用,讓元件以 分數 N 模式運作 (圖 8)。

圖 8:Analog Devices 的 ADF4169CCPZ-RL7 使用三階三角積分調變器。(圖片來源:Analog Devices)

圖 8:Analog Devices 的 ADF4169CCPZ-RL7 使用三階三角積分調變器。(圖片來源:Analog Devices)

ADF4158WCCPZ-RL7 合成器預計用於頻率調變連續波 (FMCW) 雷達。包含鋸齒和三角斜坡在內的頻域內眾多類型調變波形。這是雷達應用中必要的特殊特點。

結論

設計人員若要以系統時脈解決方案,在高速通訊匯流排中提高數據傳輸率,必須超越使用適用於 3 GHz 的直接數位合成器。PLL 架構頻率合成器使用整數 N 和分數 N 拓撲,提供穩定、低雜訊訊號,用於高達數十 GHz 的高頻時脈、序列資料通訊、雷達應用。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。