類比基礎知識 - 第 3 篇:管線式 ADC 及其使用方法

資料提供者:DigiKey 北美編輯群

2020-07-14

編者說明:類比數位轉換器 (ADC) 可將類比世界連接至數位世界,因此對任何連接至真實世界的電子系統來說是基礎元件之一。此元件也是系統效能的重要決定因素。本系列文章將探討 ADC 的基礎知識、各種類型及其應用。第 1 篇討論 SAR ADC;第 2 篇討論三角積分 (ΔƩ) 轉換器;本文為第 3 篇,討論管線式 ADC 的功能、特性及使用方法。第 4 篇說明三角積分 ADC 如何產生超低雜訊的結果。第 5 篇探討 SAR ADC 的輸入驅動難題。

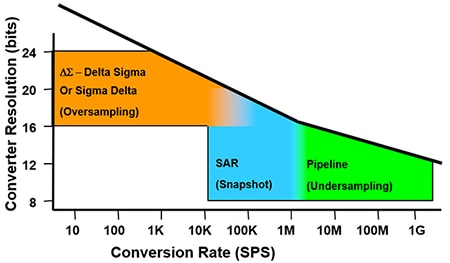

ADC 適用的一些應用包括:超高速多載波行動通訊基礎架構基地台、電信、數位預失真觀察,以及回程接收器等等,所有這些應用都逐漸要求 ADC 必須達到每秒取樣 10 億次的水準。本類比基礎知識系列的第 1 篇和第 2 篇中,個別討論了連續漸近暫存器 (SAR) ADC 及三角積分 (ΔƩ) ADC,以及如何在適合的應用中使用這些裝置。不過,這兩種技術都無法因應挑戰,達到每秒取樣 10 億次 (GSPS) 的水準。

舉例來說,由於 SAR ADC 使用「快照」演算法,加上採用序列法的關係,因此速度受限於 10 MSPS。在高解析度 ΔƩ ADC 的超取樣演算法中,則需要更多的時間來擷取多個樣本並求平均值,以達到高達 5 MHz 的 24 位元輸出數據傳輸率。GSPS 率遠遠超出 SAR ADC 和 ΔƩ ADC 的取樣頻率範圍。

管線式 ADC 能在處理多個樣本的同時,仍以 GSPS 速度將數據傳送到輸出,因此能克服這項超高速 ADC 的挑戰。

本文首先會簡單比較 ΔƩ、SAR 及管線式 ADC,接著探討與實現高速轉換器輸出有關的問題,以及管線式 ADC 為何是這些高速應用的絕佳替代方案。然後介紹 Texas Instruments 的兩款管線式 ADC (一款強調精確度,另一款則強調高速),以及說明如何開始使用這些元件。

何謂管線式 ADC?

管線式 ADC 由幾個連續的階段組成。第一階段為差動結構化階段,會先評估最高有效位元 (MSB) 值,然後對訊號進行調節,再將其傳遞到下一階段,進行 MSB-1 轉換。每個階段都與其他階段同時執行操作 (圖 1)。

圖 1:管線式拓撲具有多個階段,以轉換多位元轉換器的一個位元,然後對訊號進行調整並將其傳遞到下一階段。(圖片來源:Texas Instruments)

圖 1:管線式拓撲具有多個階段,以轉換多位元轉換器的一個位元,然後對訊號進行調整並將其傳遞到下一階段。(圖片來源:Texas Instruments)

在圖 1 中,各個階段的功能相似,而且只解析一個或兩個位元。每個階段都有取樣保持、低解析度快閃記憶體 ADC 和訊號調節功能。第一階段會接收樣本,隨即產生 MSB 決策。MSB 數位值會前往第一個閂鎖 (閂鎖 1)。如果 MSB 決策是 1,則此階段會從樣本中減去 MSB 值對應的電荷。然後,管線式轉換器會將 2 倍增益倍數套用至剩餘電荷。當某個階段完成操作時,此階段會將類比差異傳遞到後續階段。若設計具 2 倍增益,其優點是,第 1 階段至第 n 階段基本上是相同的電路。

階段數通常與 ADC 位元數相符。最終轉換輸出會在輸出閂鎖中結合每個階段的數位結果。此轉換過程會導致數據延遲數個時脈週期。

ΔΣ、SAR 和管線式 ADC 取樣的比較

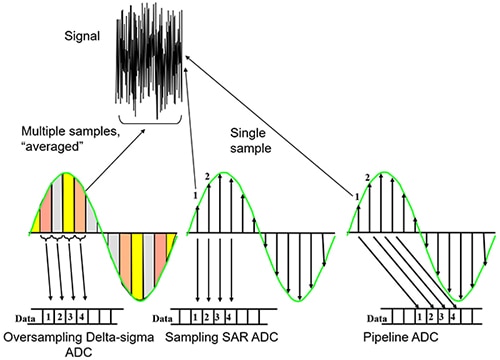

ΔΣ 轉換器使用超取樣演算法,來實作有限脈衝回應 (FIR) 或無限脈衝回應 (IIR) 數位濾波器。在擷取多個樣本時,這些濾波器會產生訊號輸出延時或延遲,同時呈現極高的解析度作為正向折衷。因此,擷取時間比 SAR 或管線式轉換器長,這兩個轉換器在每個轉換操作中,都只會對訊號取樣一次 (圖 2)。

圖 2:速度最慢、解析度最高的 ΔƩ ADC 用於較低頻訊號。中速、解析度中等的 SAR ADC 有利於一般用途應用。高速、解析度較低的管線式 ADC,則適用於進階高速解決方案。(圖片來源:DigiKey)

圖 2:速度最慢、解析度最高的 ΔƩ ADC 用於較低頻訊號。中速、解析度中等的 SAR ADC 有利於一般用途應用。高速、解析度較低的管線式 ADC,則適用於進階高速解決方案。(圖片來源:DigiKey)

SAR ADC 使用指定的擷取時間點來呈現輸入訊號的快照。在使用電荷再分配技術的同時,SAR 會快速完成零延遲的轉換。管線式轉換器使用欠取樣技術,藉由電荷再分配技術並延遲呈現輸出結果,來實現高速轉換。此轉換演算法會產生數據延遲。

對於 SAR、管線式和 ΔƩ 轉換器來說,其延遲與轉換速度之間的關係各不相同 (圖 3)。

圖 3:ΔƩ 超取樣和平均演算法會延遲呈現最終輸出數據字組。由於 SAR ADC 的輸出出現在下一次取樣之前,因此 SAR ADC 的延遲為零。若管線式轉換器的數據結果延遲,會導致非零延遲。(圖片來源:DigiKey)

圖 3:ΔƩ 超取樣和平均演算法會延遲呈現最終輸出數據字組。由於 SAR ADC 的輸出出現在下一次取樣之前,因此 SAR ADC 的延遲為零。若管線式轉換器的數據結果延遲,會導致非零延遲。(圖片來源:DigiKey)

在圖 3 中,ΔƩ 轉換器將每個轉換結果的多個樣本進行平均。ΔƩ 的平均濾波器通常是 FIR 或 IIR 數位濾波器。此多重取樣平均作業會增加整體轉換時間。但是,由於允許高解析度,因此會產生吞吐時間/準確度依存性。

SAR 轉換器的轉換時間包括輸入訊號擷取時間和轉換時間。擷取時間可讓輸入訊號在實際發生訊號擷取之前達到穩定。吞吐時間結合了內部電荷再分配和連續序列數據輸出訊號,並從 MSB 值開始。

使用管線式 ADC 時,使用者利用外部輸入時脈的正緣 (或負緣),來啟動取樣。針對此樣本擷取的電荷,則會進入第二階段,同時,轉換器會擷取等同其他輸入訊號的電荷,且第二階段會確認 MSB 值。在後續的外部時脈上,第二個擷取的訊號會進入第二階段,第一個訊號則進入第三階段。在此時脈週期內,則會確定第一個擷取訊號的 MSB-1 和第二個擷取訊號的 MSB。此過程將隨每個擷取的訊號繼續進行。當輸入訊號可完整重現數位輸出時,轉換器的輸出階段將同時重現輸入訊號。

憑藉此架構,管線式 ADC 能以幾 MSPS 至 1 GSPS 以上的取樣率而廣受歡迎。解析度範圍介於取樣率較快的 8 位元,到取樣率較慢的 16 位元。這些解析度和取樣率涵蓋多種應用,包括電荷耦合元件 (CCD) 成像、超音波醫療造影、數位接收器、基地台、數位預失真和數位影片。其中某些應用強調精確性和速度。

精密管線式 ADC

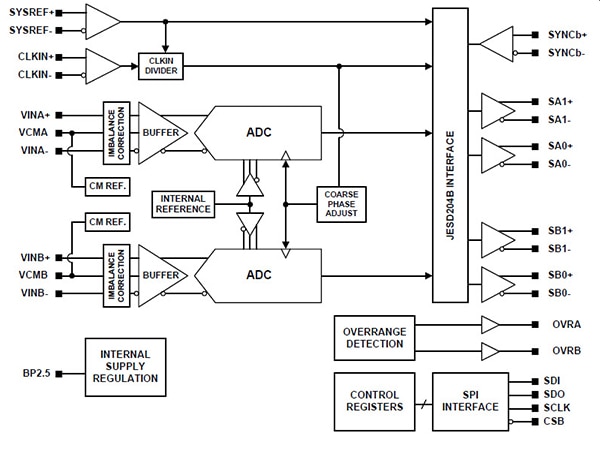

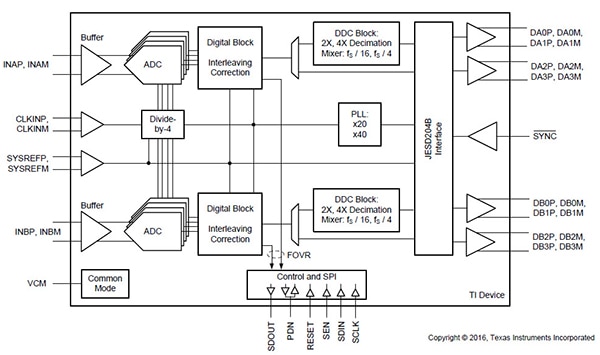

Texas Instruments 的 ADC16DX370 是精密管線式 ADC 的良好範例之一。這 16 位元、370 MSPS 的雙通道管線式 ADC,搭配一個後端式 7.4 Gbit/s JESD204B 介面。ADC16DX370 具有 150 MHz 輸入訊號,其訊噪比 (SNR)、無雜散動態範圍 (SFDR) 和雜訊頻譜密度 (NSD) 分別為 69.6 dBFS、88 dBFS 和 -152.3 dBFS/Hz。

每個 ADC 都有一個輸入緩衝器和一個不平衡校正電路,並有必要的參考電壓及內部驅動器。整合式輸入緩衝器可消除內部切換式取樣電容的電荷和電荷反沖雜訊。此緩衝器能緩解驅動放大器、抗交疊濾波器和阻抗匹配的要求 (圖 4)。

圖 4:高效能 370 MSPS ADC16DX370 是具有內部參考的雙管線式 ADC。此元件會將類比訊號轉換為 16 位元數位字組。(圖片來源:Texas Instruments)

圖 4:高效能 370 MSPS ADC16DX370 是具有內部參考的雙管線式 ADC。此元件會將類比訊號轉換為 16 位元數位字組。(圖片來源:Texas Instruments)

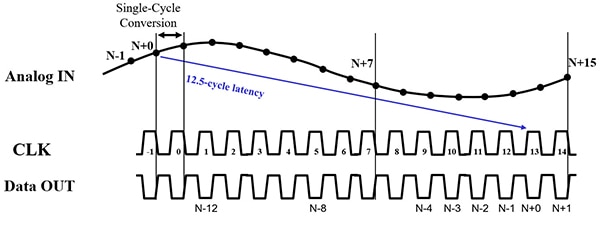

ADC16DX370 使用低雜訊接收器和時脈分頻器,從 CLKIN 輸入取得取樣時脈。輸入時脈分頻器會在整個系統中分配高頻時脈訊號,並在 ADC 元件局部向下分頻,以避免將共用中頻 (IF) 的訊號耦合到系統的其他部分。ADC 的核心延遲為 12.5 個時脈週期 (圖 5)。

圖 5:時序圖顯示 ADC 核心延遲為 12.5 個時脈週期。(圖片來源:DigiKey)

圖 5:時序圖顯示 ADC 核心延遲為 12.5 個時脈週期。(圖片來源:DigiKey)

取樣發生於 (CLKIN+) − (CLKIN -) 差動訊號的正緣。數位輸出碼作為最小核心值,在數據延遲 12.5 個時脈週期後才能使用。CLKIN 輸入頻率分頻器係數為 1、2、4 或 8。

ADC16DX370 具有差動時脈輸入引腳。每個引腳使用 50 Ω 電阻器在內部端接到 DC,讓總內部差動端接達到 100 Ω。時脈輸入引腳需要進行外部 AC 耦合。

雙管線式 ADC 電路板設計是達到完整效能的關鍵要素。為了適當地將所有訊號佈線到元件內外,需要至少六層。訊號路由層鄰近實心接地面,以便控制訊號返回路徑,將迴路區域最小化,而且微帶和帶狀線需要謹慎佈線,以便控制阻抗。可使用電源面和相鄰的實心接地面來控制供電返回路徑。此外,若可將供電面和接地面的間距縮小,就可增加分散式解耦及提高效能。

ADC16DX370 的目標應用包括:高 IF 取樣接收器、多載波基地台接收器,以及多模式與多頻帶接收器,可補足更高解析度和 370 MSPS 轉換速度。這款 16 位元管線式 ADC 還提供需要的 SNR (69.6 dBFS) 效能,例如可從 RF 外差接收器子系統的背景雜訊中識別出微小訊號。

為了協助設計人員評估 ADC16DX370,ADC16DX370EVM 評估板和相關的 High-Speed Data Converter (HSDC) Pro 軟體均支援此 ADC。EVM 附有一條 mini-USB 纜線,可連接到 PC。此外,TI 也提供 TSW16DX370EVM 公版設計板,可用來評估可用頻寬超過 100 MHz 的接收器 IF 子系統解決方案。

高速管線式 ADC

如果優先考量高速和寬動態範圍,設計人員可改用 Texas Instruments 的 ADS54J20,這是一款 12 位元的雙通道 1 GSPS ADC。在設計上,此 ADC 可提供 67.8 dBFS 的高 SNR,背景雜訊為 -157 dBFS/Hz。此 ADC 非常適合用於需要在寬廣瞬時頻寬上達到最高動態範圍的應用 (圖 6)。

圖 6:ADS54J20 雙管線式 ADC 提供交錯校正,可達到 -157 dBFS/Hz 的背景雜訊和降頻取樣數位濾波選項。(圖片來源:Texas Instruments)

圖 6:ADS54J20 雙管線式 ADC 提供交錯校正,可達到 -157 dBFS/Hz 的背景雜訊和降頻取樣數位濾波選項。(圖片來源:Texas Instruments)

圖 6 中使用 ADS54J20 的交錯和顫動演算法,達到高 SFDR 的乾淨頻譜。對於需要在廣大頻率範圍內達到更高 SNR 和 SFDR 的系統,該元件還具有多種可編程的降頻取樣濾波選項。

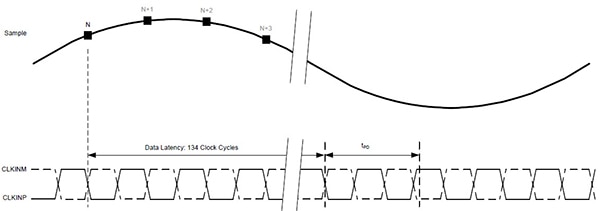

帶通降頻取樣濾波器具有一個數位混頻器和三個 FIR 級聯濾波器,可產生大約 134 個輸出時脈週期的延遲,加上一個邏輯閘和 4 ns 的輸出緩衝傳播延遲 (圖 7)。

圖 7:時序圖顯示 ADC 延遲為 134 個時脈週期,加上邏輯閘和輸出緩衝傳播延遲 (tPD)。(圖片來源:Texas Instruments)

圖 7:時序圖顯示 ADC 延遲為 134 個時脈週期,加上邏輯閘和輸出緩衝傳播延遲 (tPD)。(圖片來源:Texas Instruments)

數位區塊、交錯引擎及降頻取樣濾波器 (再次參見圖 6),與高速取樣 1 GHz 時脈頻率,都會造成轉換器延遲。

ADS54J20 的一些目標應用包括:雷達和天線陣列、寬頻無線和纜線數據機端接系統 (CMTS) 和 DOCSIS 3.1 接收器。

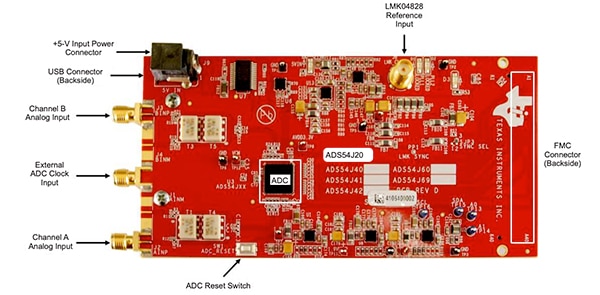

也有評估板可支援 ADS54J20,在本篇中為 ADS54J20EVM (圖 8)。

圖 8:ADS54J20EVM 評估板隨附 mini USB 纜線和電源線,可支援 ADS54J20 高速 ADC。(圖片來源:Texas Instruments)。

圖 8:ADS54J20EVM 評估板隨附 mini USB 纜線和電源線,可支援 ADS54J20 高速 ADC。(圖片來源:Texas Instruments)。

ADS54J20EVM 也能配合 HSDC Pro 軟體使用,並隨附用於連接 PC 的 mini USB 纜線,以及電源線。

結論

雖然 SAR ADC 和 ΔƩ ADC 各佔有一席之地,但管線式 ADC 才是克服超高速 ADC 挑戰的解決之道。管線式 ADC 能在處理多個樣本的同時,仍以數百 KSPS 至 GSPS 的速度將數據傳送到輸出。然而,並非所有管線式 ADC 都只強調速度。如本文所述,也能達到更高的精確度。

無論強調何者,管線式 ADC 都非常適合用於高速行動基地台、超高速多載波行動基礎架構基地台、電信、數位預失真觀察、回程接收器,以及其他許多需要高速轉換的應用。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。