類比基本知識 - 第 5 篇:克服 SAR ADC 的輸入驅動難題

資料提供者:DigiKey 北美編輯群

2020-10-28

編者註:類比數位轉換器 (ADC) 可將類比世界連接至數位世界,因此對任何連接至真實世界的電子系統來說是基礎元件之一。此元件也是系統效能的重要決定因素。本系列文章將探討 ADC 的基礎知識、各種類型及其應用。本系列類比基礎知識的第 1 篇探討 SAR ADC。第 2 篇探討三角積分轉換器。第 3 篇探討管線式 ADC。第 4 篇說明三角積分 ADC 如何產生超低雜訊的結果。本文屬於第 5 篇,會探討 SAR ADC 的輸入驅動難題。

許多數據採集、工業控制以及儀表應用都需要超高速的類比數位轉換器 (ADC),其中又以連續漸近暫存器 (SAR) 轉換器最為合適。但是,必須確保 SAR 轉換器周圍的外部電路也有能力可確保轉換成功。SAR 轉換器上需要特別注意的關鍵端子是類比訊號輸入。如果無人看管,這些輸入引腳會有穩定性問題以及電容式電荷「回衝」,可能會導致轉換不準確和訊號採集時間延長。

要讓 SAR 轉換器應用達到精密的輸入訊號控制,解決方案在於運算放大器的驅動。這些元件由適當的輸出電阻和電容值支援,是高度精密且完備的解決方案,可達到高解析度的 16 位元和 20 位元 SAR 轉換器系統。

本文將簡要探討要達到穩定和準確的 SAR ADC 轉換會遭遇的相關難題。接著會介紹適合驅動 SAR ADC 的運算放大器,並說明如何實作必要的輸入驅動器電路。本文將以 Analog Devices 的解決方案舉例說明。

SAR ADC 輸入電路

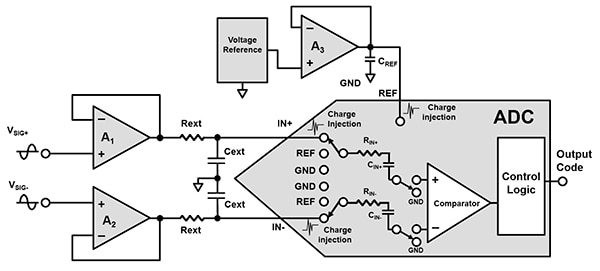

SAR ADC 驅動器電路具有運算放大器 (A1 和 A2),可將 ADC 及其訊號源分隔。在此電路中,Rext 會將放大器的輸出級與 ADC 的電容式負載 (CIN+ 與 CIN-) 及 Cext 「隔離」,藉此達到穩定。Cext 和 CREF 提供近乎完美的輸入源給 ADC,再由 ADC 吸收 IN+、IN- 和 REF 輸入端子的切換式電荷注入。輸入端子 (IN+、IN-) 會在轉換器採集期間追蹤輸入訊號 (VSIG+、VSIG-) 的電壓,提供電荷給 ADC 的輸入採樣電容 CIN+ 和 CIN-。

圖 1:在此電路中,Rext 會將運算放大器輸出級的 Cext「隔離」。Cext 和 CREF 在取樣期間可提供電荷儲備給差動 SAR ADC。(圖片來源:DigiKey)

圖 1:在此電路中,Rext 會將運算放大器輸出級的 Cext「隔離」。Cext 和 CREF 在取樣期間可提供電荷儲備給差動 SAR ADC。(圖片來源:DigiKey)

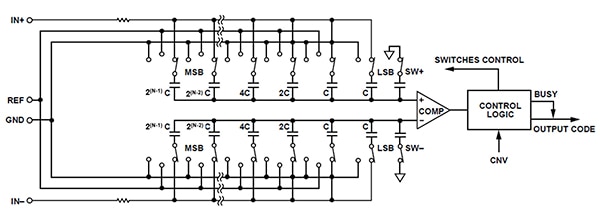

在此使用 Analog Devices 的 AD7915 (16位元) 和 AD4021 (20 位元) SAR ADC 為例,可以看到 ADC 內部使用電荷重分配數位類比轉換器 (DAC)。電容式 DAC 具有兩個相同的二進位加權電容陣列。這些陣列會連接到非逆變和逆變型比較器輸入 (圖 2)。

圖 2:簡化的 AD7915 和 AD4021 架構 SAR ADC 線路圖,其中 N 等於轉換器的位元數。(圖片來源:DigiKey 以 Analog Devices 的原始素材進行修改)

圖 2:簡化的 AD7915 和 AD4021 架構 SAR ADC 線路圖,其中 N 等於轉換器的位元數。(圖片來源:DigiKey 以 Analog Devices 的原始素材進行修改)

在採集階段,輸入 (IN+ 和 IN-) 會切換到電容陣列。此外,SW+ 和 SW+ 會關閉,將最低有效位元 (LSB) 電容與接地 (GND) 捆綁在一起。在此狀態下,電容陣列會變成採樣電容,採集 IN+ 和 IN+ 的類比訊號。採集階段完成後,CNV 輸入對控制邏輯 (右側) 會升高,以啟動轉換階段。

轉換階段開始會先開啟 SW+ 和 SW-,然後將兩個電容陣列切換到 GND。在此配置中,擷取的 IN+ 和 IN 差動電壓會導致比較器變不平衡。電荷重分配 DAC 會有條理地切換電容陣列的各個要素,從最高有效位元 (MSB) 到 LSB,介於 GND 和 REF 之間。 比較器的輸入會隨著二進位加權電壓步進 (VREF/2N-1、VREF/2N-2 …VREF/4、VREF/2) 而有所不同。控制邏輯會負責將 MSB 切換成 LSB,讓比較器返回平衡狀態。完成此過程後,ADC 會重返採集階段,控制邏輯會產生 ADC 輸出碼。

AD7915 ADC 的輸入電荷注入、電路穩定性和驅動

轉換過程有個關鍵部分就是擷取準確的輸入訊號電壓。若驅動放大器有準確為輸入電容、CIN+和 CIN- 充電,同時在 ADC 採集時間內全程維持穩定性,ADC 數據轉換過程就可順利進行。對設計人員來說,問題在於 ADC 的輸入端子會引入電容量 (CIN+、CIN-),以及切換雜訊或「回衝」電荷注入,因此驅動放大器必須進行管理。

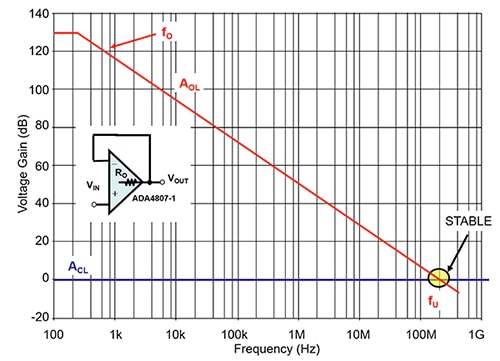

放大器電路波德圖可快速估計電路的穩定性。波德圖工具可估算放大器開迴路的大小以及系統必迴路增益轉移函數。

圖 3:圖 1 放大器的開迴路和閉迴路轉移函數,如放大器負載和後續的 SAR ADC 一樣,無 Rext 和 Cext。(圖片來源:DigiKey)

圖 3:圖 1 放大器的開迴路和閉迴路轉移函數,如放大器負載和後續的 SAR ADC 一樣,無 Rext 和 Cext。(圖片來源:DigiKey)

Y 軸可量化放大器的開迴路增益 (AOL) 與閉迴路增益 (ACL),而放大器的 AOL 曲線從 130 分貝 (dB) 開始,而閉迴路、ACL 等於 0 dB。X 軸沿線的單位能以演算法量化開迴路和閉迴路的增益頻率,從 100 Hz 到 1 GHz。

在圖 3,放大器的DC 開迴路增益約為 220 Hz (fO),以 -20 dB/dec 的速率從 130 dB 逐漸向下。隨著頻率增加,這個衰減速率會在大約 180 MHz 時持續有效並通過 0 dB。由於此曲線表示單極系統,因此交越頻率 fU 等於單位增益穩定放大器的增益頻寬乘積 (GBWP)。此圖表示穩定的系統,因為 AOL 和 ACL 閉合率為 20 dB/dec。

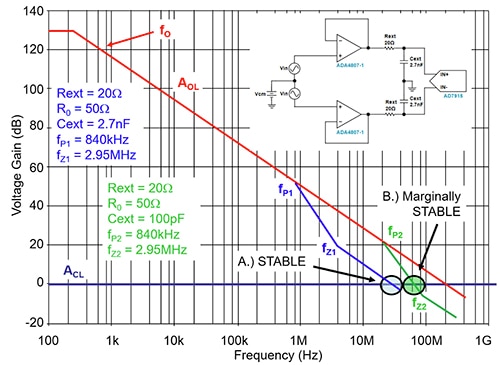

添加 Rext 和 Cext 以及 SAR ADC,會產生系統零點與極點,因此需修改放大器電路 (圖 4)。此系統包括一個 16 位元、1 MSPS 的 AD7915 差動 PulSAR ADC 以及一個 180 MHz、軌對軌輸入/輸出 ADA4807-1 放大器,兩者皆來自 ADI。放大器和 ADC 的組合需要 Rext,因為具有 30 pF (典型值) 的 ADC 輸入電容量負載。此電路還要求 Cext 當作電荷儲備桶,以在 ADC 輸入提供足夠的電荷,以便準確匹配輸入電壓。

圖 4:在此顯示兩個 ADA4807 運算放大器在驅動 AD7915 SAR ADC,並搭配兩個單獨的 Rext/Cext 對時的波德圖響應。fP1 和 fZ1 角頻率可修改放大器的開迴路增益,進而達到穩定的系統響應。fP2 和 fZ2 角頻率可修改放大器的開迴路增益,進而達到稍微穩定的響應。(圖片來源:DigiKey)

圖 4:在此顯示兩個 ADA4807 運算放大器在驅動 AD7915 SAR ADC,並搭配兩個單獨的 Rext/Cext 對時的波德圖響應。fP1 和 fZ1 角頻率可修改放大器的開迴路增益,進而達到穩定的系統響應。fP2 和 fZ2 角頻率可修改放大器的開迴路增益,進而達到稍微穩定的響應。(圖片來源:DigiKey)

圖 4 中的電路可能會因為 ADC 的電容負載,以及初次採集時 ADC 的切換電荷注入而發生振盪。Rext/Cext 放大器輸出元件所產生的額外極點和零點可確保系統穩定,因此開迴路和閉迴路增益曲線的交叉會大於 20 dB/dec,導致相位邊限小於 45°。此配置搭配 fP2 和 fZ2 就會產生不穩定的電路。

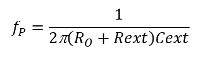

為了防止不穩定性,評估放大器的開迴路增益曲線,且電路中有 Rext 和 Cext 時,設計人員需要將放大器的開迴路輸出電阻值 RO 的影響納入考量。RO 相加後等於 50 ohm (W) Rext,而 Cext 會引進一個極點 (fp 如方程式 1)與一個零點 (fZ 如方程式 2),因此會修改開迴路響應曲線。RO、Rext 和 Cext 的值會決定 fP 的角頻率。Rext 和 Cext 的值會確定零角頻率 fZ。

方程式 1

方程式 1

方程式 2

方程式 2

fP 與 fZ 的計算:

fP1 = 842 kHz

fZ1 = 2.95 MHz

搭配: RO = 50 W

Rext = 20 W

Cext = 2.7 nF

fP2 = 22.7 MHz

fZ2 = 79.5 MHz

搭配: RO = 50 W

Rext = 20 W

Cext = 0.1 nF

fP1 和 fZ1 的上述值能讓 AD7915 和 ADA4807-1 達到穩定的系統。

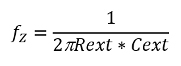

驅動 Easy Drive AD4021 SAR ADC

AD7915 的替代品是 AD4021 20 位元 1 MSPS Easy Drive SAR 轉換器。AD4021 元件系列可大幅降低輸入回衝與輸入電流至 0.5 μA/MSPS。Easy Drive 可降低功耗與訊號鏈的複雜性。

AD4021 的類比輸入有電路可降低典型切換式電容 SAR 輸入非線性電荷回衝。降低回衝並延長採集階段,因此能使用更低的頻寬與更低功率的驅動器放大器 (圖 5)。

圖 5:AD4021 的輸入電路和採集時間可降低回衝切換電流,並可減輕驅動器放大器的嚴格要求。(圖片來源:Analog Devices)

圖 5:AD4021 的輸入電路和採集時間可降低回衝切換電流,並可減輕驅動器放大器的嚴格要求。(圖片來源:Analog Devices)

在回衝減少以及採集時間延長的加成下,亦可在輸入電阻電容 (RC) 濾波器中使用更大的 Rext 電阻值,以及對應的較小 Cext 電容。搭配較小的 Cext 放大器負載可提升穩定性並降低功耗。

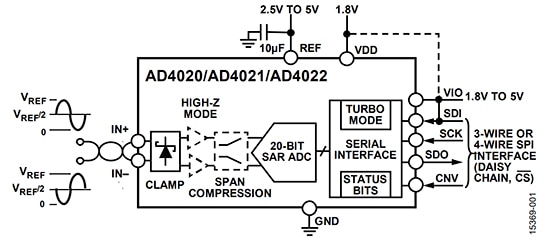

使用單一 5 V 電源的 AD4021 其建議的連接圖似乎有類似的電路圖。但是,放大器的要求則有放寬,Rext/Cext (R 和 C) 值較小 (圖 6)。

圖 6:AD4021 和 ADA4807-1 典型應用圖採用單一 5 V 電源供電,與上述 AD7915 的驅動相比,放大器的要求更為放寬,並採用更大的 Rext 值。(圖片來源:Analog Devices)

圖 6:AD4021 和 ADA4807-1 典型應用圖採用單一 5 V 電源供電,與上述 AD7915 的驅動相比,放大器的要求更為放寬,並採用更大的 Rext 值。(圖片來源:Analog Devices)

在圖 6 中,SAR 架構的 AD4021 亦使用電荷重分配採樣 DAC。ADC 具有板載轉換時脈和序列時脈。因此,轉換過程不需要同步時脈 (SCK) 輸入。此時脈配置允許延長採集時間,以更多的時間讓輸入訊號趨穩到最終值,進而改善準確度。

AD7915 和 AD4021 驅動放大器的主要考量是雜訊,因為對 AD7915 而言,放大器/Rext/Cext 的組合必須從全量程步進趨穩到 16 位元位準 (0.0015%、15 ppm),而 AD4021 則要趨穩到 20 位元位準 (0.00001%、1 ppm)。

為了維持 AD7915 和 AD4021 的訊噪比 (SNR) 效能,驅動器放大器的雜訊必須小於 ADC 雜訊的三分之一。AD4021 的雜訊為 60 mVrms,因此放大器/Rext/Cext 的組合要小於 20 mVrms。AD4021 的雜訊為 31.5 mVrms,因此放大器/Rext/Cext 的組合要小於 10.5 mVrms。

Analog Devices 的精密 ADC 驅動器工具有助於設計人員快速計算正確的 Rext 與 Cext 值。透過精選的驅動器和 ADC,此工具能針對電路的趨穩時間、雜訊和失真行為建立模型。

結論

SAR ADC 繼續在超高速數據採集、工業控制和儀器儀錶應用領域主導趨勢。但是,這些元件 (驅動放大器與輸入濾波器) 的外部輸入電路,需要特別的考量才能適應潛在的切換電荷注入和放大器穩定性問題。

大多數 SAR 轉換器 (如 AD7916 和 AD4021) 要達到精密的輸入訊號控制,解決方案放是使用運算放大器驅動器,在此例中即為 ADA4807-1。如本文所示,這些元件由適當的輸出電阻和電容值支援,能以此強大基礎打造高度精密、完備、高解析度的 16 位元或 20 位元 SAR 轉換器系統。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。