類比基礎知識 – 第 1 篇:SAR 類比數位轉換器

資料提供者:DigiKey 北美編輯群

2020-04-15

編者說明:類比數位轉換器 (ADC) 可將類比世界連接至數位世界,因此對任何連接至真實世界的電子系統都很重要。此元件也是系統效能的重要決定因素。本系列文章將探討 ADC 的基礎知識、各種類型及其應用。本文為系列文章的第 1 篇,著重於類比的基礎知識,將會討論連續漸近暫存器 (SAR) ADC。第 2 篇則討論三角積分 (ΔƩ) 轉換器。

由於感測的資訊仍屬於類比世界,要想讓其進入數位域,必須進行某種轉換。這項重要工作主要由類比數位轉換器 (ADC) 來處理。多年來,三個成功受到關注的 ADC 拓撲分別為連續漸近暫存器 (SAR)、三角積分 (S-D) 和管線式 ADC。這三個 ADC 拓撲具有很大的差異,可以不同的頻率範圍工作,以滿足各種應用的需求,包括從低頻率感測器應用一直到更高頻率的 LiDAR 或衛星通訊應用等等。

SAR ADC 是第一個成為主流的轉換器。隨著時間的推移,此轉換器拓撲漸漸用於各種應用中,包括流程控制、醫療以及早期的數位音訊系統。SAR ADC 的輸出轉換範圍為 8 位元至 20 位元,這為上述應用提供很大的助益。但 SAR ADC 出名的原因在於,此 ADC 可捕捉類比輸入訊號的快照,並利用多個訊號快照繪製一段時間內的圖像。

本文將簡要介紹與 SAR ADC 息息相關的訊號鏈。隨後會深入探究 SAR ADC 拓撲,並分析負責 ADC 快照動作的基本輸入級。然後,本文將介紹 SAR ADC 範例解決方案,即 Analog Devices 的 AD7625BCPZ 和 AD4020BCPZ-RL7,重點探討 ADC4020BCPZ-RL7 的內部類比對數位轉換技術。此外,還提供相關數據採集系統的重要規格。

SAR ADC 的類比訊號鏈

SAR ADC 應用於自動測試設備、機器自動化、醫療設備及高精密數據採集等系統中。所有的 SAR ADC 應用都有類比訊號需要以數位形式來表示,解析度需達到適度的 8 至 20 位元,而採樣速度則需從近乎 DC 至 15 MSPS (本文撰寫時)。

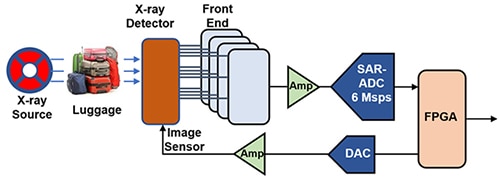

SAR ADC 無需類比前端 (AFE) 訊號鏈即可運作。但如果設計人員還需要在 SAR ADC 的前端成功提供訊號,則很有可能需要進行一定程度的訊號調整 (圖 1)。

圖 1:此 SAR ADC 訊號鏈範例含有 X 光偵測器、AFE、放大器驅動器、Analog Device 的 AD7625BCPZ 6 MSPS 轉換器,以及用於取得轉換結果的數位容器 (FPGA)。(圖片來源:DigiKey)

圖 1:此 SAR ADC 訊號鏈範例含有 X 光偵測器、AFE、放大器驅動器、Analog Device 的 AD7625BCPZ 6 MSPS 轉換器,以及用於取得轉換結果的數位容器 (FPGA)。(圖片來源:DigiKey)

上圖中,X 光光源傳送的訊號經行李箱後進入 X 光偵測器。該 X 光裝置的任務是在短時間內建構行李箱的完整影像,以減少旅客的不滿。

前端取得偵測器訊號後會執行訊號調整功能,例如類比增益和位準移位等。之後會將訊號提供至 SAR ADC;此例為 Analog Devices 的 AD7625BCPZ。

SAR ADC 前面的放大器可提供相應的穩定性,放大器和 SAR ADC 之間通常會設有一個一階低通濾波器。SAR ADC 能以高達 6 MSPS (即每 167 ns 採樣一次) 的速度採樣,可在短時間內接受多張快照。

SAR ADC 輸入級的核心變得更簡化

SAR ADC 已經過多次增強與改進,但在任何情況下,轉換期間主要的活動都是進行電荷再分配,這是連續漸近 ADC 最常見的實作之一。此外,使用 SAR ADC 還多了一項好處,就是零延遲,這和三角積分及管線式轉換器有所不同。

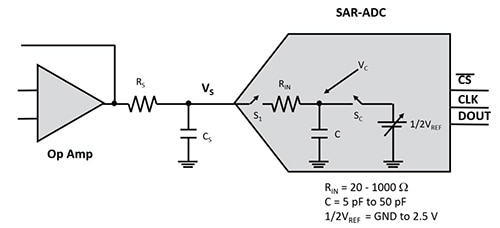

在最簡單的層級,很容易看到訊號快照發生的位置。SAR ADC 輸入核心包含輸入訊號擷取開關 (S1)、電容陣列、轉換開關 (SC) 和內部參考電壓 (½ VREF) (圖 2)。

圖 2:運算放大器搭配輸出穩定濾波器來驅動 SAR ADC。(圖片來源:DigiKey)

圖 2:運算放大器搭配輸出穩定濾波器來驅動 SAR ADC。(圖片來源:DigiKey)

SAR ADC 核心的運作如下:

- S1 開,SC 關:輸入級會從類比訊號源斷開。

- C 上的電荷以 ½ VREF 重新校正。重新校正後,SAR ADC 會歸零。

- 然後 S1 關,SC 開:現在,元件連接至輸入類比訊號。

- SAR ADC 在預定的擷取時間內取得輸入訊號 VS。這段擷取時間會產生 S1和 SC 切換雜訊,並讓放大器突然接觸電容負載和切換雜訊。

- 然後 S1 開:此時即會發生訊號快照。

- SAR ADC 將 VC 的訊號轉換為數位形式。執行此動作所花的時間稱為「轉換時間」。

SAR ADC 輸入級的核心細節

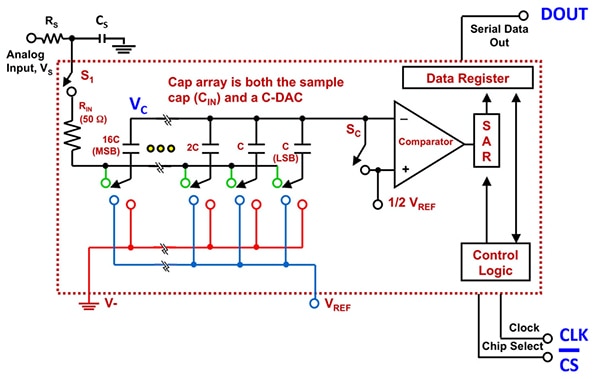

轉換核心會對捕捉的 VC 訊號進行電荷再分配。核心會在時脈的閘控下協調轉換器的電荷再分配。在此過程中,每個時脈控制的數位輸出程式碼會送至 SAR ADC 的 DOUT 輸出 (圖 3)。

圖 3:4 位元 SAR ADC 光幕具有一系列經過數位加權的電容:16C、8C、4C、2C 和兩個 C。(圖片來源:DigiKey)

圖 3:4 位元 SAR ADC 光幕具有一系列經過數位加權的電容:16C、8C、4C、2C 和兩個 C。(圖片來源:DigiKey)

轉換期間,SAR ADC 演算法會首先確定最高有效位元 (MSB)。SAR ADC 會在 V- 和 VREF 比較器輸入之間切換 16C 電容的底部,藉此測試相較於 ½ VREF 的訊號強度。在 SAR ADC 轉換線路中,下一個比較是針對 ½ VREF 測試 8C (未顯示),然後測試 4C,以此類推。

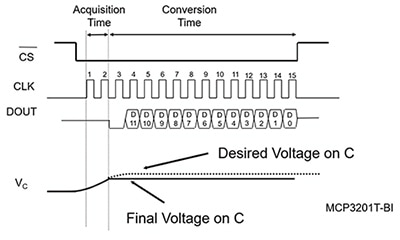

SAR ADC 輸出轉換細節

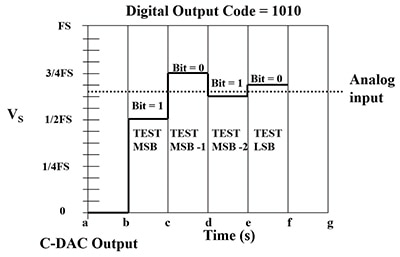

確定的 MSB 會立即透過 DOUT 引腳進行傳輸,而 MSB 開關會在確定 MSB 1 期間一直保持凍結。SAR ADC 將執行此演算法,直至最終選定最低有效位元 (LSB) (圖 4)。

圖 4:4 位元的 SAR ADC 透過確定的位元來控制轉換演算法的時脈,並透過 DOUT 引腳傳輸這些位元 (如圖 3 所示)。(圖片來源:DigiKey)

圖 4:4 位元的 SAR ADC 透過確定的位元來控制轉換演算法的時脈,並透過 DOUT 引腳傳輸這些位元 (如圖 3 所示)。(圖片來源:DigiKey)

在圖 4 中,SAR ADC 按照 MSB 到 LSB 的順序確定經時脈控制的位元。所有轉換資料會在時脈的控制下不斷透過圖 3 右上方的 DOUT 即時輸出。完整的傳輸週期通常需要足夠的時間來擷取訊號,而每個位元需要一個時脈週期。

SAR ADC 轉換挑戰

設計人員必須清楚需要多長的訊號趨穩時間,才能確保從轉換中擷取正確的類比值 (圖 5)。

圖 5:12 位元 SAR DAC 的轉換時序示意圖。每個完整的轉換,都需要 16 個時脈。(圖片來源:DigiKey)

圖 5:12 位元 SAR DAC 的轉換時序示意圖。每個完整的轉換,都需要 16 個時脈。(圖片來源:DigiKey)

在圖 5 中,輸入訊號 VC 在轉換器的輸入開關開啟之前,尚未達到最終所需的電壓。在此例中,電路設計人員算錯了放大器輸入訊號的趨穩時間。

AD4020BCPZ-RL7 20 位元 1.8 MSPS SAR ADC 在擴展擷取相位的同時,仍保持同樣的傳輸率,從而降低了訊號擷取的複雜度。其訊噪比 (SNR) 很低,只有 100.5 dB。

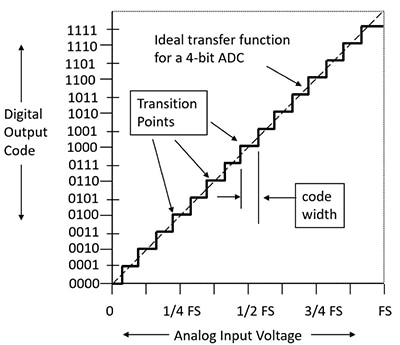

SAR ADC 傳遞函數

ADC 的潛在程式碼數量等於 2N,其中 N 代表位元數。例如,4 位元轉換器將有 24,即 16 個不同的程式碼 (圖 6)。

圖 6:理想 4 位元 SAR ADC 的傳遞函數 (即數位輸出程式碼與類比輸入電壓的關係圖) 應為一條直線。(圖片來源:DigiKey)

圖 6:理想 4 位元 SAR ADC 的傳遞函數 (即數位輸出程式碼與類比輸入電壓的關係圖) 應為一條直線。(圖片來源:DigiKey)

繪製圖片

SAR ADC 的傳輸率包含擷取時間和轉換時間,以讓 Analog Devices 的 AD4020BCPZ-RL7 在 20 位元解析度下達到高達 1.8 MSPS 的傳輸率。在 AD4020BCPZ-RL7 的傳輸速度下,將可取得多張快照並為機器自動化和醫療設備建立數位圖片渲染解決方案。

結論

SAR ADC 可用於各種應用,如流程控制、醫療及消費性應用等,其以強大的訊號快照能力以及穩步提高的解析度和速度不斷證明自身的價值。目前,SAR ADC 的解析度為 8 至 20 位元,傳輸速度則高達 15 MSPS。Analog Devices 的 AD4020BCPZ-RL 就是其中的典範。其雜訊低、速度快,是一款 20 位元、1.8 MSPS 的精密元件。不過,SAR ADC 轉換器的體系仍在發展。未來還會有更多產品問世。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。