類比基礎知識 — 第 2 篇:三角積分 (ΔΣ) ADC 與其數位能力的運用方式

資料提供者:DigiKey 北美編輯群

2020-05-14

編者說明:類比數位轉換器 (ADC) 可將類比世界連接至數位世界,因此對任何連接至真實世界的電子系統來說是基礎元件之一。此元件也是系統效能的重要決定因素。本系列文章將探討 ADC 的基礎知識、各種類型及其應用。此類比基礎知識系列文章的第 1 篇探討 SAR ADC。本文為第 2 篇,探討三角積分 (ΔƩ) 轉換器。第 3 篇探討管線式 ADC。第 4 篇說明三角積分 ADC 如何產生超低雜訊的結果。第 5 篇探討 SAR ADC 的輸入驅動難題。

誠如第 1 篇探討的連續漸近暫存器 (SAR) 類比數位轉換器 (ADC),類比感測器訊號鏈面臨著高精確度難題:多項增益、訊號調整、複雜的類比濾波級,全部都由 SAR ADC 負責,因此可能會導致類比錯誤。設計人員最終也可能會取得昂貴且密集組裝的 PC 板解決方案。

此外,從超低感測器訊號開始,訊號鏈的每個類比級輸出都會導致誤差,進而在轉換器的數位輸出端產生低訊噪比 (SNR) 和高失真誤差。此類系統的設計人員需要後退一步,重新思考高精確度感測器 ADC 解決方案。

若要解決高精確度感測器系統的相關問題,可選用一種 ADC 拓撲,迅速將微小感測器訊號數位化,並以數位形式實作增益和濾波等雜訊類比功能。這就是三角積分 (ΔƩ) ADC 發揮功用之處。

本文以 Analog Devices 的 AD4110-1 通用輸入類比數位前端為例,簡要探討 ΔƩ ADC 的基本功能和內部的類比數位轉換機制。接著會帶您深入瞭解周圍的訊號鏈,並為合適的數據採集系統提供重要規格。

ΔƩ ADC 的結構

ΔƩ ADC 就在世紀交替之際,搶走了類比技術的光環。在 ΔƩ 先進技術廣泛採用下,主要的類比訊號和運算處理開始駐留在數位域。檢視 ΔƩ ADC 積體電路 (IC) 後發現,有超過 80% 的矽空間都用來執行數位功能。主導地位的數位電路產生的附加效益是耐用性和小型覆蓋區。

到底是為什麼?這起因於低電壓類比訊號的直接數位化。一旦進入數位域,數位電路幾乎可以完全取代類比濾波,同時還能夠執行任何所需的增益功能 (圖 1)。數位電路也隨著每個半導體製程節點而縮小。

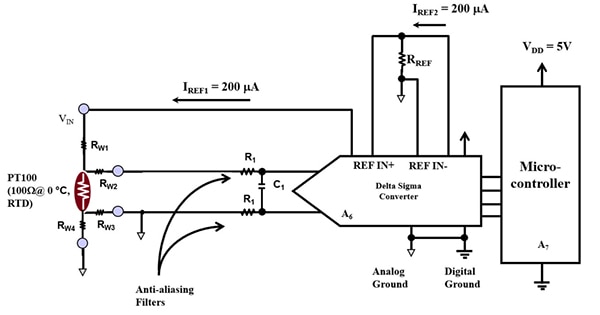

圖 1:一個 ΔƩ 幾乎就含有濾波和增益用的所有必要電路。在此範例中,ΔƩ ADC 會對小型電阻溫度偵測器 (RTD) 電壓進行感測與數位化。接著使用內建數位訊號增益和濾波來產生低雜訊的 24 位元數位結果。(圖片來源:A Baker’s Dozen)

圖 1:一個 ΔƩ 幾乎就含有濾波和增益用的所有必要電路。在此範例中,ΔƩ ADC 會對小型電阻溫度偵測器 (RTD) 電壓進行感測與數位化。接著使用內建數位訊號增益和濾波來產生低雜訊的 24 位元數位結果。(圖片來源:A Baker’s Dozen)

圖 1 所示的 24 位元 ΔƩ ADC 系統由一個類比輸入、一個中央數位引擎和一個數位 I/O 端子組成。轉換器取得低電壓 RTD 訊號,然後透過數位濾波,以完整 24 位元數位化形式呈現類比輸入。在此並沒有 SAR ADC 常用的類比增益區塊,且唯一的類比濾波器是由 R1 和 C1 組成。沒錯,這就是個簡易且成本低廉的一階濾波器!

ΔƩ ADC 的運作方式

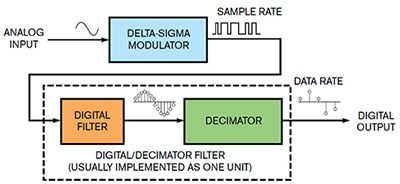

ΔƩ ADC 的基本拓撲具有一個 ΔƩ 調變器,並且與數位濾波器串聯。除了此基本拓撲外,大多數 ΔƩ ADC 還具有其他眾多功能。然而,所有的 ΔƩ 轉換器都具備此基本核心 (圖 2)。

圖 2:從基本結構來看,每個 ΔƩ ADC 均有 ΔƩ 調變器、數位濾波器和降頻器。(圖片來源:EDN)

圖 2:從基本結構來看,每個 ΔƩ ADC 均有 ΔƩ 調變器、數位濾波器和降頻器。(圖片來源:EDN)

在圖 2 中,輸入可以是正弦波或 DC;本篇將著重探討正弦波輸入。ΔƩ 調變器將單一週期正弦波數位化成 1 位元流。ΔƩ 調變器輸出取樣頻率為 Fs。雖然 1 位元調變器轉換似乎會產生高量化雜訊,但訊號雜訊實際上被「塑形」成更高的頻率。這有助於在數位濾波器的輸出端進行低雜訊且高解析度的轉換。

在調變器的輸出端,數位濾波器會累加 ΔƩ 調變器的 1 位元結果並執行濾波器計算。數位濾波器輸出訊號會以數位形式反映類比輸入訊號,同時以 Fs 頻率持續輸出。此時,訊號將獨留在數位域中。數位低通濾波器 (或稱降頻取樣濾波器) 會減弱較高頻率的雜訊,並降低輸出數據傳輸率 1/Fd。數位/降頻取樣濾波器會對調變器的 1 位元編碼流進行取樣和濾波,使其成為速度較慢的多位元編碼。

儘管大多數轉換器只有一種取樣率,但 ΔƩ 轉換器卻有兩種:輸入取樣頻率 (Fs) 以及輸出數據頻率 (Fd)。根據方程式 1,這兩個頻率變數之間的比值會界定系統降頻取樣比 (DR):

![]() 方程式 1

方程式 1

ΔƩ 調變器

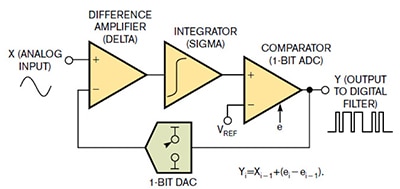

ΔƩ 調變器會產生 1 位元編碼流,藉此執行實際的類比數位轉換。此流程從差動放大器開始 (圖 3)。

圖 3:ΔƩ ADC 調變器輸入級會感測類比輸入和回授 DAC 之間的差值 (三角)。第二級會在類比訊號實作積分器功能 (或稱積分)。(圖片來源:EDN)

圖 3:ΔƩ ADC 調變器輸入級會感測類比輸入和回授 DAC 之間的差值 (三角)。第二級會在類比訊號實作積分器功能 (或稱積分)。(圖片來源:EDN)

在圖 3 中,差動放大器 (三角) 將類比訊號傳輸到積分器 (積分)。在積分器輸出端,比較器會以極高取樣率 (1/Fs) 區分積分器的輸出和參考電壓 (VREF)。此外,比較器會將 1 位元流傳輸到 1 位元數位類比轉換器 (DAC)。然後,調變器會測量類比輸入訊號和回授 DAC 的類比輸出之間的差值。

ΔƩ > 調變器會透過積分器和 DAC 回授迴路的作用,將雜訊塑形成更高的頻率。圖 3 中的公式 (右下方) 列出傳遞方程式:Yi = Xi-1 + (ei – ei-1)。調變器利用量化雜訊 (ei) 將輸入訊號 (Xi) 數位化成 1 位元輸出碼 (Yi)。具體而言,調變器的輸出 (Yi) 等於輸入 (Xi-1) 加上量化雜訊 (ei – ei-1)。由此公式可見,量化雜訊是目前誤差 (ei) 減去調變器先前誤差 (ei-1) 的差值。

數位和降頻取樣濾波器

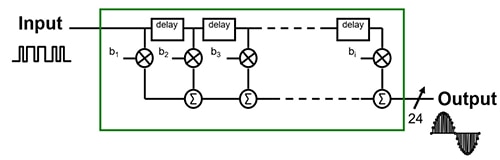

平均技術是低速工業 ΔƩ ADC 中常用的數位濾波形式。幾乎所有工業 ΔƩ ADC 均採用名為 sinc 濾波器的平均濾波器;此濾波器使用線性相位有限脈衝回應 (FIR),屬於一種數位低通濾波器 (圖 4)。

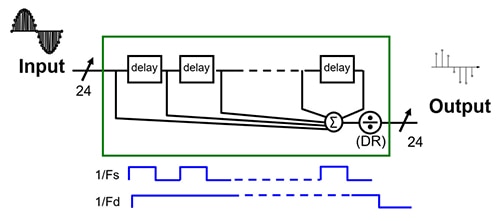

圖 4:此平均 FIR 數位濾波器的係數 (bx) 均等於 1。(圖片來源:DigiKey)

圖 4:此平均 FIR 數位濾波器的係數 (bx) 均等於 1。(圖片來源:DigiKey)

在圖 4 中,調變器輸出位元流是此數位濾波器的輸入,調變器的取樣時脈會決定延遲時間。圖 4 的 FIR 濾波器係數 (bx) 均等於 1。利用此平均值演算法,FIR 數位濾波器會以低雜訊、24 位元的數位形式呈現類比輸入,如圖 3 所示,並以調變器取樣率 (1/Fs) 進行取樣。接著,降頻取樣濾波器會按照 DR 降低輸出數據傳輸率。

根據文獻,「decimation」一詞指的是有條理地清除冗員士兵的軍事行動。在數位電子領域中,「decimation (降頻取樣)」承襲了相同概念,即按照 DR 降低數位訊號的輸出數據傳輸率 (1/Fd)。為達此目的,最快速且數位化的方式就是以系統化方法,捨棄數位濾波器的部分輸出取樣 (圖 5)。

圖 5:降頻取樣流程會將輸出數據傳輸率 (1/Fd,圖片底部) 除以取樣率 (1/Fs),藉此系統化地減少 24 位元數位輸出的數量。(圖片來源:DigiKey)

圖 5:降頻取樣流程會將輸出數據傳輸率 (1/Fd,圖片底部) 除以取樣率 (1/Fs),藉此系統化地減少 24 位元數位輸出的數量。(圖片來源:DigiKey)

根據方程式 1,圖 5 中的降頻取樣流程會按照 DR 降低輸出數據傳輸率 (1/Fd)。

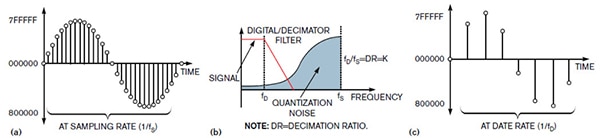

透過數位和降頻取樣濾波器的事件,即可有效降低 ΔƩ ADC 雜訊 (圖 6)。

圖 6:此圖列出時域中的數位濾波器輸出 (a)、疊加在降頻取樣濾波器低通函數上的調變器塑形雜訊輸出 (b),以及時域中的降頻器輸出訊號 (c)。(圖片來源:EDN)

圖 6:此圖列出時域中的數位濾波器輸出 (a)、疊加在降頻取樣濾波器低通函數上的調變器塑形雜訊輸出 (b),以及時域中的降頻器輸出訊號 (c)。(圖片來源:EDN)

圖 6 顯示數位訊號通過數位/降頻取樣濾波器時的情形。數位濾波器 24 位元輸出 (圖 6(a)) 的運作速率與調變器取樣率 (1/Fs) 相同。調變器已將量化雜訊塑形成更高的頻率 (圖 6(b)),因此數位/降頻取樣濾波器會擷取輸出訊號的較低頻率部分。降頻取樣濾波器 (圖 6(c)) 輸出會以較低頻率的數位形式呈現原本的類比訊號。

數位擴張

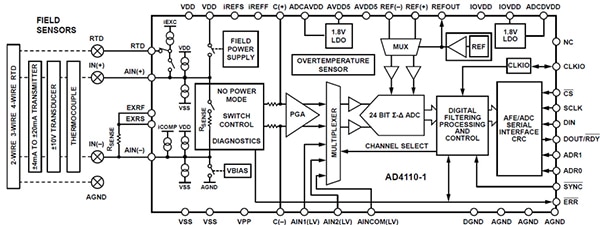

ΔƩ ADC 主要駐留在數位域中。現在,可以輕鬆添加數位可編程增益級、電流源、短路或開路輸入訊號指示器,以及多種序列輸出介面 (圖 7)。

圖 7:Analog Devices 的 AD4110-1 為工業製程控制系統提供多種類比前端功能。(圖片來源:Analog Devices)

圖 7:Analog Devices 的 AD4110-1 為工業製程控制系統提供多種類比前端功能。(圖片來源:Analog Devices)

圖 7 顯示 Analog Devices 的 AD4110-1 ΔƩ ADC 具有多種數位增強項目,包括可編程輸入端子、診斷功能和彈性的數據傳輸率。輸入就緒感測器介面包含 RTD 和熱電偶溫度感測器。

AD4110-1 具有 ΔƩ ADC 的核心架構,但此裝置的數位加強功能還可促成一系列的數位功能,因此 AD4110-1 如今成為通用類比前端 (AFE)。

AD4110-1 與標準 ΔƩ ADC 相同,都能將熱電偶、RTD 和橋接器的極低電壓進行數位化。雖然這些功能通常需要額外的激磁電路,但 AD4110-1 已經將其整合在板件上。

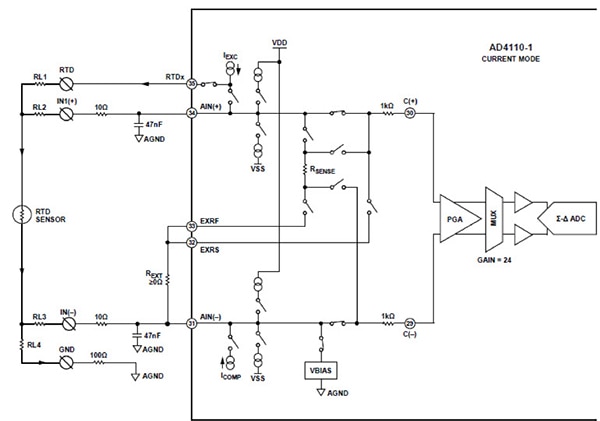

例如,RTD 需要一個精密電流源,且此電流源與轉換器的參考電壓成比例 (圖 8)。

圖 8:四線式 RTD 和 AD4110-1 ΔƩ ADC 的適當接線。RTD 激磁電流可編程為 0.1 mA 至 1 mA 之間的六種位準。(圖片來源:Analog Devices)

圖 8:四線式 RTD 和 AD4110-1 ΔƩ ADC 的適當接線。RTD 激磁電流可編程為 0.1 mA 至 1 mA 之間的六種位準。(圖片來源:Analog Devices)

在圖 8 中,AD4110-1 包含一個激磁電流,此電流可以使用轉換器的 PGA_RTD_CTRL 暫存器,編程為 0.1 mA 至 1 mA 之間的六種位準。RTD 電阻的激磁電流來自引腳 35。轉換器透過引腳 34 和 31 高阻抗值輸入,來感測 RTD 兩端的壓降。AD4110-1 可編程增益放大器 (PGA) 提供 0.2 至 24 V/V 之間的 16 個可編程增益。設計人員可以運用此特點,進一步將輸入感測器補足到 AD4110-1 輸入範圍中。其他輔助功能包含上拉/下拉電流,以感測是否有裸線 (對熱電偶有用),以及增益校準和校正係數。

結論

ΔƩ ADC 採用前端調變器、FIR 數位濾波器和降頻取樣濾波器,可省去複雜的類比前端電路,並能提供經過數位平均的高解析度、低雜訊數位輸出訊號。由於許多電路都採用數位形式,因此可以透過進階數位處理節點輕鬆擴充,還能加入更多功能,同時維持小覆蓋區並減少機板複雜度。

Analog Devices 的 AD4110-1 ΔƩ ADC 充分利用這種 ADC 架構的特性。AD4110-1 具有 ΔƩ ADC 的核心架構,但此裝置的數位加強功能還可促成一系列的數位功能,因此 AD4110-1 如今成為通用 AFE,並具有 RTD 和熱電偶的真正支援能力。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。