「可編程」類比元件究竟怎麼了?

最近,有人透過 LinkedIn 寄了一封電子郵件給我,詢問我 2001 年撰寫的一篇文章是否有任何更新。哇!真的是凡走過必留下痕跡!這是一篇關於可編程類比元件的文章,主要探討類比訊號鏈功能的不同設計選項。

我很討厭看如今的大眾新聞,其中一個原因是這些報導有頭沒尾:你看到逮捕犯人時戲劇化的現場實況報導,卻很少看到後續的審判結果。有鑒於這篇文章已經發表近 20 年,似乎有必要重新回顧一下這個主題。

不過,首先要釐清一項定義。巿面上有許多可編程類比 IC,能讓使用者透過固定引腳、離散電阻,或透過 I2C/SPI 連接埠驅動的軟體,設定一些工作參數或功能,如頻寬或取樣率等。但這些並非我所指的「可編程」。

我所指的是讓現場可編程閘陣列 (FPGA) 更加完備類比元件。FPGA 是一種具有大量無約束數位閘陣列和功能的元件。這些閘陣列和功能可視需要互連,建立最終的電路拓樸,進而構成極複雜的數位系統;閘數達百萬以上的 FPGA 現今相當常見。毫無疑問地,FPGA 已成為主流趨勢 (原因我不在此解釋),而且還在不斷地推陳出新。

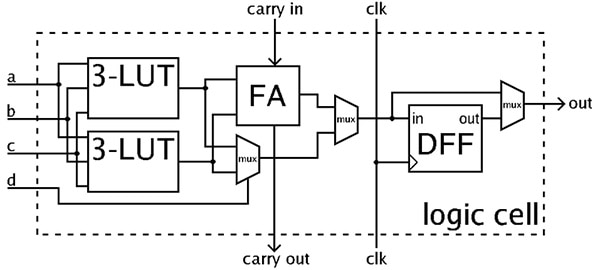

圖 1:Efinix 的 T4F81C FPGA 是以 SMIC 的 40 nm 製程打造,在 1.1 V 下的典型核心漏電流低於 150 µA。(圖片來源:Efinix)

圖 1:Efinix 的 T4F81C FPGA 是以 SMIC 的 40 nm 製程打造,在 1.1 V 下的典型核心漏電流低於 150 µA。(圖片來源:Efinix)

最新的產品是 Efinix 推出的 T4F81C2 Trion™,此款 FPGA 是以 SMIC 的 40 nm 製程打造,並採用 81 焊球 BGA 封裝 (圖 1)。

T4F81C 採用高密度、低功率的 Efinix Quantum™ 架構,將 I/O 介面封裝在小型覆蓋區內。此元件的目標市場是需要低功率、低成本與小尺寸的行動裝置、消費性及 IoT 邊緣裝置巿場。T4F81C 的特色包括:

- 以 SMIC 的 40 nm 製程打造

- 在 1.1 V 下的典型核心漏電流低於 150 µA

- 採用高效能 I/O,可支援 1.8 V、2.5 V 和 3.3 V 單端 I/O 標準和介面

- 提供靈活的晶片上時脈

- 提供元件配置選項,包括標準 SPI 和 JTAG 介面

隨著技術演進,FPGA 會不斷推陳出新,因應更多樣化的需求和應用,反觀可編程類比元件卻沒在近期跟著蓬勃發展。

想法似乎不錯,為何...?

如此看來,或許需要推出具有大量無約束類比功能的類似 IC。理論上,這種元件可以為感測器介面、訊號調節、濾波,甚至主機處理器的 I/O 提供整個類比訊號鏈 (眾多例子之一)。這種現場可編程類比陣列 (FPAA) 甚至可以在 OEM 生產線上進行配置,針對同系列中的不同產品提供其所需的功能,因此眾多產品之間可共用 BOM。此外,如果類比鏈功能有必要更改,也不必經歷可怕的 PC 板重新設計過程以及隨之而來的延遲及不確定性。

但實際情況是,這種類型的可編程類比元件並未在工程設計界引起多少關注。請看一下我在 2001 年發表文章中提到的廠商,有些已經關門大吉,有些則被其他的 IC 公司兼併 (這個現象在業界早已司空見慣,無需多談),但沒有任何一家開發出佔據市場主導地位的產品。即使如此,這種產品並未消失,只是很少有人提及。我不曾聽說有設計人員打算選擇用可編程類比元件來滿足訊號鏈需求。

可編程類比元件為何流行不起來?我認為,原因在於類比電路無法避免的固有特性及其功能。就以最基本的類比構建區塊功能 (如運算放大器和比較器) 來說吧,大多數製造商都會在產品組合中提供數十種,甚至上百種這類元件 (請參閱《令人頭痛:為何有如此多種運算放大器?》)。其原因在於,為了提供獨一無二的效能屬性組合,每個型號都會經過設計調整、生產製程,以及測試/微調。舉例來說,某款運算放大器可能有極佳的低雜訊效能,但比起另一款具有更高雜訊的同類型號,卻有較大的偏移漂移。

關鍵在於多方面權衡

設計人員必須評估權衡,並決定犧牲何種效能以便換取其所需的高優先權效能。運算放大器可在關鍵的靜態和動態規格之間提供多種搭配組合,有些在一兩個層面上表現傑出,但在其他層面卻表現普通;有些則在大多數規格上「表現不錯」,卻沒有任何一項規格真正特別突出。所以,哪一款才是設計人員的「最佳選擇」?

答案永遠是「看情況」,必須取決於設計的優先考量以及各項取捨的權重而定。想想那些用來評估基本運算放大器的參數吧,例如速度、電壓偏移、偏壓電流、溫度漂移、頻寬、雜訊、耗散、增益、驅動能力和電壓範圍等等,你可以列出一個長長的清單。

此外,如果退一步看大局,與 FPGA 數位世界不同的是,大多數類比訊號鏈並沒有太多功能區塊,而且彼此的功能區塊通常差異極大。類比區塊的關鍵特性會隨訊號的位置而變化:你在面向感測器的介面中需要的特性,不再是使用帶通濾波器、用於驅動負載或處理器 I/O 時所需要的特性。

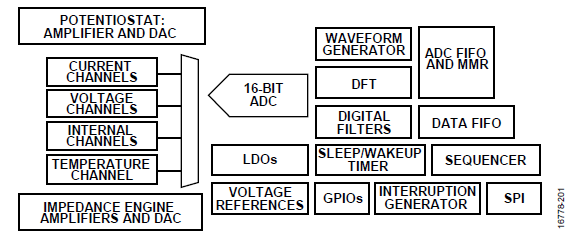

以 Analog Devices 的 AD5940 為例,此利基型 IC,可針對化學實驗室設定提供高精確度的阻抗和電化學前端 (圖 2)。AD5940 包含大量的類比和數位功能,但是類比功能的差異最大,其規格經過仔細規劃,可相容於支援的電化感測器。

圖 2:AD5940 的簡化方塊圖。(圖片來源:Analog Devices)

圖 2:AD5940 的簡化方塊圖。(圖片來源:Analog Devices)

儘管這款元件內建類比數位轉換器 (ADC),甚至有內部管理用的微控制器,但設計中最靈敏的部分,是與專用實驗室恆電位器電極介接的部分,包括具有近零偏壓電流的運算放大器和可編程增益放大器 (PGA)。在更通用的 FPAA 內的類比功能則不會有所需的靈敏特性。

結論

儘管類比區塊陣列乍看之下很有吸引力,但現實是,通用的類比區塊陣列無法滿足許多應用的不同需求。雖然在 BOM 複雜度、PC 板佔用空間及其他設計因素方面有實際優勢,但這些優勢不足以讓設計人員做出妥協。

對大多數類比設計來說,最好的設計方法是:針對訊號鏈的每個部分精心挑選一些最符合要求的 IC (這些 IC 通常是不同的)。好消息?對於訊號鏈的每個階段,都不乏優良選擇。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum