如何為邏輯電路或閘極設計選擇 MOSFET

金屬氧化物半導體 (MOS) 變體的場效電晶體,或稱 MOSFET,是常見的高電壓、高電流、電壓驅動式切換應用的首選半導體。這類產品比其前身的電流驅動式產品「雙極性接面電晶體」(BJT) 更受歡迎。在切換式應用的另一端,邏輯位準 MOSFET 在處理器及其他小型訊號元件的結構中佔據主導地位,主因是其具有更高的效率和高速的切換能力。

就配置而言,MOSFET 的內部工作原理與 BJT 明顯不同,但仍使用增強型或空乏型通道的 N 與 P 接面,而此位置即是導電處。如需瞭解 MOSFET 結構與運作的一般說明,請閱讀 Digi-Key Electronics 在 eewiki 上的文章。

市面上有許多微控制器試驗電路板或 PCB 專案指定 TTL 邏輯使用 BJT 電晶體,如常用的 2N3904 (NPN) 或 2N3906 (PNP) 等。這類電晶體無論是否對基極預先施加偏壓都會有良好的表現,但效率較低,而且在某些情況下,回應時間會比同類的 CMOS 產品更慢。

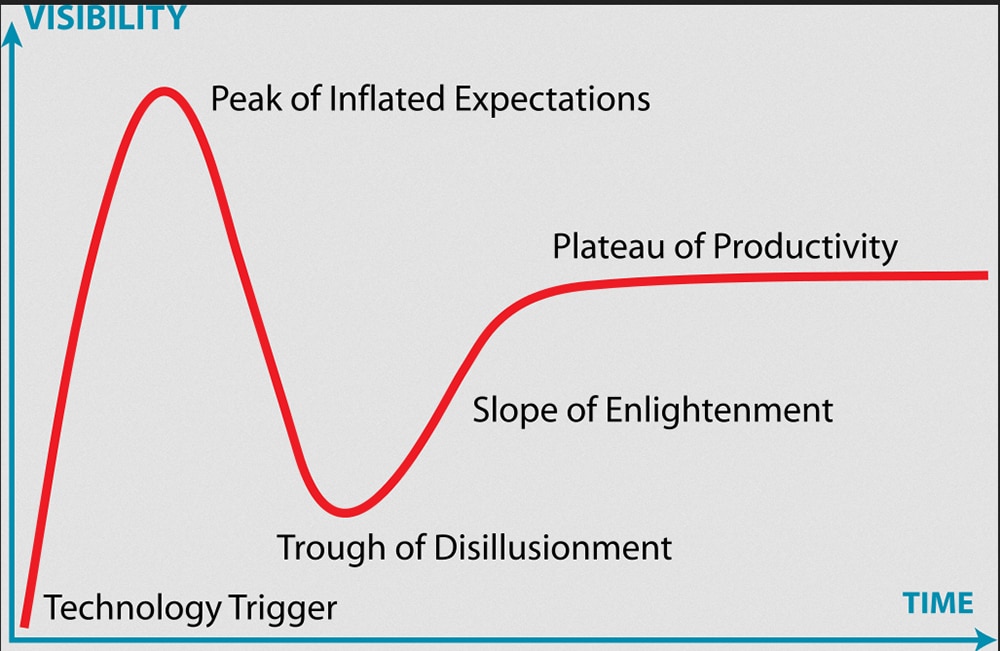

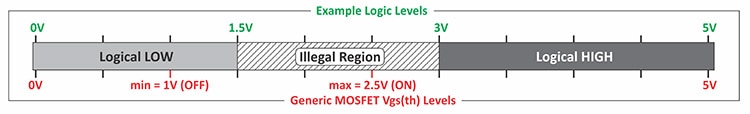

無論是使用 3.3 V 還是 5 V 邏輯,這兩種電壓與接地之間都會存在多個閾值,可確定邏輯是高還是低。同時,在高低電壓之間還需要有一個電壓範圍作為緩衝區,此區通常稱為「非法」區,可確保固態高值與固態低值之間的臨界點不會太突然地出現,否則可能會導致輸出無法預測 (圖 1)。

選擇邏輯位準 N 通道 MOSFET 時須考慮的參數

閘極源極閾值電壓 - Vgs(th)(min) 與 Vgs(th)(max):當閘極電壓等於或低於最小閾值時,MOSFET 將會截止。5 V 邏輯的常見最小閘極電壓可能介於 0.5 V 至 1 V 之間。當閘極電壓超過最大閾值時,MOSFET 將會導通。若閘極閾值電壓在最小閾值和最大閾值之間,MOSFET 可能會導通,也可能會截止,因此必須加以避免。請注意,在圖 1 中最小值與最大值之間的區域大致與非法區重合。

圖 1

圖 1

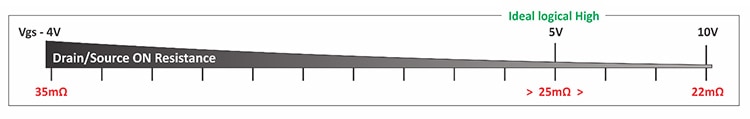

汲極-源極導通電阻 - Rds(on):導通時,汲極與源極之間存在電阻,而且此電阻會隨著閘極源極電壓 (即 Vgs) 的增加而減小。請選擇一個 MOSFET,其最低 Rds(on) 值恰好位於或接近理想邏輯高電壓值,並且不會隨著較高的 Vgs 值而大幅降低。請參閱圖 2。

圖 2

圖 2

範例:依照規格書,Infineon 的 IRLZ44 MOSFET 在 5 V 下的汲極-源極電阻為 25 mΩ;在 4 V 下為 35 mΩ;在 10 V 下為 22 mΩ。在 5 V 下,此元件的 Rds(on) 值僅比在 10 V 下的數值高出 3 mΩ,但比在 4 V 下的 Rds(on) 值低 10 mΩ,因此就 Rds(on) 而言,本產品是個不錯的選擇。

圖 3

圖 3

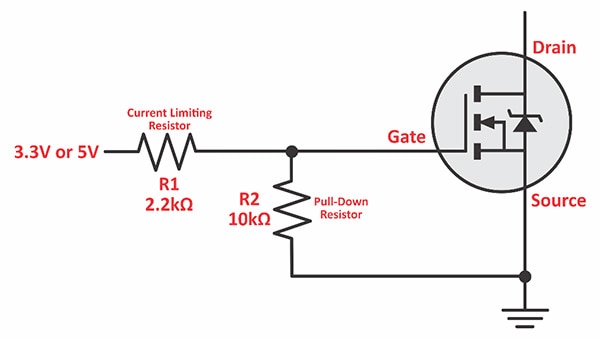

輸入電容 - Ciss:由 MOSFET 的閘極、氧化層與基體連接所形成的組合可充當小型電容,在閘極出現電壓時開始充電。由於充電需要時間,這會導致導通狀態發生延遲。因此,需選擇輸入電容盡可能最低的 MOSFET,以避免發生長時間延遲,並最大程度降低湧入電流;該湧入電流起初可能很高,但會隨著電容充電而減小。理想情況下,導通狀態延遲極為短暫,但可能產生足夠的突波,導致電流流出容量有限的 I/O 引腳受損。

在引腳與閘極之間放置限流電阻,可防止 I/O 引腳消耗過多電流。

若使用與微控制器輸出引腳直接相連的 MOSFET,則根據需要應使用外部電阻,將 MOSFET 閘極拉高或拉低,以避免 MOSFET 在 MCU 啟動及重置期間產生浮動閘極邏輯以及不想要的輸出。

在為邏輯電路或閘極設計選擇 MOSFET 時,您可以從上述參數入手並進行微調,同時還須考量散熱及其他效能參數。請在您的下一個設計專案中勇於嘗試 MOSFET 吧!

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum