如何設計和認證功能安全性 RTD 型系統

資料提供者:DigiKey 北美編輯群

2023-07-24

電阻溫度偵測器 (RTD) 由傳感器及其類比前端 (AFE) 訊號調整電路組成,不僅用途廣泛且準確可靠。但對於可靠性高的任務關鍵型應用,往往須透過 Route 1S 或 Route 2S 元件認證流程來設計和確保功能安全性系統。

對系統進行功能安全認證是個相當複雜的過程,所有系統內的元件都必須經過檢視,查看是否有任何潛在的失效模式和機制。診斷失效的方法很多,而認證時若搭配經認證的零件,即能減輕診斷工作的負擔。

請注意,「可靠性」和「功能安全性」雖有關,但不能畫上等號。簡單來說,「可靠」是指某個設計和實作能在不發生問題或失效的情況下符合運作規格;「功能安全性」則代表任何失效問題都必須在設計過程中逐一檢測而出。對關鍵應用來說,可靠性和功能安全性缺一不可。

本文將在功能安全認證的框架中,介紹 RTD 及其訊號調整電路的基礎知識。接著將討論各種可靠性與失效認證等級,以及使用兩種認證方式時需滿足哪些條件,才能達到相應等級。本文將運用兩個多通道 RTD AFE IC、Analog Devices 的兩種 AD7124 產品,以及相關的評估板配置以說明相關要點。

功能安全性的作用

功能安全性的作用是透過正確實行一或多種自動保護/安全功能,保護人們免於無法承受的受傷風險或健康損害。這樣一來,即能確保產品、裝置或系統在出現故障的狀況下持續安全運作。功能安全性是許多工業、商業甚至一些消費性應用所必需的,例如:

- 自駕車

- 機器安全性與機器人

- 工業控制系統 (ICS)

- 消費性智慧型家庭產品

- 智慧型工廠與供應鏈

- 安全儀控系統與危險區域控制系統

例如,在功能安全性設計中,即使系統內其他元件故障,主電源開關仍會支援斷電功能 (圖 1)。

圖 1:在功能安全性系統中,此開關無疑會按照其設計的方式執行。(圖片來源:Pilla 經 City Electric Supply Co. 提供)

圖 1:在功能安全性系統中,此開關無疑會按照其設計的方式執行。(圖片來源:Pilla 經 City Electric Supply Co. 提供)

RTD 基礎知識

為什麼要考慮溫度和功能安全性?原因之一是,溫度是最常測量的物理參數。溫度常與安全性或關鍵應用有關,並由多種傳感器支援,其中包括 RTD。其概念很簡單:它們能利用鎳、銅、白金等金屬的已知電阻溫度係數 (TCR),此外還具重複性。其中最為廣泛使用是 0°C 下電阻值為 100 Ω 和 1000 Ω 的白金 RTD。另外,它們也能在 -200°C 至 +850°C 的範圍內使用。

在此溫度範圍內,這些 RTD 的線性電阻-溫度關係較明顯;在準確度超高的情況,也可套用校正和補償表及因數。白金 RTD 的標稱電阻為 100 Ω (名為 PT100),在 -200°C 時,典型電阻值為 18 Ω,在 +850°C 時為 390.4 Ω。

使用 RTD 時,必須以某個已知的電流進行激磁,該電流通常保持在 1 mA 左右,以將自體發熱降至最低。其中,也會根據 RTD 的標稱電阻使用其他電流值。

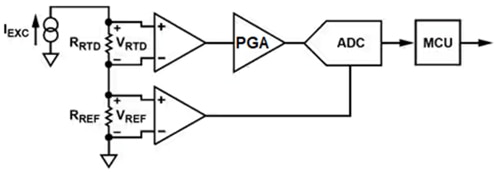

RTD 的壓降乃是透過 AFE 同時測量,此 AFE 包含一個可編程增益放大器 (PGA),且在絕大對數情況下,還包含一個類比數位轉換器 (ADC) 和微控制器單元 (MCU) (圖 2)。

圖 2:使用 RTD 測量溫度時,需要透過 RTD 驅動已知的電流、測量其壓降,接著再套用歐姆定律。(圖片來源:Digi-Key)

圖 2:使用 RTD 測量溫度時,需要透過 RTD 驅動已知的電流、測量其壓降,接著再套用歐姆定律。(圖片來源:Digi-Key)

此基本結構的電路拓撲與「使用感應電阻來判定負載電流」相同,但已知和未知變數會對調。對於電流感測,電阻值為已知,而電流為未知,因此計算式為 I = V/R。對於 RTD,電流為已知,但電阻值未知,因此計算式為 R = V/I。

需要使用 PGA 才能維持訊號完整性及達到最大的動態範圍,因為 RTD 的電壓位準將根據 RTD 的類型和溫度而介於數十到數百 mV 不等。

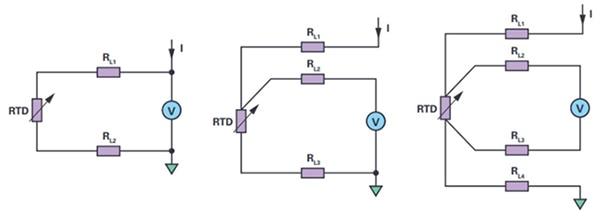

激磁來源、RTD 和 PGA 之間的實體連接,可以是雙線、三線或四線介面。雖然原則上兩條引線已經足夠,但連接引線存在 IR 壓降問題以及其他偽影。在更進階的開爾文接法中使用三線和四線拓撲,雖然會增加佈線成本,但能提高準確性和一致性 (圖 3)。

圖 3:RTD 僅透過兩條電線 (左側) 就能驅動和感測,但使用三條引線 (中間) 甚至四條 (右側,開爾文接法) 能消除引線造成的多種錯誤來源。(圖片來源:Analog Devices)

圖 3:RTD 僅透過兩條電線 (左側) 就能驅動和感測,但使用三條引線 (中間) 甚至四條 (右側,開爾文接法) 能消除引線造成的多種錯誤來源。(圖片來源:Analog Devices)

從瞭解相關術語及標準開始

如同許多專業領域,功能安全性也有許多獨特的術語、資料集和縮寫,且在進行相關討論時會被廣泛使用。其中包括:

- 失效率 (FIT):表示裝置每運作十億 (109) 小時可能出現的失效次數。

- 失效模式與效應分析 (FMEA):此流程旨在盡可能檢視最多元件、組件和子系統,以找出系統中的潛在失效模式,以及其因果關係。

- 失效模式效應與診斷分析 (FMEDA):一種系統性分析技術,用於取得子系統/產品層級失效率、失效模式和診斷能力。

要進行完整的分析,需要使用 FIT 資料,同時對系統不同的元件進行失效模式效應與診斷分析 (FMEDA)。FMEA 只提供定性資訊,FMEDA 則提供定性與定量資訊,讓使用者能測量失效模式的關鍵性級別,並根據重要性予以排序。FMEDA 增加了風險、失效模式、效應與診斷分析,以及可靠度資訊。

- 安全完整性等級 (SIL):SIL 有四個完整性等級:SIL 1、SIL 2、SIL 3 和 SIL 4。SIL 等級越高,相關安全性等級越高,系統無法正常執行的可能性也就越低。

SIL 2 等級表示,系統內部 90% 以上的失效都能診斷出來。設計要獲得認證,系統設計人員必須針對潛在失效、該失效是否具危險性以及這類失效的診斷方式,向認證機構提出證明。

- IEC 61508 是功能安全性設計的規格,正式名稱為「電氣/電子/可編程電子安全相關系統的功能安全性」,非正式名稱為「電子功能安全性」。此規格記錄了開發 SIL 認證零件所需採取的設計流程。從概念和定義,到設計、佈局、製造、組裝與測試,每個步驟都必須提供文件。

此流程稱為 Route 1S,且非常複雜。不過,Route 1S 還有一種替代方法,即 Route 2S 流程。此途徑「經過使用實證」,當產品已大量設計為終端產品與系統、正在現場使用,且運作時數已累積數千小時,即適用此方式。

根據 Route 2S 流程,只要向認證機構提供以下證據,產品仍可取得認證:

- 現場使用量

- 分析任何現場退貨,並詳細說明退貨原因並非是元件本身失效而造成

- 安全規格書,當中詳述了診斷及其提供的覆蓋率

- 引腳與晶粒 FMEDA

合併 RTD 介面與 SIL Route 2S 流程

取得系統認證是個漫長的過程,因為系統的所有元件都必須經過檢視,查看是否存在潛在的失效機制,而且診斷失效的方法很多。使用經認證的零件能減輕工作負擔,並縮短認證流程。

成熟且高度整合的 RTD 介面元件,是簡化 Route 2S 認證的關鍵,因為此元件定義了完整的解決方案套件,因此能藉由現場應用與失效相關的資料,來進行完整特性化。這與使用許多較小的建置區塊 IC 不同,該情況必須針對使用的互連配置,分析 IC 的各種介面及互動。

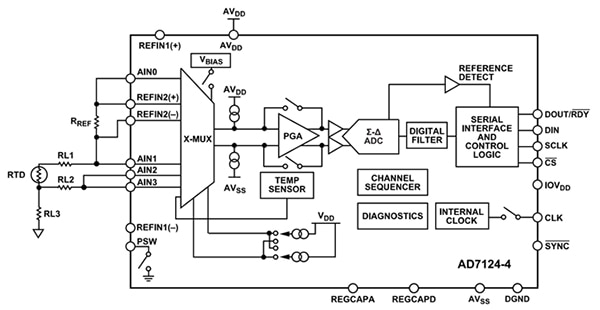

其中一個範例是四通道 AD7124-4 (圖 4),以及類似的八通道 AD7124-8 (以下論及許多共同特點時統稱為「AD7124」)。這些元件具有嵌入式自我測試與診斷特點,另外還有現場「追蹤記錄」,因此非常適合用於 Route 2S 流程。

圖 4:四通道 AD7124-4 功能完整的 RTD 感測器對處理器訊號鏈。(圖片來源:Analog Devices)

圖 4:四通道 AD7124-4 功能完整的 RTD 感測器對處理器訊號鏈。(圖片來源:Analog Devices)

這些 IC 是多通道 RTD 量測的完整解決方案,從感測器到數位化輸出,所有必要的建置區塊都包含在內,也能幫助與相關的微控制器進行通訊。其包含多通道多工器、PGA、24 位元三角積分 ADC、RTD 的電流源、用於內部操作的參考電壓、系統時脈、類比與數位濾波,以及 SPI、QSPI、MICROWIRE 與 DSP 相容互連的三線或四線串列介面。

然而,這些功能本身無法為 SIL Route 2S 資格提供基礎。對於功能安全性設計,組成 RTD 系統的許多功能都需要一系列的嵌入式診斷。AD7124 的多個嵌入式診斷,能盡可能減少設計的複雜性和設計時間,使用者亦無須針對診斷覆蓋率來複製訊號鏈。

這些診斷包括但不限於監測電源、參考電壓和類比輸入;偵測 RTD 的明線;檢查轉換和校正效能;檢查訊號鏈的功能;監測讀/寫功能;以及監測暫存器內容。

這些「高階」的陳述內容,如何轉化為必要的晶片上診斷?這個問題的答案牽涉許多層面,包括:

SPI 診斷:每次寫入 AD7124 時,處理器都會產生循環冗餘檢查 (CRC) 值,而此值會附加到傳送至 ADC 的資訊上。接著,ADC 從接收的資訊產生自己的 CRC 值,並與來自處理器的 CRC 值進行比較。如果兩個值一致,則代表資訊完整無缺,並將寫入晶片上相關的暫存器。

如果值不相符,則代表傳輸時出現了些許毀損,而 IC 會設定錯誤標示,以指明受到毀損的資料。AD7124 還會自我保護,以避免將毀損的資訊寫入暫存器。

資訊從 AD7124 讀取至系統處理器時,也採用類似的 CRC 程序。最後,介面還會計算時脈脈衝的數量,以確保每個讀取或寫入資料訊框只有八個時脈脈衝,進而確保未發生時脈突波。

記憶體檢查:CRC 也可用於驗證暫存器的內容,無論是通電時,還是每當晶片上的暫存器更動時 (例如更改增益時)。CRC 流程也會定期執行,以確保記憶體位元不會因為雜訊或其他原因而「翻轉」。如果出現任何變更,且處理器隨後被標記為暫存器設定已毀損,則此流程能重設 ADC 並重新載入暫存器。

訊號鏈檢查:所有關鍵靜態電壓均可透過 ADC 檢查,包括電軌、低壓降 (LDO) 穩壓器輸出與參考電壓;還能檢查 LDO 穩壓器上是否存在外部電容。此外,能對 ADC 輸入施加已知電壓,以檢查 ADC 和增益功能設定。此外,還能在類比輸入上注入已知電流,以檢查其為開路 RTD 還是短路 RTD。

轉換和校正:持續檢查 ADC 轉換的結果,瞭解其是全為 0 還是滿量程 (無論何者都表示存在問題)。監測 ADC 核心調變器發出的位元串流,以確保其未達到飽和,如果達到飽和 (代表調變器有連續 20 個 1 或 0),則會標示錯誤標誌。

主時脈頻率:此時脈的頻率不僅能控制轉換率,還可確定 50/60 Hz 數位濾波器的限波頻率。AD7124 的內部暫存器,使輔助處理器能計時並因此檢查主時脈的準確度。

其他特點:AD7124 包含溫度感測器,也可用於監測晶粒溫度。這兩種版本都有 4 kV 靜電放電 (ESD) 額定值,以達到穩健的效能;同時也都採用 5×5 mm 的 LFCSP 封裝,而此封裝適用於本質安全型設計。

由於 AD7124-4 和 AD7124-8 的內部複雜性、精密性及進階的自我測試特點,擁有一套執行和評估 IC 的方法合情合理。

為此,Analog Devices 提供一對連接板:EVAL-AD7124-4SDZ 評估板 (針對 AD7124-4;圖 5),和 EVAL-SDP-CB1Z SDP 輔助板 (系統展示平台)/介面板 (圖 6)。前者專門用於 AD7124-4,並可與後者搭配運作;後者則透過 USB 鏈路與使用者的 PC 及評估軟體進行通訊。

圖 5:EVAL-AD7124-4SDZ 是一款適用於 AD7124-4 的評估板。(圖片來源:Analog Devices)

圖 5:EVAL-AD7124-4SDZ 是一款適用於 AD7124-4 的評估板。(圖片來源:Analog Devices)

圖 6:EVAL-SDP-CB1Z/介面板是 EVAL-AD7124-4SDZ 評估板的輔助板,可提供 USB 與主機 PC 的連接。(圖片來源:Analog Devices)

圖 6:EVAL-SDP-CB1Z/介面板是 EVAL-AD7124-4SDZ 評估板的輔助板,可提供 USB 與主機 PC 的連接。(圖片來源:Analog Devices)

評估配置由 AD7124-4 EVAL+ 軟體支援,該軟體全面設定 AD7124-4 裝置暫存器功能以及執行 IC。其還可以波形圖、直方圖、相關雜訊分析的形式提供時域分析,以進行 ADC 效能評估。

過渡到功能安全性設計

務必注意,AD7124-4 和 AD7124-8 並無 SIL 等級,因此皆非以 IEC 61508 標準定義的開發準則進行設計與開發。但是,瞭解終端應用並妥善使用各種診斷,進而評估這兩者,可確定其是否可用於 SIL 等級型設計。

失效可能具系統性,也可能是隨機的,因此要分析和解決失效,Route 1S 認證方式有許多考量因素。系統性失效源自於設計或製造缺陷,例如因外部中斷引腳缺乏濾波或訊號餘裕不足,而導致雜訊中斷。相較之下,隨機失效則源自腐蝕、熱應力或磨損等物理原因。

其中重點關注的是未被偵測出的危險失效,可靠多種技術合力解決。要將隨機失效減到最少,設計人員可採用以下其中一種策略,或三種全採用:

- 更可靠、應力更小的元件。

- 仰賴內建的偵測機制來進行診斷,而且該偵測機制可透過硬體或軟體予以實作。

- 透過備援電路進行容錯。多增加一條備援路徑,便能多容許一次失效。這稱為硬體容錯 1 (HFT 1) 系統,亦即一次失效不會導致整個系統故障。

矩陣圖是瞭解 SIL 等級覆蓋率的有效工具,由矩陣圖繪製出安全失效分數 (SFF,即診斷覆蓋量) 和硬體容錯 (備援) (圖 7)。

|

|||||||||||||||||||||||

圖 7:此矩陣圖顯示出安全失效分數 (SFF) 相對於硬體容錯 (HFT) 的特性,並列出 SIL 覆蓋率。(圖片來源:Analog Devices)

矩陣圖列表示診斷覆蓋量,而矩陣圖欄表示硬體容錯。HFT 為 0 表示,如果系統存在一個故障,則將會喪失安全功能。進行更高階的診斷能減少所需的系統備援量,或能讓相同備援程度的解決方案達到更高的 SIL 等級 (下移至矩陣圖)。

請注意,根據 IEC 61508,某個採用這些裝置的典型溫度應用,其 FMEDA 顯示的安全失效比率 (SFF) 超過 90%。雖然通常需使用兩個傳統的 ADC,才能透過備援提供此等覆蓋率,但 AD4172 只需要一個 ADC,因此大大節省了物料清單 (BOM) 成本與電路板面積。

SIL 等級設計的文件

要取得 Route 1S 認證,需要搭配大量的文件。必要的來源文件包括:

- 安全規格書 (SIL 等級型零件的安全手冊)

- 引腳 FMEDA 和晶粒 FMEDA (兩者皆包含失效模式、效應與分析)

- 附件 F 檢查清單 (由 IEC 61508 定義)

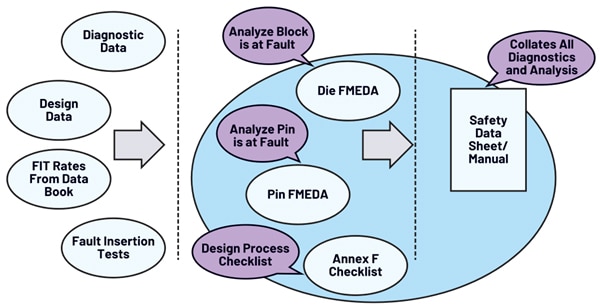

這份文件包含多種資料來源 (圖 8):

- 規格書中的診斷資料,其中記錄了零件中的所有診斷特點。

- 設計資料指的是內部資料,例如晶粒面積和零件各內部區塊的影響。

- FIT (包含各種元件的比率) 來自於資料手冊。

- 對無法使用設計與診斷資料進行分析的區塊,執行故障插入測試。這些測試根據應用要求進行規劃,而故障插入測試的結果則可用於強化 FMEDA 與 FMEA 文件。

圖 8:彙整和擷取多種文件來源,以提供 SIL 認證作業所需的完整資訊套件。(圖片來源:Analog Devices)

圖 8:彙整和擷取多種文件來源,以提供 SIL 認證作業所需的完整資訊套件。(圖片來源:Analog Devices)

深究細節:

- 安全手冊或安全規格書運用所有編譯的資訊來提供必要要求,進而完成 AD7124-4 或 AD7124-8 整合。其收集整理了來自各種文件和資料集的所有診斷與分析。

- AD7124-4 和 AD7124-8 的晶粒 FMEDA,可分析應用線路圖中的主要區塊、辨識失效模式與效應,以及檢查特定安全功能的診斷與分析。例如,時脈模組分析顯示了失效模式、各模式對輸出的效應、診斷覆蓋量,以及影響的分析 (圖 9)。

|

圖 9:此表定義了主時脈區塊失效模式、效應、診斷與分析。(圖片來源:Analog Devices)

此晶粒 FMEDA 可定量顯示安全失效、已偵測出的危險失效和未偵測出的危險失效之失效率。這些都可用於計算 SFF。

引腳 FDEMA 從不同的角度看待失效。它會分析 AD7124-4 和 AD7124-8 引腳上的各種失效,以及其對 RTD 應用產生的結果。它為每個引腳執行此分析,並描述以下這些情況的結果:引腳開啟、電源/接地短路,或鄰近引腳短路。

附件 F 檢查清單是一種設計措施檢查清單,用於避免發生系統性失效。其中包含:

- 產品總覽

- 應用資訊

- 安全概念

- 壽命預測

- FIT

- FMEDA 計算 - SFF 和 DC

- 硬體安全機制

- 診斷說明

- EMC 穩健性

- 備援設定下的操作

- 附件與文件清單

總之,要透過 Route 1S 對新推出的元件進行功能安全性認證,是一個漫長、複雜、耗時的全面性密集流程。所幸,本文提到的 Route 2S 是一種能用於其中部分元件的替代方法。

Route 2S:替代途徑

Route 2S 適用於某個已釋出、具有現場經驗及資料的零件,此替代途徑也被稱為「經過使用實證」。此方式以客戶退貨分析和運送的裝置數量為基礎。在實際使用方面幾乎 (或完全) 沒有公開「追蹤記錄」的新零件,不能使用此方式。

Route 2S 允許 SIL 認證,就好像該零件已根據 IEC 61508 標準執行完整分析。如果模組和系統的設計人員過去曾成功使用實驗 IC,並已從現場瞭解失效率,就能使用此替代方式。AD7214-4 和 AD7214-8 具有嵌入式測試與驗證特點以及效能資料,因此成為實行 Route 2S 的理想之選。

要調用 Route 2S,必須具備詳細的現場退貨與失效資料,該資料也必須具有統計意義。相較於板件或模組供應商,IC 供應商要滿足此要求更加不易,因為 IC 供應商一般不夠瞭解最終的應用,或不夠瞭解現場退回多少比例的故障單元供其分析。

結論

以 Route 1S 對新產品進行功能安全性認證,是一種詳細、完整的全面式途徑。技術上也很有挑戰性,且絕對相當耗時。相較之下,Route 2S 流程則讓人根據現場經驗、失效與分析資料,對釋出的產品進行認證。這種方式非常實用,受到 AD7214-4 和 AD7214-8 RTD 介面 IC 的支援,因為它們皆具有所需的歷程紀錄。同樣重要的是,這些 IC 嵌入了許多診斷與自我測試功能及特點,使其成為實行此類認證的適當選擇。

相關內容

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。