在 Xilinx ZCU102 評估套件上啟用 NVMe SSD 介面

資料提供者:DigiKey 北美編輯群

2020-05-12

總覽

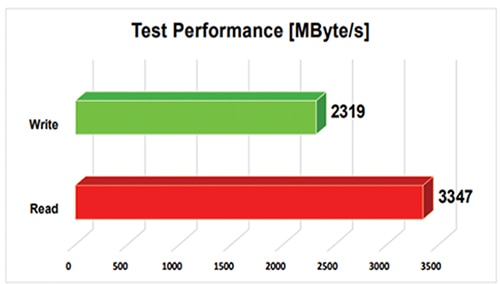

Zynq® UltraScale+™ MPSoC 系列以 Xilinx® UltraScale™ MPSoC 架構為基礎,在單一裝置中整合了功能豐富的 64 位元四核心或雙核心 ARM 架構處理系統 (PS),以及 Xilinx 可編程邏輯 (PL) UltraScale 架構。此外,亦包含晶片上記憶體、多埠外部記憶體介面以及豐富的周邊裝置連接介面,尤其是 GTH 16.3 Gbps 收發器,可支援 PCI Express® Gen3 儲存裝置介面 (例如 NVMe SSD 硬碟)。本文將說明在 Xilinx 的 ZCU102 評估套件上透過 Design Gateway 的 NVMeG3-IP 核心實作 NVMe 固態硬碟 (SSD) 介面的解決方案,可達到驚人的快速效能:2319 MB/s 的寫入速度和 3347 MB/s 的讀取速度。

Zynq® UltraScale+ MPSoC ZCU102 評估套件簡介

ZCU102 是一般用途評估板,能以 XCZU9EG-2FFVB1156E MPSoC 元件為基礎快速進行原型開發。此評估板包含高速 DDR4 SODIMM 和組件記憶體介面、FMC 擴充埠、每秒數 Gigabit 的序列收發器、多種周邊裝置介面,以及客製化設計用的 FPGA 邏輯,因此可提供靈活的原型開發平台。

圖 1:ZCU102 評估套件。(圖片來源:Xilinx Inc.)

圖 1:ZCU102 評估套件。(圖片來源:Xilinx Inc.)

ZCU102 提供可編程的邏輯功能,可用來打造最先進的應用,例如 5G 無線網路、新一代先進駕駛輔助系統 (ADAS) 和工業物聯網 (IIoT) 解決方案。

無論如何,若是應用要求使用高效能、高度可靠的外部資料儲存空間 (例如 NVMe SSD 硬碟),則需要選擇合適的解決方案,以運用 GTH 收發器提供 PCI Express® Gen3 相容介面的優勢。

NVMe SSD 儲存空間簡介

NVM Express (NVMe) 可針對主機控制器界定其介面,以透過 PCI Express 存取 SSD。NVM Express 只需使用兩個暫存器 (命令發布和命令完成),即可讓命令的發布和完成程序達到最佳化。另一方面,NVMe 支援平行操作,能在單一佇列中支援最高 64K 命令。64K 命令條目可改善循序存取和隨機存取的傳輸效能。

NVMe 硬碟為迎接高速資料儲存和運算做好準備。使用 PCIe Express® Gen3 技術,現代化 NVMe SSD 硬碟即可實現高達 40 Gbit/s 的峰值效能。

此處顯示 NVMe 儲存裝置範例。

在 ZCU102 上實作 NVMe 主機控制器

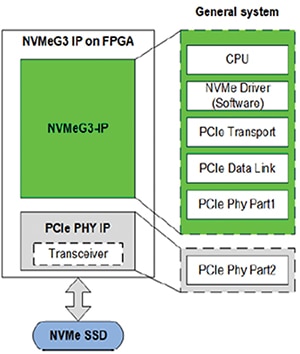

圖 2:NVMe 實作。(圖片來源:Design Gateway)

圖 2:NVMe 實作。(圖片來源:Design Gateway)

通常,NVMe 主機的實作會使用主機處理器搭配 PCIe 控制器一起操作,以便與 NVMe SSD 進行資料雙向傳輸。NVMe 協議的實作,是為了讓裝置驅動器與 PCIe 控制器硬體 CPU 周邊裝置,透過超高速匯流排進行通訊。而資料緩衝處理和命令佇列都需要外部 DDR 記憶體,以便在 PCIe 控制器和 SSD 之間傳輸資料。

由於 ZCU102 上的 XCZU9EG-2FFVB1156E FPGA 元件沒有 PCIe Gen3 整合區塊,因此無法採用傳統的實作方法。

Design Gateway 推出一項解決方案,可使用 NVMeG3-IP 核心 (如圖 2 所示),針對沒有 PCIe 整合區塊的 Zynq® UltraScale+™ MPSoC 元件啟用 NVMe SSD 介面。ZCU102 的 NVMe 介面可建構效能極高、FPGA 資源消耗最低的多通道 RAID 系統。NVMeG3-IP 核心授權包括範例公版設計,可幫助設計人員減少開發時間和成本。

Design Gateway 的 NVMeG3-IP 概述

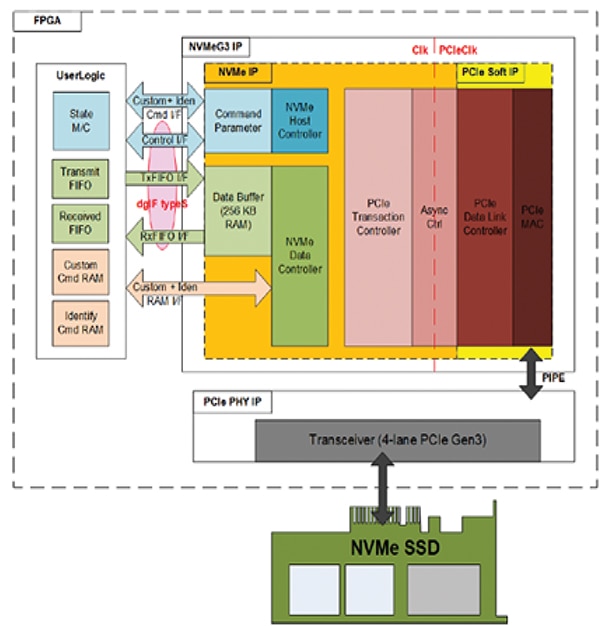

NVMe IP 核心具有 PCIe Gen 3 軟體 IP (NVMeG3-IP),非常適合在沒有 PCIe 整合區塊、CPU 和外部記憶體的情況下存取 NVMe SSD。NVMeG3-IP 包含 PCIe Gen3 軟體 IP 和 256 KB 記憶體。此解決方案可使用不含 PCIe 整合區塊的低成本 FPGA,因此推薦用於需要超高速效能 NVMe SSD 儲存空間的應用。

圖 3:NVMeG3-IP 方塊圖。(圖片來源:Design Gateway)

圖 3:NVMeG3-IP 方塊圖。(圖片來源:Design Gateway)

NVMeG3-IP 的特點

NVMeG3-IP 有許多特點,以下列出一些重點項目:

- 無需佔用 CPU,即可實作應用層、交易層、資料鏈路層,以及實體層的某些部分以存取 NVMe SSD

- 可搭配設定為 4 通道 PCIe Gen3 (128 位元匯流排介面) 的 Xilinx PCIe PHY IP 進行操作

- 包含 256 KB RAM 資料緩衝區

- 透過 dgIF typeS 提供簡便的使用者介面

- 支援六個命令,即識別 (Identify)、關機 (Shutdown)、寫入 (Write)、讀取 (Read)、SMART 以及排清 (Flush) (可選擇支援其他命令)

- 支援的 NVMe 裝置:

- 基本類程式碼:01h (大容量儲存),子類型程式碼:08h (非揮發性),編程介面:02h (NVMHCI)

- 最小記憶體分頁大小 (MPSMIN):0 (4 KB)

- 最大資料傳輸大小 (MDTS):至少 5 (128 KB) 或 0 (無限制)

- LBA 單元:512 位元組或 4096 位元組

- 使用者時脈頻率必須大於或等於 PCIe 時脈 (Gen3 為 250 MHz)

- 可用的公版設計:

- ZCU102 配 AB17-M2FMC 配接器板

- KCU105 配 AB18-PCIeX16/AB16-PCIeXOVR 配接器板

- VCU118 配 AB18-PCIeX16 配接器板

Design Gateway 開發 NVMeG3-IP 做為 NVMe 主機控制器執行,以便存取 NVMe SSD。不必了解 NVMe 協議,亦可輕鬆使用使用者介面和標準功能。NVMeG3-IP 的附加功能是內建 PCIe 軟體 IP,可透過純邏輯實作 PCIe 協議的資料鏈路層和實體層的某些部分。因此,透過內建的 PCIe 軟體 IP 和 Xilinx PCIe PHY IP 核心,NVMeG3-IP 即可在沒有 PCIe 整合區塊的 FPGA 中運作。Xilinx 的 PCIe PHY IP 是可免費取得的 IP 核心,其中包含收發器和邏輯等化器。

NVMeG3-IP 支援六個 NVMe 命令,即識別 (Identify)、關機 (Shutdown)、寫入 (Write)、讀取 (Read)、SMART 以及排清 (Flush)。256 KB BlockRAM 整合在 NVMeG3-IP 中,可當作資料緩衝區。此系統不需要 CPU 和外部記憶體。如需更多詳情,請參閱 NVMeG3-IP 的規格書 (可從我們的網站下載)。

下表 1 中顯示 XCZU9EG-2FFVB1156E FPGA 元件上的 FPGA 資源使用情況。

|

表 1:Ultrascale/Ultrascale+ 元件的實作統計資訊範例

ZCU102 的實作與效能結果

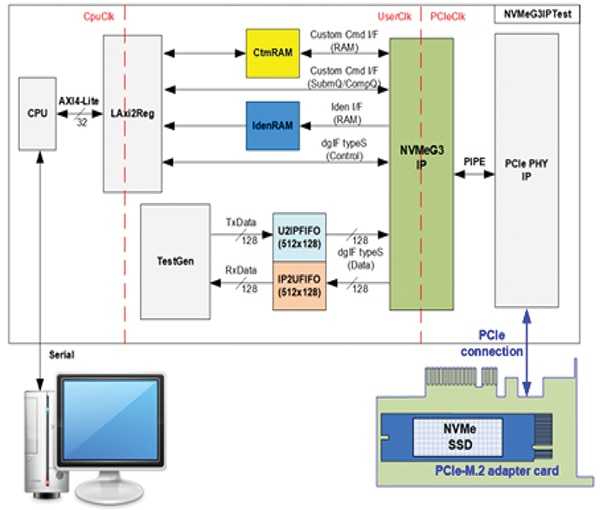

在圖 4 中,可概覽以 ZCU102 為基礎的公版設計,以示範 NVMeG3-IP 的操作。示範系統中的 NVMeG3IPTest 模組包括以下模組:TestGen、LAxi2Reg、CtmRAM、IdenRAM 和 FIFO。

如需進一步瞭解 NVMeG3-IP 公版設計,請參閱 Design Gateway 網站上的 NVMeG3-IP 公版設計文件。

圖 4:NVMeG3-IP 公版設計概覽。(圖片來源:Design Gateway)

圖 4:NVMeG3-IP 公版設計概覽。(圖片來源:Design Gateway)

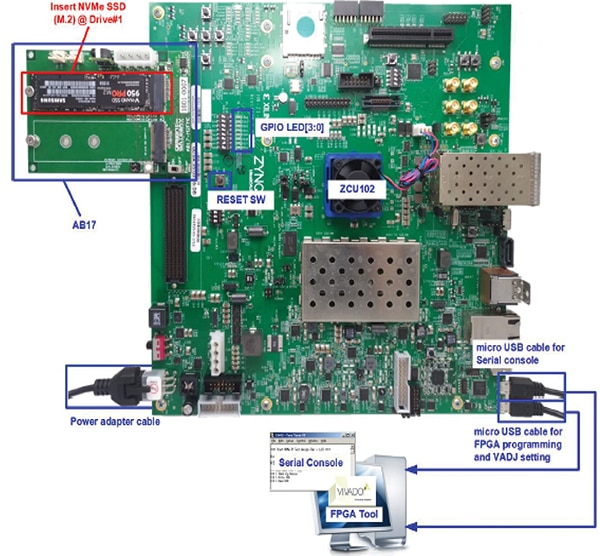

示範系統可使用 ZCU102 上的 NVMe SSD 寫入/驗證資料。使用者可透過序列控制台控制測試作業。為了讓 NVMe SSD 介接 ZCU102,需要一個 AB17-M2FMC 配接器板,如圖 5 所示。

圖 5:設置在 ZCU102 上的 NVMeG3-IP 示範環境。(圖片來源:Design Gateway)

圖 5:設置在 ZCU102 上的 NVMeG3-IP 示範環境。(圖片來源:Design Gateway)

使用 512 GB Samsung 970 Pro 時,在 ZCU102 上執行示範系統的範例測試結果如圖 6 所示。

圖 6:使用 Samsung 970 PRO S 時,ZCU102 上的 NVMe SSD 讀取/寫入效能。(圖片來源:Design Gateway)

圖 6:使用 Samsung 970 PRO S 時,ZCU102 上的 NVMe SSD 讀取/寫入效能。(圖片來源:Design Gateway)

結論

NVMeG3-IP 核心提供解決方案,可在 ZCU102 評估套件上啟用 NVMe SSD 介面;同時也針對沒有 PCIe 整合區塊的 Xilinx® Zynq® UltraScale+™ MPSoC 元件系列提供解決方案。NVMeG3-IP 的設計目標是在不使用 CPU 的情況下,以最低的 FPGA 資源使用量達到最高效能的 NVMe SSD 存取。該元件非常適合在無 CPU 介入下達到高效能 NVMe 儲存,並可運用 GTH 收發器實作多個 NVMe SSD 介面,不受 FPGA 元件上可用 PCIe 整合區塊數量的限制。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。