使用隔離來保持準確性並提升數據採集的效能

資料提供者:DigiKey 北美編輯群

2024-12-20

隨著智慧能力轉移到邊緣端以編撰小說並解決複雜問題,確保數據採集 (DAQ) 的可靠性、準確性和效能越來越重要。因此設計人員必須在採集的訊號和系統處理器之間提供隔離的精密訊號鏈。

確保精密類比訊號測量鏈中具有隔離,是一項有挑戰性的任務。為了維持訊號鏈的效能,除了要考量訊號破壞因素與無可避免的溫度漂移之外,還要特別注意細節。對於許多設計人員來說,在挑選和使用適當的隔離技術之前,最好先進一步瞭解涉及的問題。

本文將探討在開發高階隔離式 DAQ 系統並進行最佳化時,會遭遇的相關問題;此處所述的「高階」,是指具有精密度、準確度、訊號完整性和一致性等屬性。接著會介紹 Analog Devices 的 DAQ 訊號鏈解決方案,並展示如何用此建構這類系統。

各個功能模塊最佳化

典型的 DAQ 系統由一系列功能模塊組成,能讓訊號透過感測器從實體系統傳遞。接著就會傳輸到類比前端 (AFE) 進行訊號調節,再到類比數位轉換器 (ADC) 進行數位化,然後再到電腦式讀出器或控制器 (可能是微控制器到更大的系統) (圖 1)。

圖 1:DAQ 系統由定義良好的線性訊號鏈組成,從受測的實體系統與感測器到主機處理器都包括在內。(圖片來源:Bill Schweber)

圖 1:DAQ 系統由定義良好的線性訊號鏈組成,從受測的實體系統與感測器到主機處理器都包括在內。(圖片來源:Bill Schweber)

要達到 DAQ 的精度和準確度,首先要挑選前端訊號調節元件,尤其是傳感器前置放大器。低雜訊效能是此功能的眾多關鍵因素之一,因為內部雜訊在設計後期很難降低,而且會隨著所需訊號而放大。在此應建立基線訊噪比 (SNR),而且隨著訊號通過其他階段,不可避免地會進一步衰退。

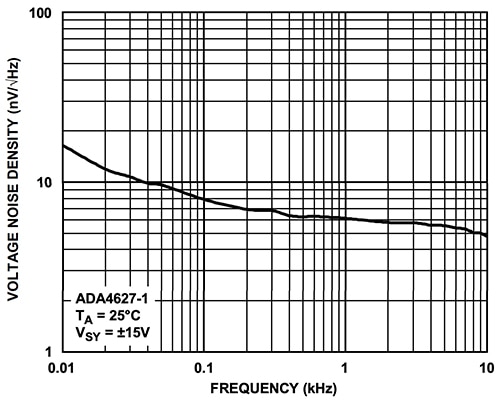

有鑑於此,AFE 通常會使用雜訊最佳化的單功能運算放大器。有個不錯的前端前置放大器選擇是 Analog Devices 的 ADA4627-1BRZ-R7,這是一款 30 V (±15 V 雙電源)、高速、低雜訊、低偏壓電流的 JFET 運算放大器。在其眾多感測器最佳化規格中,具有 200 μV (最大值) 的低偏移電壓、1 μV/°C (典型值) 的偏移漂移,以及 5 pA (最大值) 的輸入偏壓電流。在 1 kHz 時,臨界電壓雜訊規格為 6.1 nV/√Hz (圖 2)。

圖 2:ADA4627 JFET 運算放大器的電壓雜訊為 6.1 nV/√Hz (1 kHz)。(圖片來源:Analog Devices)

圖 2:ADA4627 JFET 運算放大器的電壓雜訊為 6.1 nV/√Hz (1 kHz)。(圖片來源:Analog Devices)

隔離帶來多重好處

訊號經過放大和數位化後,下一步就是在訊號與系統的數位區和相關處理器之間達到電流隔離。執行此步驟有三個主要原因:

- 降低雜訊和干擾:電流隔離可以消除共模電壓的變化、接地迴路和電磁干擾 (EMI)。還可以避免外部雜訊源破壞採集的訊號,確保更清晰、更準確的測量。

- 省去接地迴路:接地迴路會帶來電壓差,會導致測量訊號失真。隔離可斷開接地迴路的路徑,因此可消除接地電位變化引起的干擾,進而提升測量準確度。

- 安全與保護:隔離屏障可避免危險的電壓尖峰、暫態或突波抵達敏感的測量元件,藉此確保電氣安全。如此一來,就可保護測量電路和連接的裝置,確保安全可靠的運作。此外,如果低階感測器短暫接觸高壓或 AC 線路,這個屏障也可讓使用者避開電氣危險。

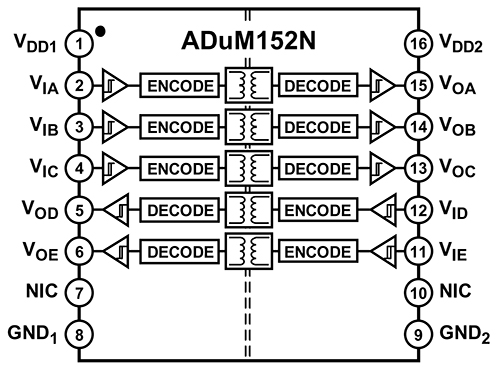

有幾種技術可依據磁性、光學、電容甚至 RF 原理的基礎,來實作數位訊號的隔離。Analog Devices 提供一系列高效能解決方案,包括以其專有 iCoupler 技術為基礎打造的 ADUM152N1BRZ-RL7 五通道數位隔離器 (圖 3)。

圖 3:ADuM152N 五通道數位隔離器採用專有的磁耦合實作方式達到高效能。(圖片來源:Analog Devices)

圖 3:ADuM152N 五通道數位隔離器採用專有的磁耦合實作方式達到高效能。(圖片來源:Analog Devices)

這些隔離器結合了高速 CMOS 與單晶片空心變壓器技術。為了確保效能可配合高速數位鏈路的需求,最大傳播延遲為 13 ns,5 V 時的脈寬失真小於 4.5 ns,傳播延遲的通道間匹配非常嚴格,為 4.0 ns (最大值)。也有提供類似的雙通道版本 ADUM120N1BRZ-RL7,因此隔離通道的總數可以匹配匯流排寬度。

這些隔離器經過最佳化,可達到高速效能,且保證達到 150 Mbps 的數據傳輸率。可提供 100 kV/μs 的高共模暫態耐受度 (CMTI),3 kVrms 的耐壓額定值,並符合所有相關法規要求。

訊號隔離只是整體隔離設計的一部分。DAQ 系統的所有 DC 電源軌也必須隔離。這通常會使用變壓器當作隔離元件來達成。

如果主電源已經是 AC,則會通過變壓器,然後進行整流和穩壓;如果電源是 DC,則須先截波成類似 AC 的波形。使用 LT3999 這類低雜訊、1 A、50 kHz 至 1 MHz 的 DC/DC 驅動器,就可大幅簡化過程。

完整的高效能 DAQ 系統需要額外的核心和週邊元件。在設計和佈局上必須確保準確的測量和資料完整性。除了放大器和隔離屏障外,精密的訊號鏈通常還含有濾波元件、高解析度 ADC 和交換器。這些元件組合在一起,就可消除雜訊、將干擾降至最低,並提供準確的訊號重現。

全部組成一體

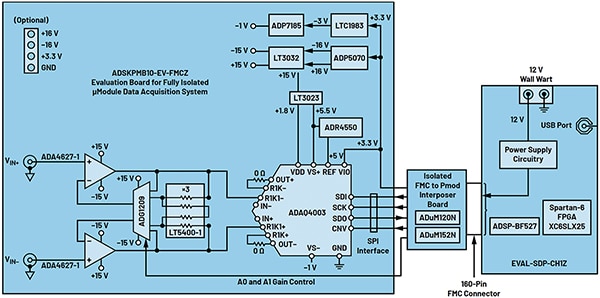

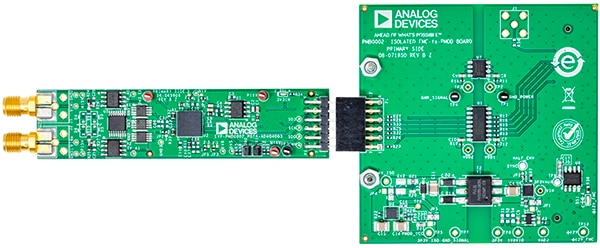

有個使用這些關鍵元件的隔離式訊號鏈範例就是 ADSKPMB10-EV-FMCZ,此精密平台可實作單通道、全隔離式、低延遲的 DAQ 系統 (圖 4)。此解決方案結合了訊號調節用的可編程增益儀表放大器 (PGIA),可配合多種感測器介面的靈敏度,且在緊湊的機板上具有數位與功率隔離。

圖 4:ADKSPMB10-EV-FMCZ 是一個精密平台,可實作單通道、全隔離式、低延遲的 DAQ 系統。PMOD 對 FMC 中介板 (中心模塊) 可提供隔離和其他功能。(圖片來源:Analog Devices)

圖 4:ADKSPMB10-EV-FMCZ 是一個精密平台,可實作單通道、全隔離式、低延遲的 DAQ 系統。PMOD 對 FMC 中介板 (中心模塊) 可提供隔離和其他功能。(圖片來源:Analog Devices)

為了進行評估,可配置成多板解決方案,含有 PMOD 外形尺寸的 ADSKPMB10-EV-FMCZ (圖 5) 和 EVAL-SDP-CH1Z 系統展示平台 (SDP) 介面板。在這兩塊板件之間有一個全隔離式 PMOD 對 FMC 中介板。

圖 5:ADSKPMB10-EV-FMCZ (左) 會透過 PMOD 對 FMC 中介板 (右) 連接到 SDP 介面板 (未顯示)。中介板上的垂直分割區指出隔離屏障的實作位置。(圖片來源:Analog Devices)

圖 5:ADSKPMB10-EV-FMCZ (左) 會透過 PMOD 對 FMC 中介板 (右) 連接到 SDP 介面板 (未顯示)。中介板上的垂直分割區指出隔離屏障的實作位置。(圖片來源:Analog Devices)

ADSKPMB10-EV-FMCZ 具有採用 ADA4627-1 運算放大器的離散式 PGIA 配置。PGIA 具有必要的高輸入阻抗,可支援與各種感測器的直接介接。此模組還具有用於增益設定的精密四通道匹配電阻網路、四通道多工器,以及用於 ADAQ4003 的全差動放大器 ADC 驅動器。ADAQ4003 是 18 位元、2 MSPS 的 ADC 和 DAQ 子系統,並以 μModule 的形式實作。

此模組不僅僅是高解析度 ADC。ADAQ4003 中結合了多種降低雜訊的技術,可促成高傳真度的訊號擷取。例如,在 ADC 驅動器輸出和 μModule 內部的 ADC 輸入之間放置一個單極、低通電阻電容 (RC) 濾波器,就可消除高頻雜訊,並可減少來自內部 ADC 輸入端的電荷「反沖」。

此外,μModule 的佈局可確保類比和數位路徑隔開以免交錯,並可將輻射雜訊降至最低。

全隔離式 PMOD 對 FMC 中介板含有 LT3999 DC/DC 驅動器、五通道和雙通道數位隔離器、低雜訊低壓降穩壓器 (LDO) 以及超低雜訊 LDO。此中介板可當作橋接器,連接到 SDP 介面板。

SDP 介面板可執行採集後的處理、管理和連接。此板件具有一個 160 引腳 FMC 連接器、一個 12 VDC 電源 (針對其他板件進一步穩壓和分區)、一個具有硬體式保全的 Blackfin 處理器 (用於程式碼和內容保護)、一個 USB 連接埠和一個 Spartan-6 FPGA。

用效能來證明

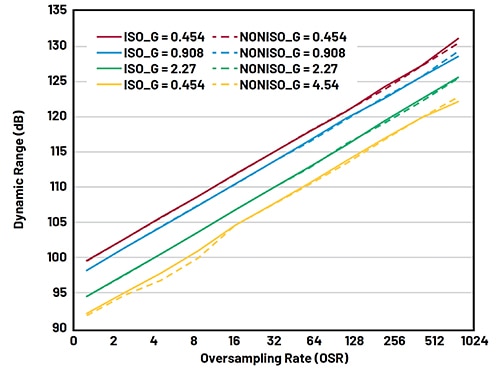

評估精密 DAQ 系統的效能並不容易,因為儀器、測試安排和指標都相當重要。雖然許多動態參數與 DAQ 系統的效能相關,但最明顯的是動態範圍、訊噪比 (SNR) 和總諧波失真 (THD)。

動態範圍是指裝置的背景雜訊與其指定最大輸出位準之間的範圍。

此設計的典型動態範圍在最高增益設定下為 93 dB,在最低增益設定下為 100 dB,表現令人驚艷 (圖 6)。將超取樣率提高到 1024 倍,就可進一步改善測量,分別達到最大值 123 dB 和 130 dB。

圖 6:整個電路和訊號鏈的動態範圍約為 100 dB,視增益和其他設定而定,也指出這是一款高效能的 DAQ 系統。(圖片來源:Analog Devices)

圖 6:整個電路和訊號鏈的動態範圍約為 100 dB,視增益和其他設定而定,也指出這是一款高效能的 DAQ 系統。(圖片來源:Analog Devices)

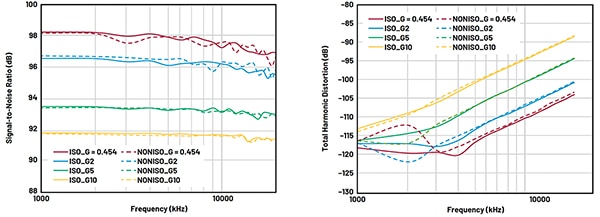

SNR 是指 rms 訊號幅度與其他所有頻譜分量 (不包含諧波和 DC) 的和方根 (RSS) 平均值的比值。THD 是基礎訊號的 rms 值與其諧波的 RSS 平均值的比值。

此設計的 SNR 和 THD 顯然具有高效能,因為訊號鏈的最大 SNR 可達到 98 dB (圖 7 左),THD 可達 -118 dB (圖 7 右),視增益設定而定。

圖 7:除了動態範圍,高 SNR (左) 和低 THD (右) 可進一步證明此 DAQ 效能的卓越程度。(圖片來源:Analog Devices)

圖 7:除了動態範圍,高 SNR (左) 和低 THD (右) 可進一步證明此 DAQ 效能的卓越程度。(圖片來源:Analog Devices)

結論

設計和實作隔離式精密訊號鏈時,必須保持準確度、將雜訊和干擾降至最低,並確保資料完整性,更是設計和實作時的重要關鍵。幸好,只要明智地使用精密放大、隔離技術、高解析度 ADC 和模組以及低雜訊電源管理就可達成,即使在電氣艱困的環境中也能達成。只要使用 Analog Devices 的進階元件就可達成,包括從基本的運算放大器到進階的隔離裝置等等,且更具有必要的週邊功能支援,更提供詳盡的規格書與應用指南。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。