設計精密數據採集系統時,如何節省空間和開發時間

資料提供者:DigiKey 北美編輯群

2022-03-16

越來越多工業自動化和醫療保健系統的設計人員採用先進的感測、偵測以及圖像和影片擷取技術,進行數位化和分析。然而,若要讓分析與輸入資料品質相當,其採集需仰賴高效能、高動態範圍、精密穩定的訊號調整和轉換模塊。使用離散電路方法設計這些模塊需大量設計資源、電路板空間、時間,所有這些都會增加總成本。

同時,設計人員需要確保其終端系統保持競爭力,這代表在確保優異效能的同時盡可能降低成本和加速上市時間。

本文簡要介紹一個典型的數據採集系統及其核心要素。接著介紹 Analog Devices Inc. 的數據採集 (DAQ) 模組,該模組整合許多關鍵元素,提供穩定的 18 位元、2 MS/s 的效能。還介紹評估板,協助設計人員熟悉該模組及使用方式。

數據採集系統的要素

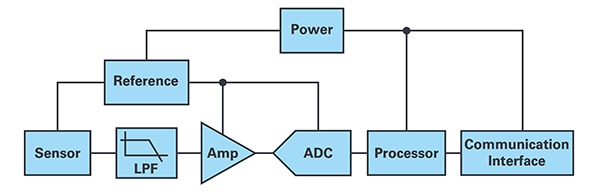

典型的數據採集系統如圖 1 所示。所需的訊號由感測器拾起,此感測器藉由回應某些物理現象輸出電子訊號。感測器的輸出可能是單端或差動,並且可能需要一些訊號調整,例如濾波。為了從類比數位轉換器 (ADC) 取得最大可能的動態範圍,必須放大訊號以匹配 ADC 的輸入電壓範圍。放大器增益和偏移通常由精密電阻控制,這些電阻必須考慮動態和溫度漂移並仔細匹配。溫度依賴性通常要求元件實體距離非常接近。動態條件包括必須最小化的雜訊和失真位準。

圖 1:典型 DAQ 系統從感測器採集數據,對其進行調節,最佳化施加於 ADC 的訊號幅度,並將數位資料傳送到系統處理器。(圖片來源:Analog Devices)

圖 1:典型 DAQ 系統從感測器採集數據,對其進行調節,最佳化施加於 ADC 的訊號幅度,並將數位資料傳送到系統處理器。(圖片來源:Analog Devices)

連續漸近暫存器 (SAR) ADC 必須具有足夠的動態範圍,由分辨率位元數表示。還需要一個緩衝、穩定和乾淨的參考電壓。

最後,必須通過通訊介面存取採集的數據。使用離散元件達成這樣的數據採集系統需要更多的實體空間,並且通常會導致效能比採用積體元件還差得多。例如,考慮到驅動 ADC 的差動放大器的效能要求,必須使放大器輸入兩端的輸入和回授電阻緊密匹配,因為任何不平衡都會降低共模拒斥比 (CMRR)。同樣地,輸入電阻必須與回授電阻精確匹配以設置級增益。這些電阻也必須追蹤溫度,要求位置相近。此外,整體電路佈局對於保持訊號完整性和最小化寄生響應非常重要。

整合式 DAQ 模組節省時間和空間

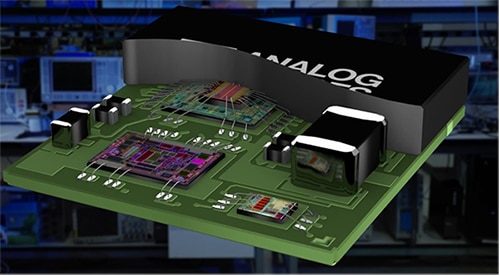

為了同時滿足縮減尺寸和設計時間的效能要求,設計人員可以運用 Analog Devices 的 ADAQ4003BBCZ µModule 系統級封裝 (SIP) 作為離散式實作的替代方案 (圖 2)。ADAQ4003 尺寸為 7 x 7 mm,專注於整合訊號鏈中最常見的部分,包括訊號調整和數位化,以提供先進效能的更完整訊號鏈解決方案。如此,即填補了標準離散元件和高度整合客戶指定 IC 之間的差距,解決數據採集需求。

圖 2:µModule SIP 的剖視圖,將多個常見的訊號處理模塊組合到一個單邊僅 7 mm 的元件中。(圖片來源:Analog Devices)

圖 2:µModule SIP 的剖視圖,將多個常見的訊號處理模塊組合到一個單邊僅 7 mm 的元件中。(圖片來源:Analog Devices)

ADAQ4003 結合一個執行速度高達 2 MS/s 的高解析度 18 位元 SAR ADC、一個低雜訊、全差動 ADC 驅動放大器 (FDA)、一個穩定的參考電壓緩衝器,以及所有必要的關鍵被動元件。其小型 49 觸點球柵陣列 (BGA) 封裝滿足緊湊的外形尺寸要求。

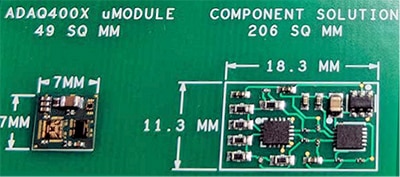

與圖 3 所示的離散佈局相比,ADAQ4003 的印刷電路板面積減少了四倍 (4x) 以上。

圖 3:與使用離散元件實作相同電路相比,去掉外殼的 ADAQ4003 (左) 佔用的表面積不到四分之一。(圖片來源:Analog Devices)

圖 3:與使用離散元件實作相同電路相比,去掉外殼的 ADAQ4003 (左) 佔用的表面積不到四分之一。(圖片來源:Analog Devices)

與離散式實作相比,µModule 有眾多優勢。更小的覆蓋區、元件在實體上更靠近,可達到更好的溫度追蹤,並減少由於引線電感和雜散電容引起的寄生效應。

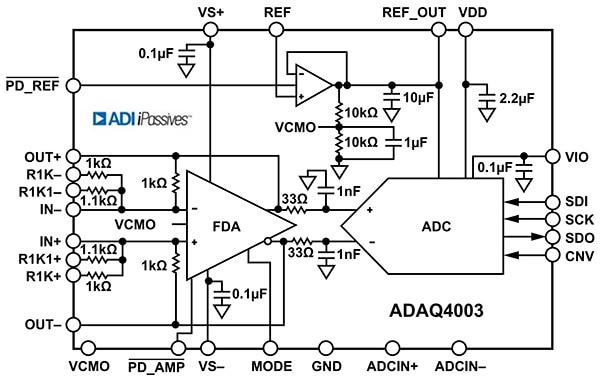

ADAQ4033 的功能方塊圖顯示每個數據採集系統中的四個關鍵組件 (圖 4)。

圖 4:ADAQ4003 的功能方塊圖顯示在 7 x 7 mm、49 觸點 BGA 封裝中的封裝量。(圖片來源:Analog Devices)

圖 4:ADAQ4003 的功能方塊圖顯示在 7 x 7 mm、49 觸點 BGA 封裝中的封裝量。(圖片來源:Analog Devices)

儘管實體尺寸很小,但 ADAQ4003 透過使用 ADI 的 iPassives 技術整合關鍵被動元件。整合式被動元件與多個被動網路同時在同樣的基板上製造。這些零件以極高的精密度製造。例如,電阻陣列元件的匹配度在 0.005% 以內。相鄰的元件間隔非常緊密,初始值匹配良好,絕對比離散被動元件優良。由於元件具備整合結構,在共用基板上實作的元件值在追蹤溫度、機械應力和壽命老化方面效能更佳。

如前所述,SAR 18 位元 ADC 的時脈頻率最高可達 2 MS/s,但作業時無漏失碼狀態。被動元件的精確值和匹配確保 ADC 的出色效能。在增益設置為 0.454 時,典型訊噪和失真 (SINAD) 比為 99 dB。其積分非線性通常為 3 ppm。輸入電阻陣列可以由引腳綁定,允許 0.454、0.909、1.0、1.9 的增益設置,讓輸入與 ADC 的滿量程範圍相匹配,進而最大化其動態範圍。關鍵組件的匹配導致在 0.454 增益範圍內的增益誤差漂移為 ±0.5 ppm/C°,偏移誤差漂移為 0.7 ppm/C°。

ADC 模塊前為 FDA 驅動器,在差動配置的所有增益範圍內,CMRR 為 90 dB。該放大器具有相當寬的共模輸入範圍,取決於特定的電路配置和增益設置。FDA 可以用作差動放大器,但也可以對單端輸入執行單端到差動轉換。

有一個單極 RC 濾波器,使用 FDA 驅動器和 ADC 之間的內部組件以差動方式實作。此設計用於限制 ADC 輸入的雜訊,並減少來自 SAR ADC 的電容數位類比轉換器 (DAC) 輸入的電壓回踢的影響。

ADAQ4003 還包含一個配置為單位增益的參考緩衝器,以最佳化驅動 SAR ADC 參考節點的動態輸入阻抗。還包括電壓參考節點和電源供應所需的所有去耦電容。這些去耦電容具有低等效串聯電阻 (ESR) 和低等效串聯電感 (ESL)。位於 ADAQ4003 內,進一步簡化物料清單 (BOM)。

ADAQ4003 的數位介面使用與 DSP、MICROWIRE 和 QSPI 相容的序列周邊介面 (SPI)。輸出介面使用獨立的 VIO 電源,與 1.8 V、2.5 V、3 V、5 V 邏輯相容。

ADAQ4003 以低總功耗運作,在 2 MS/s 的最大時脈速率下僅為 51.5 mW,並且在較低時脈速率下具有更低功耗。

ADAQ4003 的實體佈局有助於設計人員透過分離類比和數位訊號保持訊號完整性和效能。引腳分配上,左側為類比訊號,右側為數位訊號,允許設計人員隔離敏感的類比和數位部分,以盡量減少任何交叉。

電路模型

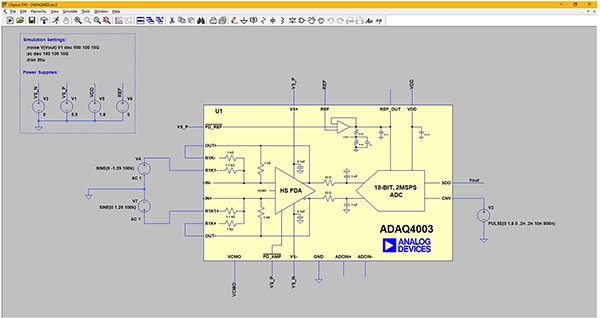

Analog Devices 提供模擬模型,在其免費的 LTspice 模擬器中為 ADAQ4003 提供模型,並製作 IBIS 模型,可用於其他商業電路模擬器。

LTspice 包括一個使用 ADAQ4003 的基本參考電路,如圖 5 所示。該元件用於差動輸入配置,輸入電阻透過串聯 1.0 和 1.1 kΩ 輸入電阻,將 FDA 增益設置為 0.454。模型參考電壓設置為 5 V,並使用 2 MS/s 轉換時脈。

圖 5:ADI 使用差動輸入配置為 ADAQ4003 提供可用的 LTspice 模擬模型。(圖片來源:Art Pini)

圖 5:ADI 使用差動輸入配置為 ADAQ4003 提供可用的 LTspice 模擬模型。(圖片來源:Art Pini)

LTspice 模型是任何可以使用評估板進一步驗證的設計的起點。

評估板

在考慮 ADAQ4003 時,明智的做法是使用 EVAL-ADAQ4003FMCZ 評估板來完成。此多板套件包括評估板和現場可編程陣列夾層卡。這些可與 Analog Devices 的 EVAL-SDP-CH1Z 系統示範平台搭配使用。ADI 還提供含產品特定附加元件的 分析/控制/評估 (ACE) 示範軟體,允許使用者執行詳細的產品測試,包括諧波分析以及積分和微分非線性測量。

結論

對於負責快速開發高效能 DAQ 系統、且需同時保持最低尺寸和成本的設計人員而言,ADAQ4003 µModule 是一個不錯的選擇。此元件消除了離散元件選擇、最佳化、佈局的訊號鏈設計挑戰,進一步縮短精密測量系統的開發週期。ADAQ4003 透過為單一組件提供最佳化、節省空間的數據採集解決方案作為客製化設計的基礎,進一步簡化設計過程。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。