使用鐵電記憶體提升汽車應用的可靠性

資料提供者:DigiKey 北美編輯群

2019-06-28

非揮發性記憶體 (NVM) 在幾乎每個嵌入式系統設計中都扮演著關鍵角色,但許多設計對非揮發性記憶體在資料寫入及存取速度、資料保留和低功率方面的要求越來越嚴格。這在汽車應用方面越來越明顯,設計人員正在尋求打造更先進的功能,比如關鍵任務型的先進駕駛輔助系統 (ADAS)。

為確保這些系統安全可靠地運作,設計人員需要更仔細瞭解進階的鐵電隨機存取記憶體 (F-RAM)。這是一種低功率的汽車級 NVM 選項,具有可靠、低功率,而且比目前 NVM 解決方案更快的特性。

本文將探討 F-RAM 技術的主要特點,並介紹開發人員如何使用 Cypress Semiconductor 的兩個 F-RAM 解決方案提高 ADAS 的可靠性,並在其他關鍵任務型應用中將 ADAS 當作 F-RAM 的使用代理。

汽車 NVM 需求

汽車產業逐漸整合更多解析度更高、更新率更快的先進感測器,而汽車安全應用是這波趨勢的寫照。ADAS、電子控制單元 (ECU)、事件資料記錄器 (EDR) 等汽車子系統持續不斷進化,並仰賴從廣泛感測器所收集到的大量資料集。只要稍微遺失資料,甚至資料存取的速度較慢,都可能會影響到系統安全性、汽車以及其乘客。

舉例來說,ADAS 設計中的電子抹除式可編程唯讀記憶體 (EEPROM),在依照所需的寫入時間進行寫入時,可能會延遲自動操控作業 (此作業是為了避開所感測到的危險而設計) 的時間,而這可能會帶來毀滅性的結果。在 EDR 設計中,假如汽車在發生事故時停電,緩慢的寫入速度可能會導致關鍵的感測器資料遺失,導致沒辦法透過資料瞭解事故的根本原因。

F-RAM NVM 特性

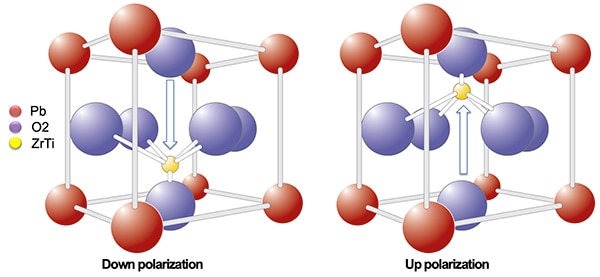

可靠的資料儲存與高速存取能力的需求增加,且相關的效能亦然,利用 F-RAM 技術打造的記憶體元件,能提供有效的 NVM 替代方案。這些元件是用鋯鈦酸鉛 (Pb[ZrxTi1−x]O3) 製成,也可以簡稱為 PZT。PZT 擁有獨特的特性,即內嵌於 PZT 水晶中的金屬空缺 (陽離子),會有「上」或「下」的極化狀態,依循著外加電場的方向 (圖 1)。

圖 1:PZT 材料在電場下呈現出兩個一樣穩定的能源狀態,而 F-RAM 技術運用這兩個狀態。(圖片來源:Cypress Semiconductor)

圖 1:PZT 材料在電場下呈現出兩個一樣穩定的能源狀態,而 F-RAM 技術運用這兩個狀態。(圖片來源:Cypress Semiconductor)

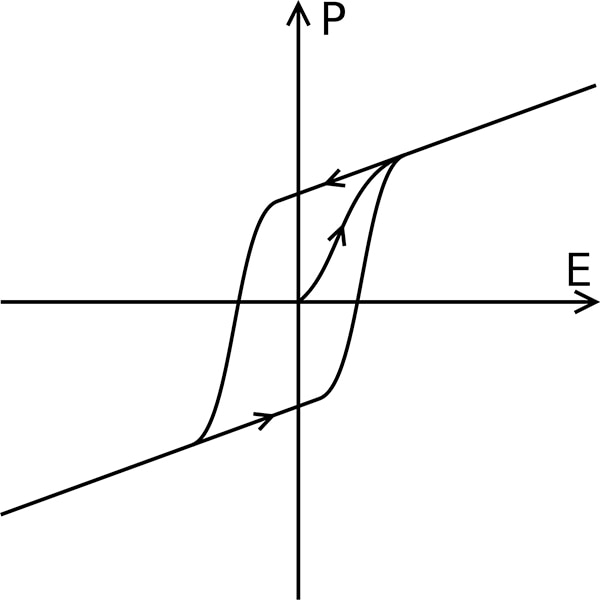

由於兩個都是同樣低能量的狀態,因此當移除電場時,陽離子會持續固定在其最近的極化狀態下 (圖 2)。一施加正電場或負電場時,陽離子會再次快速轉換到適當的極化狀態,依循著與鐵磁材料中類似的特徵磁滯迴圈。

圖 2:在兩種穩定極化狀態間切換,以對外加的電場作出回應時,PZT 材料會依循特徵磁滯迴圈。(圖片來源:WikiMedia Commons/ CC-BY-SA-3.0)

圖 2:在兩種穩定極化狀態間切換,以對外加的電場作出回應時,PZT 材料會依循特徵磁滯迴圈。(圖片來源:WikiMedia Commons/ CC-BY-SA-3.0)

F-RAM 技術的特性,為運用此技術製造的 NVM 元件直接帶來許多優勢。由於兩種 PZT 能量狀態都一樣穩定,因此陽離子能維持在最後的位置長達數十年,甚至可能長達數百年,讓 PZT 型 F-RAM NVM 元件達到前所未有的資料保留率。此外,由於此技術是以陽離子的位置 (而不是以其他 NVM 技術的電荷儲存機制) 為基礎,因此 F-RAM 元件本身可承受輻射,也不會受游離輻射造成的單粒子翻轉事件影響。

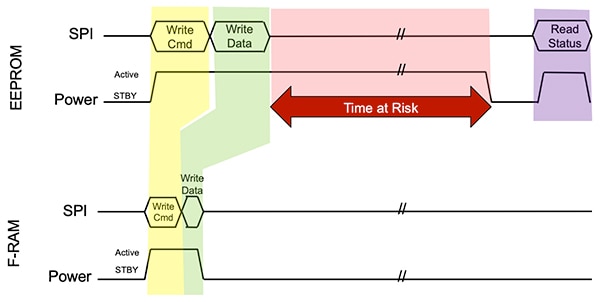

除了具有長時間存放的優點,F-RAM 還強化 NVM 元件的動態效能。狀態的轉換非常迅速,而且只需很少的能源,克服了在任務關鍵性應用中使用 EEPROM 或快閃記憶體時所面臨的基本限制。在相對緩慢的寫入週期中,EEPROM 和快閃元件在資料緩衝方面需要大量的「預備時間 (soak time)」。經過這個額外的寫入週期延遲後,資料可能會面臨風險,假如在作業還沒完成最終讀取狀態檢查前發生停電,資料還可能完全遺失 (圖 3)。

圖 3:EEPROM 或快閃寫入作業期間需要大量的預備時間 (紅色部分),造成資料有很長一段時間一直處於風險之中,F-RAM 元件則不會。(圖片來源:Cypress Semiconductor)

圖 3:EEPROM 或快閃寫入作業期間需要大量的預備時間 (紅色部分),造成資料有很長一段時間一直處於風險之中,F-RAM 元件則不會。(圖片來源:Cypress Semiconductor)

為了應付 EEPROM 或快閃記憶體較緩慢的寫入週期,開發人員若是希望降低停電的影響,則需要增添大型的電容或電池以及適當的穩壓器,讓 NVM 供應電壓維持足夠長的時間,以便完成寫入作業。相較之下,Cypress Semiconductor 的 Excelon-Auto 元件等 F-RAM,在寫入作業期間能以匯流排的速度運作,大幅減少關鍵資料的遺失量,並且無需在設計中使用輔助電源。

汽車級 F-RAM 元件

Excelon™-Auto F-RAM 元件在功能上與序列 EEPROM 和序列快閃記憶體相似,能符合關鍵任務型應用對高效能可靠 NVM 的需求。汽車系統設計人員可使用這些獲得 AEC-Q100 認證的元件來取代其他記憶體類型,可選擇 CY15V102QN (用於 1.71 至 1.89 V 供應電壓) 或 CY15B102QN (用於 1.8 至 3.6 V 供應電壓)。兩者皆為 2 Mbit 元件,邏輯上組織為 256 Kbit x 8。

在 -40°C 至 +125°C 工作溫度範圍中,Excelon F-RAM 擁有的資料保留率遠遠優於其他 NVM 技術。舉例來說,CY15x102QN 在 85°C 下作業時,資料預計能保留 121 年。由於資料保留與溫度呈反比,因此如果被迫要在較高的典型引擎溫度下作業 (像是 95°C),F-RAM 預計能保留資料 35 年。

在可靠性部分,F-RAM 能讀取/寫入週期耐久性為 1013 次,這大約是一般典型 EEPROM 或快閃記憶體的七倍。因此,採用這些 F-RAM 元件的開發人員,不需要實行平均抹寫等技術 (平均抹寫技術會為扇區分配寫入,以處理其他 NVM 技術寫入次數有限的問題)。

採用 F-RAM 的簡化設計

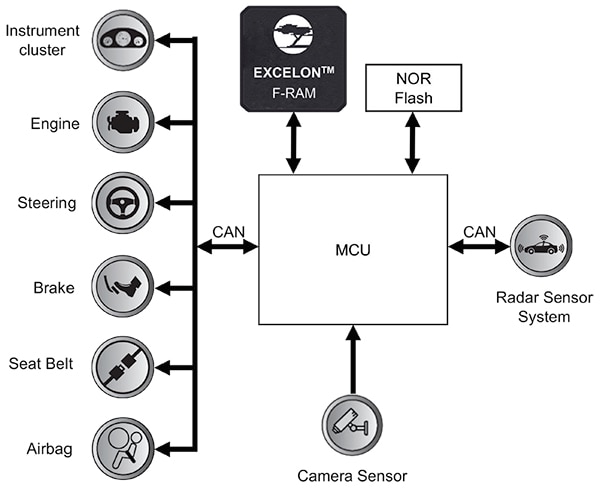

在典型的設計中,開發人員可使用這些元件來直接取代或補足其他類型的 NVM 元件,例如 NOR 快閃記憶體。舉例來說,在 ADAS 設計中,開發人員可能會將用來儲存韌體的 NOR 快閃元件與 Excelon F-RAM 結合;而 Excelon F-RAM 能從許多為 ADAS 應用提供輸入的汽車子系統,可靠地處理多個資料串流 (圖 4)。

圖 4:汽車 ADAS 開發人員能在微控制器 (MCU) 型設計中,將用來儲存關鍵資料的 Excelon F-RAM 元件,與常用來儲存韌體或設定資料的 NOR 快閃元件進行結合。(圖片來源:Cypress Semiconductor)

圖 4:汽車 ADAS 開發人員能在微控制器 (MCU) 型設計中,將用來儲存關鍵資料的 Excelon F-RAM 元件,與常用來儲存韌體或設定資料的 NOR 快閃元件進行結合。(圖片來源:Cypress Semiconductor)

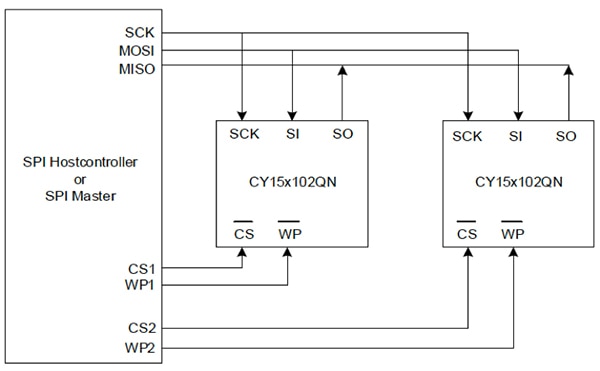

開發人員可輕鬆將 Excelon F-RAM 置入設計中,只要將其連接到主機處理器的序列周邊裝置介面 (SPI) 匯流排即可。CY15x102QN F-RAM 是當作 SPI 從屬元件來運作,可支援高達 50 MHz 的 SPI 時脈率。在一般典型的硬體設定中,開發人員會將 F-RAM 的序列輸入 (SI) 和序列輸出 (SO),連接到各自對應的 SPI 主控裝置的主控輸出從屬輸入 (MOSI) 和主控輸入從屬輸出 (MISO) 線。然後分別連接到序列時脈 (SCK) 與晶片選擇單元 (/CS) 線路後,硬體介面就完成了。開發人員可結合多個元件來共用主機的 SPI 匯流排 (圖 5)。

圖 5:開發人員可使用共用的 SPI 匯流排,將主機處理器與一個或多個 CY15x102QN F-RAM 連接起來。(圖片來源:Cypress Semiconductor)

圖 5:開發人員可使用共用的 SPI 匯流排,將主機處理器與一個或多個 CY15x102QN F-RAM 連接起來。(圖片來源:Cypress Semiconductor)

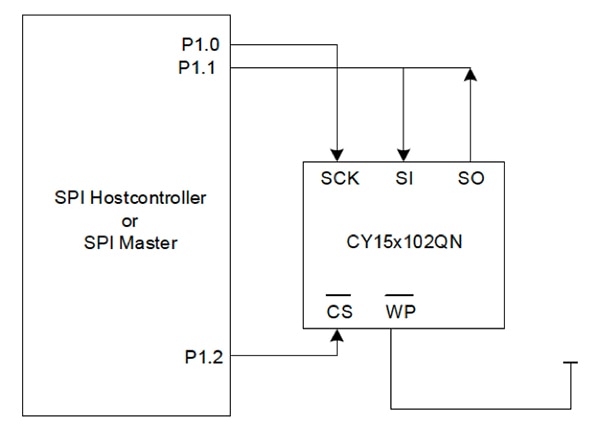

對於沒有 SPI 能力的 MCU,CY15x102QN 元件能讓人經由另一種簡單的方式來模擬 SPI 硬體介面,即使用微控制器的一般用途 IO (GPIO) 來連接到 F-RAM。開發人員透過為 F-RAM 的 SI 和 SO 數據線使用相同的引腳,只要使用三個 GPIO 就能實作這個介面 (圖 6)。

圖 6:對於沒有原生 SPI 能力的微控制器,開發人員僅需使用微控制器的一般用途 IO 來模擬 SPI 協定,以存取 CY15x102QN 序列 F-RAM。(圖片來源:Cypress Semiconductor)

圖 6:對於沒有原生 SPI 能力的微控制器,開發人員僅需使用微控制器的一般用途 IO 來模擬 SPI 協定,以存取 CY15x102QN 序列 F-RAM。(圖片來源:Cypress Semiconductor)

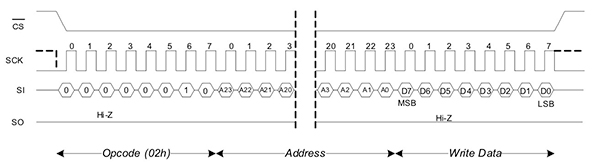

在標準 SPI 協定中,主控裝置會藉由拉低 /CS 來啟動交易。/CS 降低之後,F-RAM 會將下個位元組詮釋為運算碼。舉例來說,寫入作業會遵循 SPI 標準寫入運算碼 (02h),搭配三位元組的位址與資料位元組 (圖 7)。

圖 7:Cypress 的 CY15x102QN F-RAM 元件支援標準 SPI 運算碼以及協定,開發人員透過依序傳送寫入運算碼 (02h)、位址和資料,便能輕鬆地執行零延遲的寫入。(圖片來源:Cypress Semiconductor)

圖 7:Cypress 的 CY15x102QN F-RAM 元件支援標準 SPI 運算碼以及協定,開發人員透過依序傳送寫入運算碼 (02h)、位址和資料,便能輕鬆地執行零延遲的寫入。(圖片來源:Cypress Semiconductor)

對於 2 Mbit CY15x102QN F-RAM,位址是個三位元組的序列,並忽略上方六個位元。Cypress 建議將這些上方六個位元設定為零,以便未來可輕鬆轉換成容量更高的 F-RAM 元件。

讀取作業也遵循相同的協定。接收到標準讀取運算碼 (03h) 和位址後,F-RAM 元件會依序在 SO 上傳送資料位元組,自動增加記憶體位址,同時 /CS 也會維持低位準且時脈訊號會繼續作用。因此,開發人員可以執行批次讀取,只需將 /CS 保持在低位準並持續發出 SCK 時脈訊號,直至讀取所需的資料位元組數目。

CY15x102QN F-RAM 也支援與序列快閃記憶體相容的快速讀取特點。在快速讀取運算碼 (0Bh) 和位址之後,SPI 主機會傳送虛位元組以模擬快閃讀取延遲。在接收到虛位元組後,F-RAM 會提供所要求的資料來作出回應。快速讀取作業也能使用和標準讀取一樣的機制來執行批次讀取。

寫入保護

除了 SPI 介面控制邏輯,CY15x102QN F-RAM 提供了額外的機制,可辨別元件以及寫入保護 F-RAM 陣列。

開發人員可以發佈 SPI 運算碼來存取 CY15x102QN 元件唯讀的唯一 ID 和元件 ID,其提供製造商、記憶體密度和零件版本等資訊。開發人員還可以設定 8 位元組的讀/寫序號暫存器,以將 F-RAM 與特定的系統或設定進行關聯。

為了保護 F-RAM,該元件提供軟體機制和硬體機制。在製造期間的資料保護方面,256 位元組的專用特殊扇區,能透過多達三個標準迴流焊接循環來維護資料的完整性。為了在正常操作期間能提供保護,元件使用寫入啟用閂鎖 (WEL) 來避免 F-RAM 陣列發生意外寫入。供電時,會預設清除 WEL,因此開發人員必須在執行寫入操作之前發出寫入啟用 (WREN) 運算碼 (06h)。

在元件狀態暫存器中,BP0 和 BP1 這對區塊保護 (BP) 位元,讓開發人員能只在記憶體的上半部分 (BP1=1,BP0=0),或只在記憶體的上四分之一 (BP1=0,BP0=1),在整個位址範圍內保護記憶體 (BP1=1,BP0=1)。

開發人員可以使用硬體寫入保護引腳 (/WP),避免軟體在正常操作期間修改 BP 位元。為此,開發人員在狀態暫存器中設定寫入保護啟用 (WPEN) 位元,並將 /WP 引腳設為低位準來鎖定狀態暫存器。

電源管理

在正常操作中,F-RAM 技術中固有的能效,通常讓 CY15V102QN (VDD 1.71 至 1.89 V) 在執行時脈速率最高 50 MHz 的作業時,僅僅只耗電 5.0 mA。開發人員可以降低時脈頻率以進一步節省電能,將 CY15V102QN 的電流消耗量降低到 1 MHz 時只有 0.4 mA 左右。CY15B102QN 的電流消耗量 (VDD 1.8 至 3.6 V),在 50 MHz 時為 6.0 mA,在 1 MHz 時為 0.5 mA,都只有高出一點點。

長時間閒置時,開發人員可使用 SPI 運算碼將 CY15x102QN 元件設定為三種低功率模式,顯著降低功耗:

- 待機模式 - CY15V102QN 的典型電流消耗量為 2.7 μA,CY15B102QN 的典型電流消耗量為 3.2 μA

- 深度斷電模式 - CY15V102QN 為 1.1 μA,CY15B102QN 為 1.3 μA

- 休眠模式 - 這兩者都是 0.1 μA

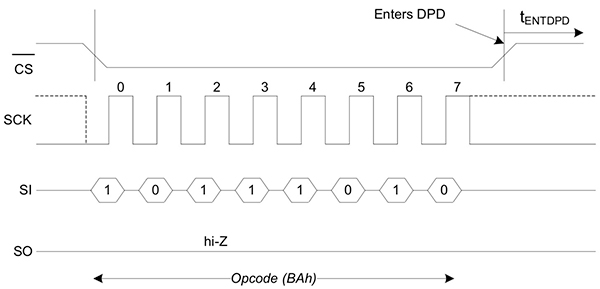

每當 SPI 主機在運算碼序列結束時將 /CS 設為高位準,CY15x102QN 元件就會自動切換到待機模式。如欲將元件切換到深度斷電或休眠模式,SPI 主機使用 SPI 運算碼協定來進行。具體來說,SPI 主機會先將 /CS 設為低位準,然後傳送一個特殊運算碼以用於深度斷電 (BAh) 或休眠 (B9h),最後將 /CS 設為高位準,藉此切換到兩種最低功率模式的其中一種 (圖 8)。

圖 8:雖然 CY15x102QN F-RAM 元件會在運算碼序列後自動進入待機模式,但開發人員可以使用正常的 SPI 運算碼程序讓該元件進入功率更低的模式,例如深度斷電 (DPD) 模式。(圖片來源:Cypress Semiconductor)

圖 8:雖然 CY15x102QN F-RAM 元件會在運算碼序列後自動進入待機模式,但開發人員可以使用正常的 SPI 運算碼程序讓該元件進入功率更低的模式,例如深度斷電 (DPD) 模式。(圖片來源:Cypress Semiconductor)

當 SPI 主機在傳送適當的低功率運算碼後將 /CS 設為高位準時,CY15x102QN F-RAM 會在大約 3 μs 內進入所要求的低功率模式。

在待機模式下,當 /CS 變為低位準時,Cypress F-RAM 會立即返回主動模式,以啟動下一個運算碼序列。從深度斷電模式或休眠模式中,F-RAM 在 /CS 變為低位準後也會返回主動模式,但深度斷電模式會有大約 10 μs 的延遲,休眠模式則為 450 μs。

結論

感測器種類越來越多,對許多仰賴其資料的應用來說,可靠、快速、低功率且高效能的 NVM 變得越來越重要。在任務關鍵型領域 (如汽車 ADAS 應用) 中,遺失資料會大大損及為保護汽車及乘客所設計的安全機制。

使用 Cypress Semiconductor 的 F-RAM 元件,開發人員可以輕鬆地新增 NVM,該元件能在不犧牲效能或低功率要求的情況下,可靠地儲存關鍵資料數十年。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。