使用 F-RAM 打造具有超低功率長期儲存功能的電池供電裝置

資料提供者:DigiKey 北美編輯群

2019-12-11

在消費性、工業及其他細分市場中,長期可靠的資料儲存功能,對電池供電的行動裝置日趨重要。較早世代的產品依賴傳統的非揮發性記憶體 (NVM) 技術,例如快閃記憶體或電子抹除式可編程唯讀記憶體 (EEPROM),滿足這一需求。

然而,對於今天的先進行動產品,使用者不斷期望有更長的電池續航力。在不折損設計效能或功率預算下,這樣的趨勢已大大限制了可提供可靠儲存功能的選項。

本文將介紹 Cypress Semiconductor 的 Excelon 鐵電隨機存取記憶體 (F-RAM) 系列,並說明如何使用該產品滿足電池供電裝置對長期可靠儲存功能的需求。

可攜式裝置的儲存空間挑戰

在設計穿戴式裝置、IoT 裝置和其他可攜式產品時,由於這些產品的功能不斷增加,對大型非揮發性儲存空間的需求也就水漲船高。使用者渴望獲得更全面的資訊,因此這些設計需要整合更多解析度更高且更新速率更快的感測器。與此同時,使用者期望這些高精密產品能夠提供廣泛的歷史資料和相關趨勢,而不是目前感測器資料的簡單快照。尤其希望裝置必須能夠按需產生這類資料,而無需與雲端、智慧型手機或其他外部裝置連線。

想要以傳統 NVM 技術滿足上述基本需求的設計人員,會面臨多重困難,特別是在功率有限的設計中。許多 NVM 技術的寫入時間,本身就比 RAM 慢上許多,這是因為需要額外的週期時間,才能完成編程過程;傳統 EEPROM 的寫入時間達數毫秒之久。即便是先進的快閃記憶體,其效能也會因寫入週期需要額外的「預備時間」而受到拖累。而較長的寫入週期意味著整體電流消耗量增加以及資料更新率變慢。最後,傳統 NVM 元件的寫入耐久性規格通常都是有限的。如果需要進行重複寫入來存儲例行資料,則這些元件可能還未到產品壽命即已報廢。

對於不斷增多的電池供電設計,F-RAM NVM 元件提供更簡便的長期儲存解決方案,可在速度、耐久性和低功耗運作上,提供所需的組合優勢。典型的 F-RAM 元件具有比 EEPROM 和快閃記憶體高好幾個數量級的寫入耐久性和寫入週期時間,在速度上甚至接近靜態 RAM (SRAM)。實際上,F-RAM 兼具傳統 RAM 的效能優勢以及其他 NVM 技術的非揮發性儲存能力。在 F-RAM 解決方案中,Cypress Semiconductor 的 Excelon LP (低功率) F-FRAM 系列更勝一籌,能夠滿足電池供電穿戴式裝置及其他行動產品對超低功耗的基本要求。

超低功率 F-RAM

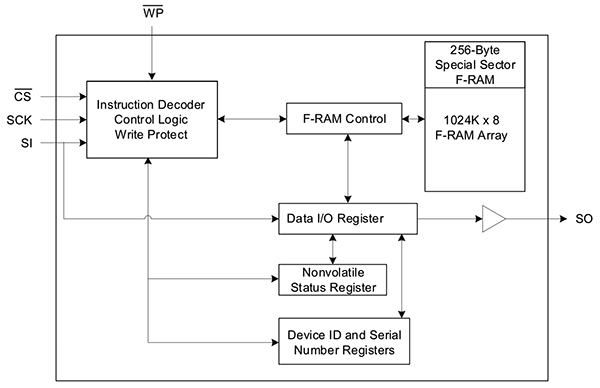

Cypress 的 Excelon LP F-RAM 元件是款整合式非揮發性記憶體子系統,內含 F-FRAM 陣列、暫存器、控制與介面邏輯,以及一個特殊的扇區,能透過多達三個標準迴流焊接循環來保存內容 (圖 1)。

圖 1:Cypress Semiconductor 的 Excelon LP F-RAM 元件整合了 F-RAM 陣列和支援電路,能提供可透過標準 SPI 連接埠存取的完整記憶體子系統。(圖片來源:Cypress Semiconductor)

圖 1:Cypress Semiconductor 的 Excelon LP F-RAM 元件整合了 F-RAM 陣列和支援電路,能提供可透過標準 SPI 連接埠存取的完整記憶體子系統。(圖片來源:Cypress Semiconductor)

Excelon LP F-FRAM 元件提供的長期可靠性水平遠遠超過典型的 EEPROM 或快閃記憶體。這些元件具有 1015 讀取/寫入週期耐久性和 151 年資料保留能力,超過了任何實用性穿戴式裝置或 IoT 裝置的實際生命週期。

此外,這些元件的寫入效能也強化了應用的整體可靠性。由於這些元件能以匯流排的速度,將資料寫入非揮發性 F-RAM 陣列,因此與其他類型的 NVM 元件相比,可大幅降低資料遺失的機率。對於其他類型的 NVM 元件而言,寫入時間大幅增加,內部資料相應需要緩衝,因此會產生一個相當長且可能發生漏洞的時段。如果在寫入序列完成之前發生停電,資料就會遺失。

不同於其他的 NVM 技術,Excelon LP F-FRAM 元件能以所需的最低電流位準工作,延長可攜式產品的電池續航力。Cypress 的 CY15x108QI 8 Mb F-RAM LP 系列的工作頻率為 20 MHz,僅消耗 1.3 mA 電流;而 Cypress 的 CY15x104QI 4 Mb F-RAM LP 系列則僅消耗 1.2 mA 電流。如後文更詳細的討論,這些元件還能為開發人員提供多種選項,進一步降低電流消耗量。

Excelon LP 系列產品旨在支援多種系統需求,可滿足商用與工業用途的溫度範圍,以及不同的電源供應器電壓。例如,4 Mb CY15V104QI 和 8 Mb CY15V108QI 的工作電壓範圍為 1.71 V 至 1.89 V,而 4 Mb CY15B104QI 和 8 Mb CY15B108QI 的工作電壓範圍為 1.8 V 至 3.6 V。

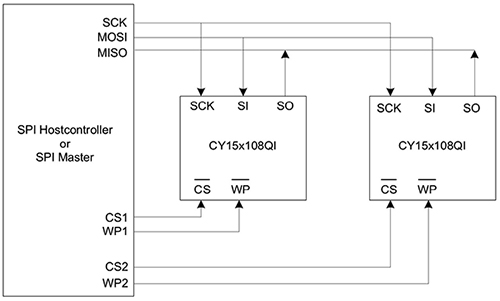

簡化系統設計

這些元件不但可以確保滿足不同應用的運作要求,還可簡化系統設計。在典型的設計中,開發人員將使用序列週邊裝置介面 (SPI) 匯流排,將一個或多個 Excelon LP F-RAM 元件作為 SPI 從屬元件連接到 SPI 主控元件,如微控制器 (圖 2)。

圖 2:開發人員只需將一個或多個 Cypress Semiconductor 的 Excelon LP F-RAM 元件連接到由微控制器等 SPI 主控元件控制的 SPI 匯流排,即可為其設計加入長期的儲存功能。(圖片來源:Cypress Semiconductor)

圖 2:開發人員只需將一個或多個 Cypress Semiconductor 的 Excelon LP F-RAM 元件連接到由微控制器等 SPI 主控元件控制的 SPI 匯流排,即可為其設計加入長期的儲存功能。(圖片來源:Cypress Semiconductor)

通過互連的 SPI 匯流排進行的交易,既簡單又快速。不像前面所提到的快閃記憶體或 EEPROM 技術,Excelon LP F-RAM 元件可以在沒有額外寫入延遲的情況下寫入記憶體。每個位元透過 SPI 匯流排抵達元件後會立即寫入 F-RAM 陣列,因而能大幅降低因突然停電而造成的資料遺失風險。

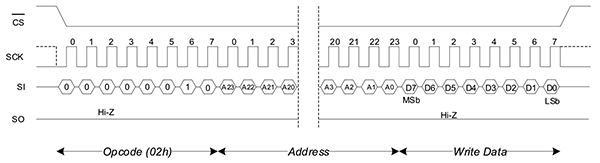

對系統開發人員來說,寫入程序遵循簡單 SPI 協定,其中涉及行業標準 SPI 運算操作碼 (opcode)。主機處理器會透過傳輸寫入啟用 (WREN) 操作碼 (06h),同時先提升然後再降低晶片選擇 (ØCS) 線的電位準,藉此開始每個寫入序列。經過這個簡短的初始化階段後,主機處理器會傳輸寫入操作碼 (02h),然後再傳輸 24 位元位址,開始寫入作業。(在這些元件中,位址的高四位元組會被忽略,但可確保與未來密度更高的 F-RAM 元件相容。)傳送位址之後,主機處理器可立即開始傳輸資料位元組 (圖 3)。

圖 3:在標準 SPI 寫入序列中,Cypress Semiconductor 的 Excelon LP F-RAM 元件會立即將資料寫入 F-RAM 陣列,完全沒有早期 NVM 技術所發生的緩衝或預備時間延遲。(圖片來源:Cypress Semiconductor)

圖 3:在標準 SPI 寫入序列中,Cypress Semiconductor 的 Excelon LP F-RAM 元件會立即將資料寫入 F-RAM 陣列,完全沒有早期 NVM 技術所發生的緩衝或預備時間延遲。(圖片來源:Cypress Semiconductor)

當主機處理器傳送資料位元組時,只要主機處理器將 ØCS 線保持為低電位準,並持續傳輸時脈訊號,F-RAM 元件即會在內部自動累加位址。因此,設計人員可將 Excelon LP F-RAM 元件用於需要任意組合單位元組寫入和區塊寫入的設計中。

讀取作業會遵循類似的 SPI 協定。在降低 ØCS 電位準之後,主機處理器會傳輸讀取操作碼 (03h) 和 24 位元位址。Excelon LP F-RAM 元件會使用每個 SCK 時脈週期在 SO 線上傳輸資料位元組,立即做出回應。與寫入作業一樣,只要主機處理器將 ØCS 維持在低電位準,並持續傳送 SCK 時脈,讀取作業便會繼續。

延長電池續航力

除了系統設計要求簡單外,這些低功率 F-RAM 還可為開發人員提供了降低電流消耗量和延長電池續航力的選項。Cypress 的 CY15x10xQI 元件專為電池供電應用而設計,其中整合了內建的湧入電流控制電路,可減少通常在 NVM 元件上電期間所產生的相對較大的電流。

Cypress 的 Excelon LP F-RAM 元件還允許開發人員採用不同的策略來延長穿戴式裝置和 IoT 設計的電池續航力,這些設計會使用感測器來追蹤進展速度相對緩慢的真實事件。在這些設計中,Cypress 的 Excelon LP F-RAM 元件通常能以較低的時脈頻率工作,從而降低電流消耗量。例如,以 1 MHz 的時脈工作時,8 Mb CY15V108QI 的電流消耗量會從 20 MHz 時的 1.3 mA 下降到 300 µA。同樣,4 Mb CY15V104QI 在 1 MHz 時僅需 200 µA,而在 20 MHz 下時則需要 1.2 mA。

開發人員可使用 Excelon LP F-RAM 元件所提供的特殊低功率模式,在穿戴式裝置與 IoT 應用定期發生的各個閒置時段,進一步將系統功耗降到最低。這些 F-RAM 元件支援三種低功率模式,允許開發人員以回應時間為代價來降低電流消耗量。

每當提高 ØCS 電位準以終止 SPI 序列時,這類元件會自動進入第一個低功率模式,即待機模式。而當降低 ØCS 電位準以開始新的 SPI 序列時,元件會自動退出待機模式。在待機模式下,8 Mb CY15V108QI Excelon LP F-RAM 僅消耗 3.5 µA,而 4 Mb CY15V104QI 僅消耗 2.3 µA。

待機模式可立即自動降低電流,而無需額外的延遲即可返回正常主動模式。然而,對於閒置時間較長的應用,即便是這種電流消耗,從長遠來看也會不可避免地降低電池續航力。針對這些情況,Excelon LP F-RAM 元件提供了兩個額外的低功率模式,即深度省電模式和休眠模式。

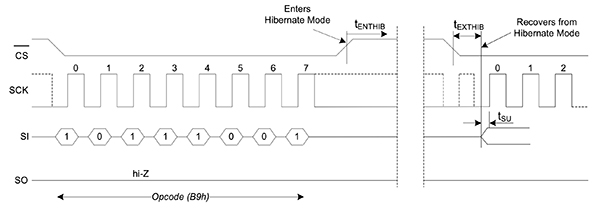

與預設的待機模式不同,深度省電模式和休眠模式皆通過使用特殊 SPI 操作碼明確進入。SPI 主控元件會發出深度省電 (DPD) 操作碼 (BAh) 或休眠 (HBN) 操作碼 (B9h),命令 F-RAM 元件進入相應的低功率模式 (圖 4),整個過程與讀取和寫入 SPI 作業類似。

圖 4:開發人員可使用標準 SPI 協定,將 Cypress Semiconductor 的 Excelon LP F-RAM 元件置於深度省電模式 (DPD) 或休眠模式 (HIB),這會大幅降低電流消耗量,但會在進入 (tENTxxx) 和退出 (tEXTxxx) 相應的低功率模式時引發不同的延遲。(圖片來源:Cypress Semiconductor)

圖 4:開發人員可使用標準 SPI 協定,將 Cypress Semiconductor 的 Excelon LP F-RAM 元件置於深度省電模式 (DPD) 或休眠模式 (HIB),這會大幅降低電流消耗量,但會在進入 (tENTxxx) 和退出 (tEXTxxx) 相應的低功率模式時引發不同的延遲。(圖片來源:Cypress Semiconductor)

這些低功率模式的影響非常大,電流消耗量可降至 1 µA 以下 (表 1)。雖然能大幅降低元件電流,但這些模式也會給對時間敏感的資料作業帶來不利影響。以操作碼為基礎的 DPD 和 HIB 低功率模式會帶來額外延遲,這些延遲與進入模式 (tENTDPD 或 tENTHIB) 和退出模式 (tEXTDPD 或 tEXTHIB) 所需的時間存在關聯性 (表 1 和圖 4)。

|

表 1:Excelon LP F-RAM 功率模式的電流消耗量,以及與進入 (tENTDPD 或 tENTHIB) 或退出 (tEXTDPD 或 tEXTHIB) 以操作碼為基礎的深度省電及休眠模式相關的延遲。這些數字來自商用型低電壓版產品,電源供應範圍為 1.71 V 至 1.89 V,工作溫度範圍為 0°C 至 +70°C。(資料來源:Cypress Excelon LP F-RAM 規格書)

使用以操作碼為基礎的低功率模式時,開發人員需要將這些模式可降低電流消耗量的優點,與進入和退出這些模式時所需耗用的電流及時間作比較,並在兩者之間作出權衡。任何會長期處於閒置時段的系統,都可能適合這兩種模式,但是具體選擇何種模式將主要依賴於 F-RAM 元件在主動時段運作的預期工作週期。對於需要以高工作週期運作的 F-RAM 元件,重複進入和退出低功率模式,可能會起反效果。舉例來說,Cypress 建議任何閒置時段達到 10 秒或 10 秒以上的應用,都非常適合休眠模式。

結論

由於電池供電穿戴式裝置和 IoT 裝置對長期資料存儲的新興需求,開發人員開始尋找能提供低功耗,同時又無 EEPROM 和快閃記憶體等傳統 NVM 技術在效能方面限制的 NVM 元件。Cypress Semiconductor 的 Excelon 低功率 (LP) F-RAM 元件以 F-RAM 技術固有的速度和可靠性為基礎,將其固有的低電流需求與可編程的低功率模式相結合,可將電流消耗量降低至 1 mA 以下。使用 Cypress 的 Excelon LP F-FRAM 後,開發人員可利用長期資料存儲功能迅速彌補電池供電設計的不足。而這些功能既有傳統隨機存取記憶體所具備的速度,同時又能將資料可靠地保存 150 年以上。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。