選擇和使用適用於汽車介接、安全性和運算密集型負載的 FPGA

資料提供者:DigiKey 北美編輯群

2022-01-12

傳統上,汽車的運算任務是由微控制器單元 (MCU) 和應用處理器 (AP) 執行。一輛典型的中型車輛可能含有 25 至 35 個 MCU/AP,而豪華車款可能使用 70 個以上。越來越多汽車需要極其精密且運算密集的功能,以完成先進駕駛輔助系統 (ADAS)、車用資訊娛樂、控制、連網和安全性等任務。這當中有許多應用都涉及機械視覺功能,需採用圖像和影像處理,並且配合人工智慧 (AI) 進行。

若單純靠處理器架構,很難處理所有電氣介面和協定,而這些都是感測器、相機和顯示器等周邊裝置必要的元素。此外,在許多情況下,這些處理器就是無法滿足機械視覺和 AI 等任務的極端運算需求。

為了解決這個複雜問題,汽車系統的設計人員正逐漸轉用現場可編程閘陣列 (FPGA),但並非為了取代現有的 MCU/AP,而是當作 MCU/AP 與其他裝置間的橋接器,並透過將通訊和其他運算密集型任務卸載,來增強 MCU/AP 的功能。

由於 FPGA 可以透過編程來支援更多種電氣介面和協定,因此可以當作 MCU/AP 與感測器、相機和顯示器之間的橋接器。此外,由於 FPGA 能夠以大規模並行處理的方式進行運算和計算,因此可用來執行運算密集的視覺處理和 AI 任務,因而可以釋放主機處理器的能力,用於執行其他作業。

本文將討論現代車輛的處理要求,並說明幾種可透過 FPGA 因應的汽車應用。接著會介紹一些來自 Lattice Semiconductor 的 FPGA 產品範例,並說明如何使用 FPGA 來解決連接性、處理和安全性等方面的問題。此外,還會展示幾款相關的開發板,協助設計人員開始使用。

FPGA 的目標汽車應用

為了支援 ADAS 功能,當今的汽車在車輛外部採用許多感測器,包括相機、雷達、LiDAR 和超音波偵測器。在許多情況下,必須從不同的感測器獲取資料,對這些資料進行預處理 (去除雜訊並視需求格式化),並使用感測器融合技術來合併資料,如此一來,比起單獨使用來自不同感測器的資料時,產生的資訊,其不確定性會較低。在許多情況下,會採用 AI 應用來分析數據、進行決策,以及採取適當的措施。

有個相對較新的趨勢是部署電子 (亦稱「數位」) 後照鏡。在此情況下,後車窗內部會安裝高解析度的廣角相機。此相機的影像串流會顯示在數位顯示器上,以取代傳統的後照鏡,即可提供清晰的後照視野,視線不受後座乘客的阻擋。在某些情況下,左右後照鏡內部相機的影像串流,會與來自後車窗相機的影像串流合併。將這三種影像來源「拼接在一起」,就可形成單一圖像,並顯示在超廣角電子後照鏡上,能讓駕駛對車輛周圍的現況有更高的警覺性。

另一個最新趨勢則是將車廂內相機安裝在儀表板、方向盤機柱上,或整合到後照鏡中 (一般型或電子型)。搭配 AI 使用後,這些車廂內後照鏡就可用於多種任務,例如識別駕駛座上的人員,並對應調整座椅和後照鏡。這類系統除了可用來監控司機,確保他們注意路況而不是打瞌睡,還可以辨識他們疲勞的跡象,以及是否有癲癇或心臟病發作等醫療問題或情緒焦躁情況,並採取適當的措施。這些措施可能包括:啟動危險警告燈、施加剎車,以及將車輛引導到路邊。更多的應用包括,防止汽車被鎖定和開啟閃光燈,藉此確保幼童和寵物不會因疏失而被留在後座無人看管,並在乘客將手機、包包或包裹等物品留在後座時,提醒駕駛。

若是影像相關應用,在某些情況下,需要將單一影像輸入分割成多個串流;而在其他情況下,可能要依據設計要求,將多個影像串流聚合成一個。

隨著電動車 (EV) 的使用日益普及,對於監測器和控制馬達的需求也隨之而來,此外還要監測並管理充電過程,以達到最長的電池續航力。

最重要的是,當今許多汽車都開始支援 5G 或 V2X,而 V2X (車聯網) 是指車輛與其可能影響 (或受其影響) 之車輛及其他任何實體間的通訊,而這些實體則涵蓋路邊的基礎設施到其他車輛等等。此連接性也帶來安全性的需求,以免車輛遭駭。

汽車級裝置

請務必記住,並非所有 FPGA 都適合用於汽車應用。汽車電子協會 (AEC) 是最初由 Chrysler、Ford 和 GM 於 1990 年代成立的組織,其宗旨在於制定通用的零件合格標準和品質系統標準。最常引用的 AEC 文件之一是 AEC-Q100,標題為「Failure Mechanism Based Stress Test Qualification for Integrated Circuits」(基於故障機制的積體電路應力測試認證)。

IATF 16949:2016 是一種技術規格,目的是要制訂一套可持續改進的品質管理系統,並且特別強調瑕疵的預防,以及減少汽車業供應鏈和組裝流程中的變異和浪費。IATF 16949:2016 是由國際汽車特別工作小組 (IATF) 和 ISO 技術委員會根據 ISO 9001 標準而制訂。

對應汽車市場的電子系統供應商,逐漸要求半導體供應商提供符合 AEC-Q100 標準的產品,並且能夠證明其品質系統可通過 ISO/TS-16949 認證。

挑選適合的 FPGA

FPGA 非常靈活,但不同的裝置系列可提供多種不同的能力和功能組合,能更貼近特定任務的需求。以嵌入式視覺應用為例,現代相機和顯示器通常會採用 MIPI 介面。MIPI CSI-2 (相機/感測器) 和 DSI (顯示器) 協定,都採用一種稱為 D-PHY 的通訊實體層 (PHY)。傳統 MCU/AP 可能不支援此介面,但某些 FPGA 有支援,例如 Lattice Semiconductor 的 CrossLink-NX 嵌入式視覺和處理 FPGA。

除了兩個強化的四線道 MIPI D-PHY 收發器,可以支援每個 PHY 具有 10 Gbit/s 的速率,CrossLink-NX 裝置還支援 5 Gbit/s PCIe、1.5 Gbit/s 可編程輸入/輸出 (I/O),以及 1066 Mbit/s 的 DDR3。此外,這些裝置亦支援傳統的電氣介面和協定,如低電壓差動訊號 (LVDS)、Sub-LVDS (LVDS 的降壓版)、開放式 LVDS 顯示介面 (OLDI) 和 Gigabit 序列媒體獨立介面 (SGMII)。因此,這些裝置可用於聚合影像串流、分割影像串流、執行 AI 應用,並且在執行這些所有操作時,還可充當傳統 MCU/AP 與現代感測器和顯示器之間的橋接器。

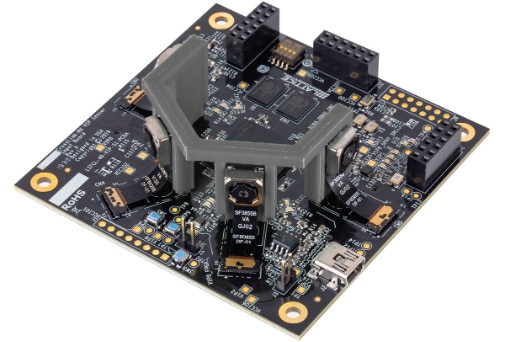

汽車系統開發人員若要評估 CrossLink-NX FPGA,都會關注 LIFCL-VIP-SI-EVN CrossLink-NX VIP 感測器輸入板 (圖 1) 和 LF-EVDK1-EVN 模組化嵌入式視覺套件的組合 (前者可以作為後者的輸入板)。除了 CrossLink-NX FPGA,感測器輸入板還配備四個 1300 萬畫素的 Sony IMX258 CMOS MIPI 影像感測器,可在 30 fps 下支援 4K2K 或在 60 fps 下支援 1080p。此外,亦可透過三個獨立的 PMOD 介面,支援簡易的感測器連接。

圖 1:CrossLink-NX VIP 感測器輸入板可作為嵌入式視覺開發套件的輸入,其中含有一個 CrossLink-NX FPGA,可支援將四個 MIPI Sony IMX258 圖像感測器進行聚合。(圖片來源:Lattice Semiconductor)

圖 1:CrossLink-NX VIP 感測器輸入板可作為嵌入式視覺開發套件的輸入,其中含有一個 CrossLink-NX FPGA,可支援將四個 MIPI Sony IMX258 圖像感測器進行聚合。(圖片來源:Lattice Semiconductor)

對於同樣需要大 I/O 頻寬的運算密集型應用,例如手勢辨識和控制、語音辨識和控制、人員在場偵測、乘客識別和駕駛監控等需要使用 AI 的任務,Lattice 的 ECP5 FPGA 具有以下特點:高達 3.2 Gbit/s 的串列器/解串列器 (SERDES);雙通道區塊中每個元件最多有四個通道,可達到更高精細度;高達 85K 的查找表 (LUT);增強型數位訊號處理 (DSP) 區塊,能讓對稱式濾波器達到 2 倍資源改善;以及單粒子翻轉 (SEU) 緩解支援。這些 FPGA 也提供可編程 I/O 支援,可用於 LVCMOS 33/25/18/15/12、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECL 和 MIPI D-PHY I/O 介面。

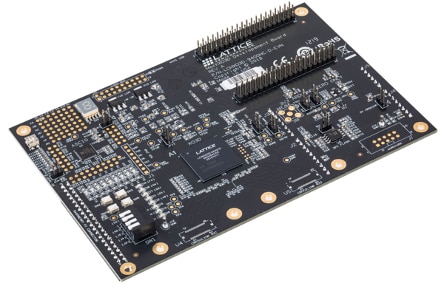

ECP5 裝置的範例之一是 LFE5U-85F-6BG554C,其採用 84,000 個邏輯元件、3.75 Mb 的 RAM 和 259 個 I/O。LFE5UM-45F-VERSA-EVNG ECP5 Versa 開發套件也是受到關注的產品 (圖 2)。此板採用 PCI Express (PCIe) 一半的尺寸,能讓設計人員評估 ECP5 FPGA 的關鍵連接特性,其中包括 PCIe、Gigabit 乙太網路 (GbE)、DDR3 和一般 SERDES 效能。

圖 2:ECPe Versa 開發套件採用 PCI Express 一半的尺寸,能讓設計人員評估 ECP5 FPGA 的關鍵連接特性,其中包括 PCIe、GbE、DDR3 和一般 SERDES 效能。(圖片來源:Lattice Semiconductor)

圖 2:ECPe Versa 開發套件採用 PCI Express 一半的尺寸,能讓設計人員評估 ECP5 FPGA 的關鍵連接特性,其中包括 PCIe、GbE、DDR3 和一般 SERDES 效能。(圖片來源:Lattice Semiconductor)

使用 FPGA 來保護汽車

駭客帶來的安全威脅日益增加,且新的漏洞不斷出現。就汽車而言,網路攻擊可能會導致失控,造成乘客和行人受傷或死亡,以及汽車、其他車輛和財產的損失。

汽車安全解決方案中有很大一部分,是要建立信任根 (RoT),亦即系統中始終可以信任的硬體資源。有個解決方案是以 FPGA 為基礎的硬體 RoT (HRoT),例如 Lattice 的 MachXO3D 系列裝置所提供的 HRoT。除了重要的 LUT 資源和大量 I/O 外,這些快閃記憶體型裝置還提供瞬間啟動和熱插槽功能。一般用途應用包括:緊連邏輯、匯流排橋接、匯流排介接、馬達控制、通電控制和其他控制邏輯應用。

特別值得注意的是,MachXO3D 是唯一同時具備雙重開機功能和少於 10K LUT 的 FPGA,且備有通過美國國家標準暨技術局 (NIST) 認證的不可竄改硬體安全引擎。因此,MachXO3D 可當作汽車的 HRoT,以系統的最先啟動、最後關閉元件形式運行。當系統通電時,MachXO3D 會先進行檢查,確保運行的是經過驗證的韌體。然後,MachXO3D 會檢查系統中其他裝置的韌體。如果系統中的任何元件 (包括 MachXO3D 本身) 受到攻擊或破壞,MachXO3D 會拒絕可疑的韌體,並使用已知良好且經過驗證的韌體映像檔,來重新載入該元件。

若開發人員想要評估採用 MachXO3D 的設計,LCMXO3D-9400HC-D-EVN MachXO3D 開發板提供可擴充的原型開發平台 (圖 3)。此板具有一個 L-ASC10 (類比感測和控制) 硬體管理裝置、可搭配 Arduino 和 Raspberry Pi 板使用的一般用途 I/O 介面、兩個 Hirose FX12-40 排針座腳位 (DNI)、一個 Aardvark 排針座 (DNI),以及具有四倍讀取功能的 128 Mbit 序列周邊裝置介面 (SPI) 快閃記憶體。

圖 3:MachXO3D 開發板具有一個 MachXO3D FPGA、一個 L-ASC10 (類比感測和控制) 硬體管理元件、Arduino 和 Raspberry Pi 板的支援、兩個 Hirose FX12-40 排針座腳位 (DNI)、一個 Aardvark 排針座,以及一個用於裝置編程的 USB-B 連線。(圖片來源:Lattice Semiconductor)

圖 3:MachXO3D 開發板具有一個 MachXO3D FPGA、一個 L-ASC10 (類比感測和控制) 硬體管理元件、Arduino 和 Raspberry Pi 板的支援、兩個 Hirose FX12-40 排針座腳位 (DNI)、一個 Aardvark 排針座,以及一個用於裝置編程的 USB-B 連線。(圖片來源:Lattice Semiconductor)

此板採用 4 x 6 in 尺寸,具有用於供電和編程的 USB mini-B 連接器,以及多個可排針座腳位,可支援 Arduino、Aardvark、FX12、Hirose 和 Raspberry Pi。此外,更隨附 USB 纜線和快速入門指南。

結論

現代汽車電子元件需要的感測器、電氣介面和協定越來越多,對處理能力和頻寬的需求也跟著增加。在加入 AI 和機械視覺處理能力以及安全需求後,採用傳統 MCU 或 AP 作法的解決方案,在實作上也變的複雜。

如上所述,只要適當地應用 FPGA,設計人員就可以增加一定程度的靈活性和處理能力,以橋接不同的處理環境、執行感測器聚合和融合功能、滿足 I/O 頻寬要求,並以大規模並行方式來進行計算和運算,同時將主機處理器的能力釋放,用於其他作業。

在安全方面,採用快閃記憶體的 FPGA 具有雙重開機功能,以及經過 NIST 認證的不可竄改安全引擎,可以當作汽車的 HRoT,確保 HRoT 和其他裝置只執行經過認證的韌體,藉此避免駭客以加密方式破壞汽車系統。

進階閱讀:

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。