Put RISC-V into Your Computer Architecture Course Using RVfpga!

Dear Professors and Friends,

Online is convenient and has saved us during the pandemic, but you can't beat in-person, in-class! That immersive feeling of hands-on and the shared mission with colleagues all trying to master the same subject.

We are in the middle of a global series of workshops to "train the teachers" on how to use RISC-V in computer architecture courses and the design of systems on chip (SoCs). We started in the USA last year and fitted in several Europe events as well. Of particular note is the December Workshop in Silicon Valley attended by nearly 60 Teachers and Trainers!

Now we are heading East: to Israel, Japan, Taiwan, Korea, and China.

RVfpga partners, including DigiKey, are working with us to make this possible!

To do this, we are asking for a day of your time so that you can empower the next generation of computer science and engineering students to get real-world expertise in computer architecture and the RISC-V instruction set architecture.

What is RVfpga?

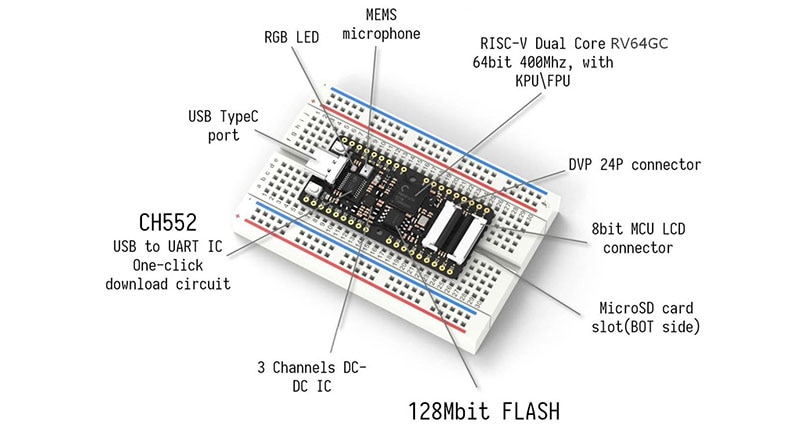

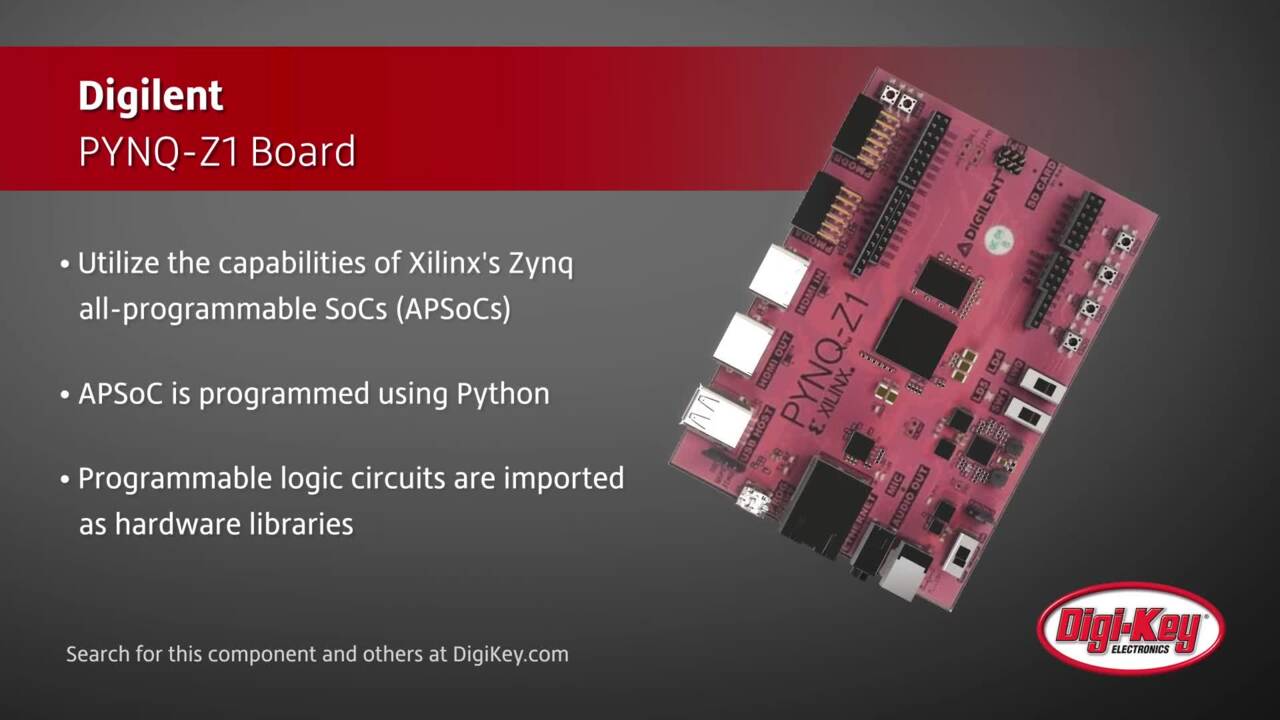

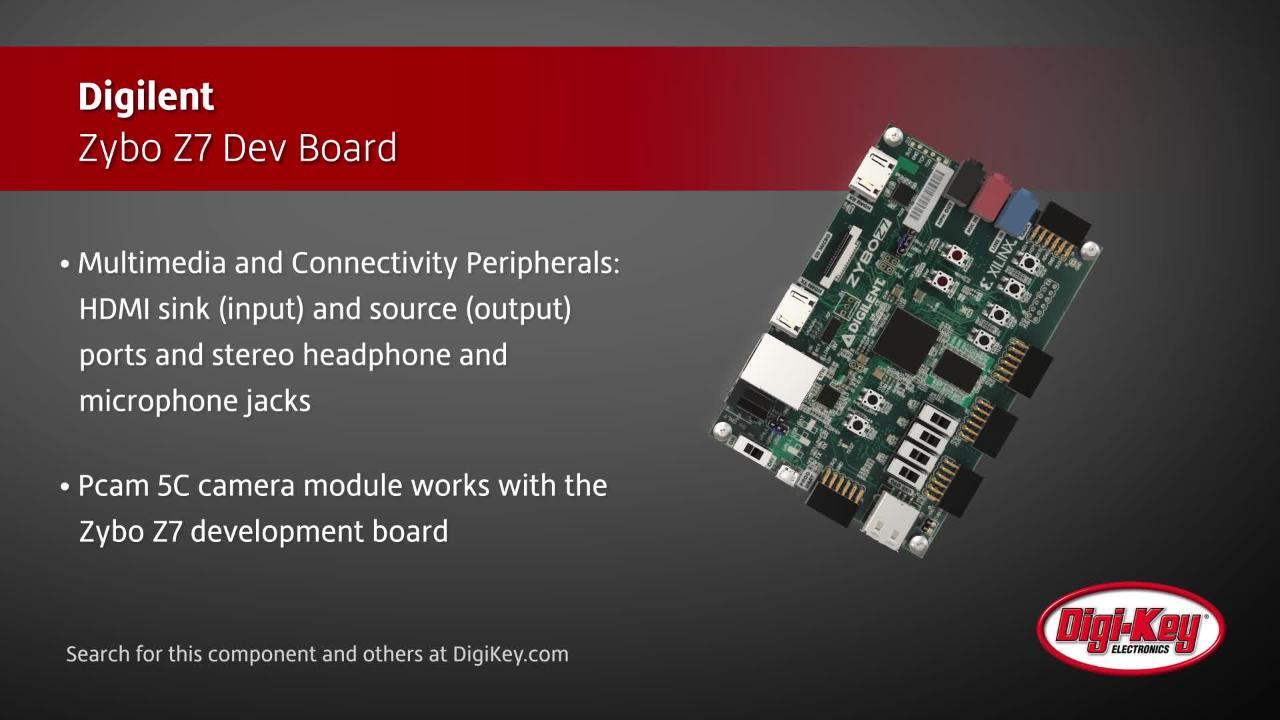

This in-person, one-day RVfpga workshop presents a commercial RISC-V system targeted to an FPGA, discusses the theory, architecture, and course structure, and shows how to use the hands-on labs as part of the complete RVfpga course. The course explores the fundamentals of computer architecture using Western Digital’s open-source, fully verified, already in-silicon, SweRV EH1 RISC-V core targeted to a Xilinx Artix 7 FPGA on Digilent’s Nexys A7 development board. Everyone will get hands-on experience with the FPGA platform and the software tools, enabling a fast start when you return to your university.

The SweRV is not an “education core”. It’s real-world, used inside Imagination’s GPUs and Western Digital’s solid-state drives.

What will you learn?

- The workshop shows how to quickly get the RISC-V FPGA system and RISC-V tools up and running

- We describe each of the labs and work through a selection of them hands-on

- We will also discuss how to integrate RVfpga into your curriculum

Specific topics include:

- Installing the tools (which we encourage before the workshop)

- Targeting the SweRV EH1 RISC-V core and SoC to an FPGA

- Programming the RISC-V SoC

- Adding more functionality to the RISC-V SoC

- Analyzing and modifying the RISC-V-core and memory hierarchy

Who should attend?

- It’s primarily a “Train the Teacher” event, of greatest value to EE, CS, and CE Teachers who want to teach Computer Architecture

- Trainers in commercial companies and postgrads who are considering a career in teaching or becoming a chip designer will also find it useful

Networking

It’s a great opportunity to make new and refresh existing links with fellow Professors who are keen to keep their courses up-to-date. Help us spread the word and bring your colleagues.

Meet innovators who are evaluating RISC-V for start-up projects, and company trainers who need great materials to train new recruits.

Our Trainers:

By teaming-up with skilled academics, and experts in other companies working on RISC-V, we are blessed with some of the most expert instructors in the world!

ASEE Baltimore & UCSC Santa Clara

Prof. Sarah Harris, professor of electrical and computer engineering at the University of Nevada, Las Vegas. Sarah Harris earned her M.S. and Ph.D. at Stanford University. She is the co-author of three popular textbooks: Digital Design and Computer Architecture, 2nd Edition (2007), ARM Edition (2015), and RISC-V Edition (2021). Her research interests include computer architecture and applications of embedded systems and machine learning to biomedical engineering and robotics.

Taiwan

Michio Abe, established expert on RISC CPU Architectures. He is Director, Sales & Solution, Japan, at MIPS LLC. His career started at NEC in 1985, and he has been involved in the development of MIPS CPUs including the development of the original NEC’s MIPS CPUs in 1991. This was followed by developing in-vehicle SoCs with MIPS and other cores and architectures. He has been in charge of promotion and marketing of MIPS CPU in Japan since 2015, initially as part of Imagination Technologies and now as a stand-alone company.

Our local host is Prof. Brian Lin from NTUST Taipei.

FPL 2023 Gothenburg

Daniel A. Chaver Martínez obtained a Physics Degree from University of Santiago de Compostela (USC) in 1998 and an Electronic Engineering Degree from University Complutense of Madrid (UCM) in 2000. He developed his PhD from 2000 to 2006 at UCM. He has taught many different courses related to Computer Architecture since 2000. His current research interests include: Architectural Techniques for the Cache and for Non-volatile Memories and OS Scheduling for Asymmetric MultiProcessors. Since 2015, he has been collaborating with Imagination Technologies in the development of some of their processors and teaching materials.

Workshop Series (date & location)

| Date | Location/Event | City, Country | Format | Registration |

|

June 25th - 28th |

ASEE Conference | Baltimore, USA |

Paper: RVfpga: Computer Architecture Course and MOOC using a RISC-V SoC Targeted to an FPGA and Simulation |

https://nemo.asee.org/public/conferences/327/registration |

| July 5th & 6th |

NTUST |

Taipei, Taiwan |

TWO In-person One-day RVfpga Workshops in English (with Mandarin & Japanese support) |

https://www.eventbrite.co.uk/e/549461984587 [eventbrite.co.uk] https://www.eventbrite.co.uk/e/602617443997 [eventbrite.co.uk] |

| October Date TBC | Zhejiang Univ. |

Hangzhou, China |

In-person half-day RVfpga Workshop in Chinese. Trainers: Prof. Liu, Peng & Xi, Yuhao, Zhejiang University, Hangzhou |

To be announced |

| Sept. 5th 9 AM - 1 PM |

FPL 2023 |

Chalmers University, Gothenburg, Sweden |

In-person half-day RVfpga Workshop in English (Workshop-only registration is available ~$120) |

https://2023.fpl.org/attend/registration |

| Nov. 9th |

UCSC Silico Valley Training Center |

Santa Clara, Ca. USA |

In-person One-day RVfpga Workshop in English |

https://www.eventbrite.co.uk/e/rvfpga-understanding-computer-architecture-in-person-workshop-nov-9th-tickets-654132025497 |

More information

- About the IUP and RVfpga: https://university.imgtec.com/teaching-download/

- RISC-V blog: https://blog.imaginationtech.com/how-rvfpga-understanding-computer-architecture-will-give-under-grads-real-world-skills

- Intro to RISC-V: https://www.digikey.com/en/resources/risc-v

We look forward to meeting you in person!

Best Regards,

Robert C.W. Owen

Principal Consultant: Worldwide University Programme

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum