Intro to RISC-V

RISC-V is a relatively new computer technology that is being actively promoted as a competitor to many architectures that require fees.

RISC stands for “Reduced Instruction Set Computer”. Here the V stands for the Roman number 5. Hence RISC-V is the 5th Generation of a family of computer cores. It is pronounced “RisK Five”. Unlike most other ISA designs, the RISC-V ISA is provided at no cost with an open source license. RISC-V does not require a license because it is Open Source and Open Architecture which means that the design can be modified and special instructions can be created to improve performance or make life difficult for hackers. For more information view the introduction guide to RISC-V e-book linked here.

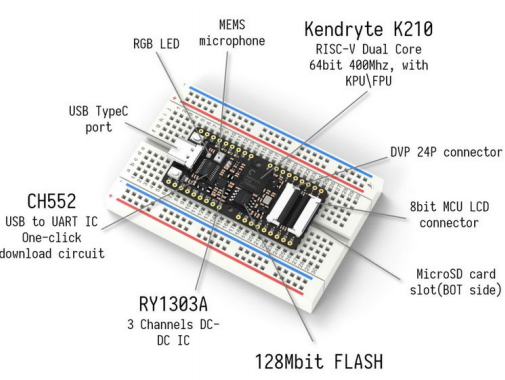

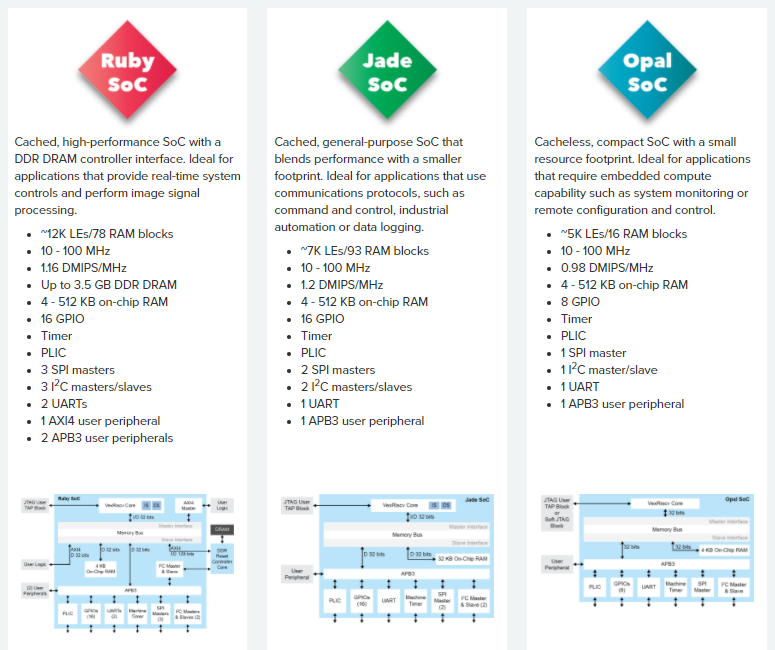

A growing list of products and suppliers such as Microchip, Seeed, Xilinx, Digilent are shown below:

Related Content

Specialized IP and software lets developers without FPGA experience rapidly deploy FPGA-based edge AI.

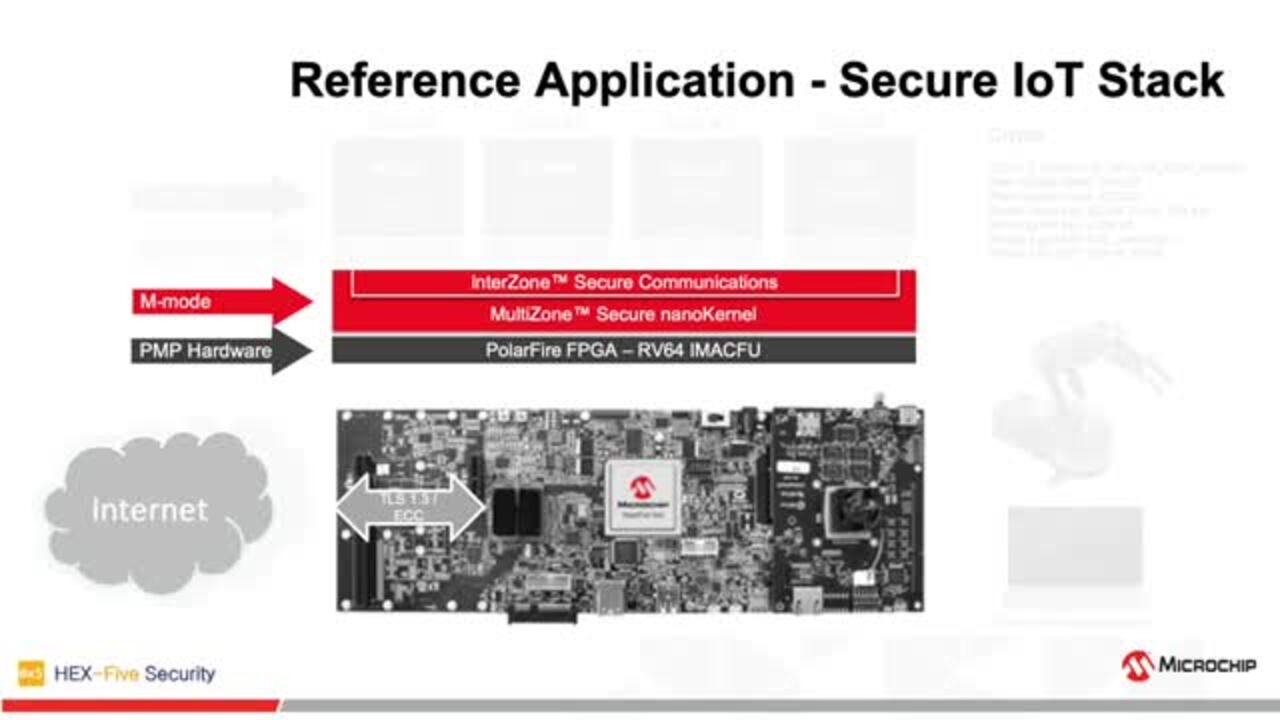

This session will appeal to anyone with an interest in embedded security in general and in RISC-V in particular.

The MultiZone™ demo shows how to secure the deterministic behavior of mixed-criticality systems where Linux and Real-Time come together in a single PolarFire SoC device.

Introduction to RISC V

Introduction to RISC V

A quick introduction to, and overview of the open-source RISC-V architecture.

Developers can depend on FPGAs and other programmable devices from Intel (Altera) in a tremendous range of applications.