Implementing High-Performance Programmable Clock Generators for Data Centers and Industrial Systems

Accurate timing to support Ethernet and Peripheral Component Interconnect Express (PCIe) communications is important and can be challenging when you’re designing servers, storage systems, and networking or embedded industrial systems. It’s not just about adding an Ethernet or a PCIe bus. A typical design can have several buses, all of which need accurate timing support with a minimum of jitter. A typical system requires a mix of communications buses that operate at various frequencies up to 650 megahertz (MHz).

You need solutions that take as little printed circuit (pc) board space as possible. In addition, the timing needs of Ethernet and PCIe differ, increasing the design challenge. To address these demands, you can turn to compact programmable clock generator ICs that can simultaneously deliver up to 12 reference clocks for Ethernet and PCIe buses.

This blog briefly reviews some of the timing needs of Ethernet and PCIe buses, then presents compact programmable clock generator solutions from Renesas you can use that simultaneously support the needs of multiple PCIe and Ethernet buses. Evaluation boards to speed your development of timing circuits in servers, storage systems, and networking or embedded industrial systems are also presented.

Controlling jitter and minimizing EMI

PCIe and Ethernet are used for different purposes. PCIe applications include chip-to-chip communications on a PC board and connections to expansion cards, while Ethernet is used for local area networks (LANs), storage area networks (SANs), and similar applications. The different operating environments place different demands on timing circuits.

Jitter attenuation is critically important in Ethernet networks. For example, in high-speed Ethernet up to 650 megahertz (MHz), root mean square (RMS) phase jitter needs to be limited to 150 femtoseconds (fs) maximum to ensure signal integrity, reduced propagation delays, and predictable behavior.

In addition to controlling jitter, PCIe buses benefit from the use of spread-spectrum modulation that spreads the jitter energy over a wider range of frequencies, minimizing electromagnetic interference (EMI). Controlling EMI means less need for shielding on pc boards, which reduces system costs and speeds up system integration. The VersaClock generators from Renesas enable you to control the amount of spread spectrum modulation to optimize the cost-performance tradeoffs required by specific applications.

Do more in less space

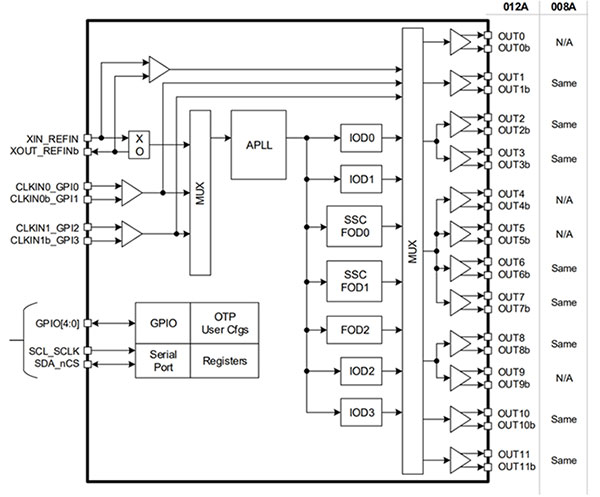

An integrated timing solution based on VersaClock generators from Renesas enables you to do more in less pc board space. They are available with 8 or 12 independent clocks and have the following features (Figure 1):

- Phase jitter of 169 fs RMS (10 kilohertz (kHz) – 20 MHz, 156.25 MHz)

- PCIe Gen6 common clock (CC) 27 fs RMS

- Support for PCIe separate reference independent spread (SRIS) and separate reference no spread (SRNS) operation

- 1 kHz to 650 MHz low voltage differential signaling (LVDS) and low-power, high-speed current steering logic (LP-HCSL) outputs

Figure 1 : VersaClock programmable clock generators are available that support up to eight clocks (column ‘008A’ on the right) or up to 12 clocks (column ‘012A’). (Image source: Renesas)

Figure 1 : VersaClock programmable clock generators are available that support up to eight clocks (column ‘008A’ on the right) or up to 12 clocks (column ‘012A’). (Image source: Renesas)

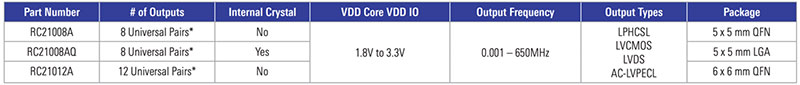

A traditional approach to building a timing solution with 5 independent clocks requires a common crystal oscillator circuit occupying about 3 x 3 millimeters (mm) of board space plus four sub-oscillators, each occupying about 5 x 3 mm. Or you can use a single VersaClock IC like the RC21008A that occupies just 5 x 5 mm. And that same IC can support up to eight clock outputs, further reducing board space, component count, and cost. Key features of the RC21008A are shown, along with two other ICs from the VersaClock 7 family: the RC21008AQ and the RC21012A (Table 1).

Table 1 : Shown are key features of 3 clock generators in the VersaClock 7 family; “*” denotes that the outputs are configurable to differential or LVCMOS. (Table source: Renesas)

Table 1 : Shown are key features of 3 clock generators in the VersaClock 7 family; “*” denotes that the outputs are configurable to differential or LVCMOS. (Table source: Renesas)

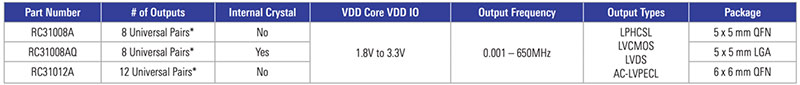

Attenuating jitter

The RC31008A, RC31008AQ, and the RC31012A programmable jitter attenuators have network synchronization capabilities, including JEDEC JESD204B/C for converter synchronization support on single-ended or differential outputs with AC or DC coupling, and support for synchronous Ethernet (SyncE) for network-based synchronization. Like the VersaClock clock generator ICs, these jitter attenuators are available with 8 or 12 outputs, reducing solution size and cost (Table 2).

Table 2 : Jitter attenuators in the VersaClock 7 family, “*” denotes the number of outputs configurable to differential or LVCMOS. (Table data: Renesas)

Table 2 : Jitter attenuators in the VersaClock 7 family, “*” denotes the number of outputs configurable to differential or LVCMOS. (Table data: Renesas)

Eval boards

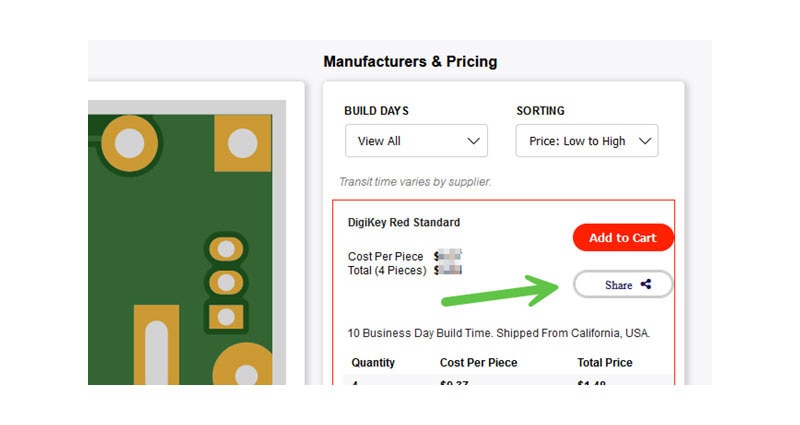

To speed up your development activities, Renesas offers a range of evaluation boards (EVBs), including RC21008-EVB (Figure 2) and RC21012-EVB, for 8 and 12 output clock generator designs, respectively, and the RC31008-EVB and RC31012-EVB eval boards that can be used for 8 and 12 output jitter attenuators, respectively. These EVBs can support clock generation in synthesizer mode for PCIe compliance and spread-spectrum performance and can also support jitter attenuation mode. They support frequency ranges of the reference input from 1 kHz to 650 MHz in differential mode and from 1 kHz to 200 MHz in single-ended mode. They feature a typical power dissipation under 1 watt with jitter specifications of:

- 150 fs RMS phase jitter (12kHz–20MHz, integer)

- 200 fs RMS phase jitter (12kHz–20MHz, fraction)

Figure 2: EVBs like the RC21008-EVB for the VersaClock 7 series support the development of eight output solutions. (Image source: Renesas)

Figure 2: EVBs like the RC21008-EVB for the VersaClock 7 series support the development of eight output solutions. (Image source: Renesas)

Conclusion

As shown, VersaClock clock generators and jitter attenuators from Renesas can be used to develop high-performance, compact, and low-cost timing solutions for PCIe and Ethernet buses across a range of data processing and industrial applications. To help you get started, EVBs are available to speed up the development process and shorten time-to-market.

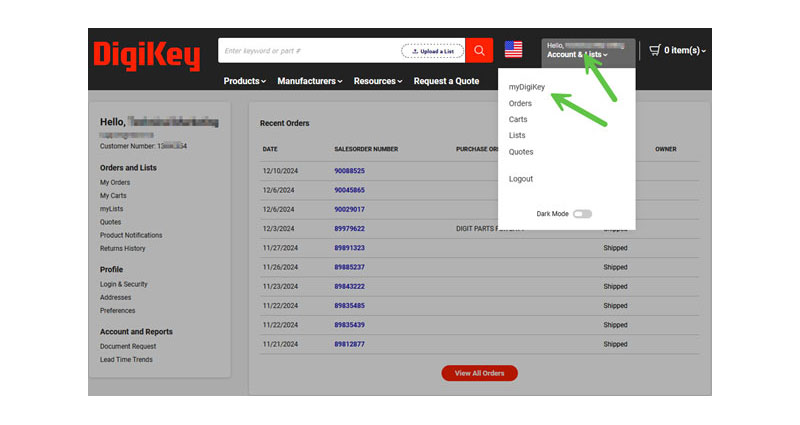

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum