Gate Level Modeling using Verilog - Part 25

2025-09-10 | By DWARAKAN RAMANATHAN

Gate-Level Modeling in Verilog: Bridging Logic and Silicon

Abstraction is key to managing complexity in digital design. From transistor-level designs to behavioral models at high levels of abstraction, every level of abstraction serves a particular purpose. For all of these, gate-level modeling provides a key bridge between abstract design and physical hardware. It represents digital circuits as a network of cooperating logic gates, and it is a key tool in structural design, timing analysis, and post-synthesis verification.

This blog gives an introduction to gate-level modeling with Verilog, its syntax, applications, advantages, and place in the ASIC and FPGA design process.

What is Gate-Level Modeling?

Gate-level modeling describes a digital system in terms of basic logic gates and how they are interconnected. It closely reflects the actual hardware implementation and is most typically utilized in:

- Post-synthesis verification

- Static timing analysis

- Power and switching activity estimation

- RTL vs. synthesized netlist equivalence check

- Fault simulation and test pattern generation

Gate-level modeling is more accurate than behavioral or dataflow modeling in describing the timing and structural aspects of a design because it is closer to the netlist generated by synthesis tools.

Gate Primitives in Verilog

Verilog provides a set of built-in primitives for modeling fundamental gates:

Logic Function-Verilog Primitive

AND-and

OR-or

NOT-not

NAND-nand

NOR-nor

XOR-xor

XNOR-xnor

Buffer-buf

Tri-state Buf-bufif1, bufif0

Tri-state Inv-notif1, notif0

These primitives can be directly instantiated to build logic structures at the gate level.

Syntax and Structural Modeling

Gate-level modeling would generally be structural in form, where attention is paid to how things get connected, not what they do.

Basic Syntax Example

module and_gate(output Y, input A, B); and (Y, A, B); // Creates a 2-input AND gate endmodule

Structural Example: 2-to-1 Multiplexer

module mux2to1(output Y, input A, B, Sel); wire nSel, w1, w2; not (nSel, Sel); and (w1, A, nSel); and (w2, B, Sel); or (Y, w1, w2); endmodule

This type of modeling is very useful when examining how a series of logic gates are connected in a schematic or physical layout.

Gate Delays and Timing Modeling

Delays in propagation are modeled with Verilog by passing delay values to gate primitives. Signal passing through gates has an influence on the performance in timing verification and is significant.

Example: Gate with Delay

module nand_with_delay(output Y, input A, B); nand #3 (Y, A, B); // 3-time unit delay endmodule

These delays may be global (the same for rise and fall) or label single transitions with triplet delay syntax:

and #(2:3:4) (Y, A, B); // rise:2, fall:3, turn-off:4

In actual flow, Standard Delay Format (SDF) files are created post-layout or post-synthesis and are back-annotated in the simulation with realistic delays from parasitic extraction.

Application in ASIC and FPGA Design Flows

Gate-level modeling is a key part of industry-standard flows:

1. Post-Synthesis Simulation

It is then simulated after being synthesized into a gate-level netlist to confirm:

- Functional equivalence with RTL

- Accuracy of optimizations and transformations

- No unintended logic introduced

This simulation is normally carried out using the synthesized Verilog netlist generated by tools like Synopsys Design Compiler, Cadence Genus, or Xilinx Vivado.

2. Static Timing Analysis (STA)

Tools like PrimeTime or Tempus use gate-level netlists and parasitic data to analyze:

- tSetup and hold violations

- Critical path delays

- Slack margins

This guarantees the design satisfies timing requirements under all operating conditions.

3. Power Estimation

Gate-level simulators aid in dynamic power estimation in terms of switching activity. Programs add up Value Change Dump (VCD) files to look at toggling per gate, which is used for determining average power consumption.

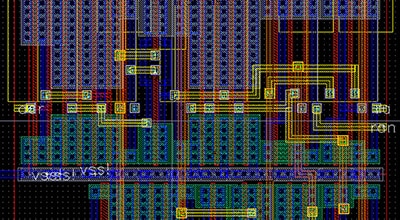

Gate-Level Netlists and Verilog

Gate-level Verilog, in actuality, has no types. It is treated by tools and has complete details such as:

- Cell types from standard cell libraries

- Interconnections based on net names

- Instances of flip-flop and logic gate modules

Example from a gate-level netlist:

module top_level ( input clk, reset, a, b, output y ); wire n1, n2; AND2_X1 U1 (.A(a), .B(b), .Z(n1)); INV_X1 U2 (.A(reset), .ZN(n2)); OR2_X1 U3 (.A1(n1), .A2(n2), .Z(y)); endmodule

This is technology-mapped logic using standard cell logic from a library (e.g., AND2_X1, INV_X1), which is converted to real transistors on silicon.

Advantages of Gate-Level Modeling

1. Accurate Timing Representation

Models delays based on real logic paths and gate loadings.

2. Power and Area Insights

Aids to reduce switching activity and monitor resource usage.

3. Synthesis Output Verification

Ensures RTL and synthesized netlist are functionally equivalent by means like gate-level simulation or formal verification.

4. Bridging Design and Layout

Critical to assist back-end engineers in verifying layout constraints, net lengths, and parasitic effects.

5. Fault Simulation and Test Generation

Employed in ATPG (Automatic Test Pattern Generation) to model stuck-at faults and improve test coverage.

Limitations and Considerations

Despite its advantage, gate-level modeling has one disadvantage:

- Simulation Speed: Gate-level simulations are extremely slow since they are low-level, granular.

- Complexity: Netlists are harder to read and debug manually.

- Restricted Usage for Functional Design: Not suitable for use in designing high-level algorithms or control logic.

Because of these considerations, designers tend to begin with behavioral or RTL models and later gate-level models for the implementation and verification steps.

Conclusion

Gate-level modeling in Verilog is a precise and unambiguous representation of digital circuits and is a part of the hardware design process. Gate-level models are useful in synthesizer output verification, timing, and power analysis, as they have information that is not present at higher levels of abstraction. Attaining this modeling paradigm allows designers to transition seamlessly from functional RTL descriptions to silicon-aware implementation, assured that their designs will not only be accurate but also efficient and manufacturable. In a forthcoming blog, we will explain actual examples of combinational and sequential circuits at the gate level using Verilog. We will demonstrate how the structural description of complicated logic can be done using primitive gates and how it can be verified using simulation.