實作資料中心和工業系統用的高效能可編程時脈產生器

在設計伺服器、儲存系統以及網路或嵌入式工業系統時,準確的時序對於支援乙太網路和快捷週邊組件互連介面 (PCIe) 來說非常重要,但也頗有難度。這不僅僅是添加乙太網路或 PCIe 匯流排這麼簡單。典型的設計可能有多個匯流排,且全都需要準確的時序支援並要求最小的抖動。典型的系統需要混用不同的通訊匯流排,且各以不同的頻率運作,最高可達 650 MHz。

您需要能盡可能佔用越少印刷電路板 (PCB) 空間的解決方案。此外,乙太網路和 PCIe 的時序需求也有所不同,因此會提高設計難度。為了因應這些需求,您可以使用緊湊的可編程時脈產生器 IC,同時為乙太網路和 PCIe 匯流排提供多達 12 個參考時脈。

本篇部落格文章將簡單回顧乙太網路和 PCIe 匯流排的一些時序需求,然後介紹 Renesas 的緊湊型可編程時脈產生器解決方案,即可透過此產品同時支援多個 PCIe 與乙太網路匯流排的需求。此外也會介紹多款評估板,可在伺服器、儲存系統以及網路或嵌入式工業系統中加速時序電路的開發。

抖動控制與 EMI 最小化

PCIe 和乙太網路的用途不同。PCIe 的應用包括電路板上的晶片對晶片通訊,以及與擴充卡的連接,而乙太網路則用於區域網路 (LAN)、儲存區域網路 (SAN) 和類似應用中。不同的操作環境對時序電路的要求也有所不同。

抖動衰減在乙太網路中至關重要。例如,在高達 650 MHz 的高速乙太網路中,均方根 (RMS) 相位抖動必須限制在 150 fs 以內,以確保訊號完整性、低傳播延遲,以及可預測的行為。

除了控制抖動之外,PCIe 匯流排也可受益於展頻調變的運用,可將抖動能量分散在更廣的頻率範圍內,進而將電磁干擾 (EMI) 降至最低。控制 EMI 意味著對電路板的屏蔽需求減少,因此可降低系統成本,並加速系統整合。Renesas 的 VersaClock 產生器能讓您控制展頻調變量,以便依據特定應用的需求,在成本與效能之間做出最佳化取捨。

以更小的空間成就更多

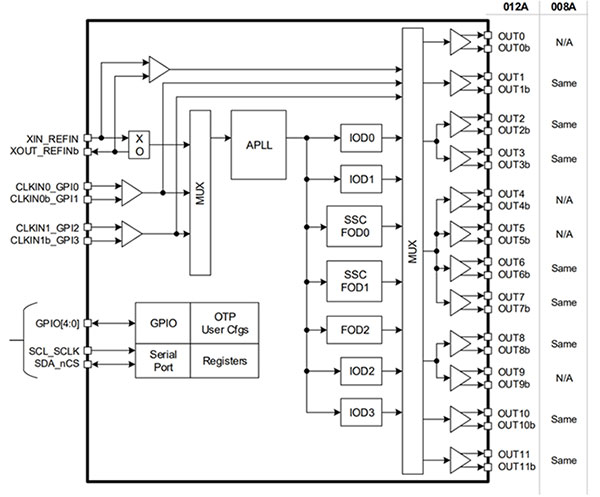

採用 Renesas 的 VersaClock 產生器的整合式時序解決方案,就可以更小的電路板空間達成更多工作。這些產生器提供 8 或 12 個獨立時脈,且具有以下特點 (圖 1):

- 相位抖動為 169 fs RMS (10 kHz – 20 MHz、156.25 MHz)

- PCIe Gen6 公用時脈 (CC) 27 fs RMS

- 支援 PCIe 獨立參考獨立展頻 (SRIS) 和獨立參考無展頻 (SRNS) 操作

- 1 kHz 至 650 MHz 低電壓差動訊號 (LVDS) 和低功率高速電流控制邏輯 (LP-HCSL) 輸出

圖 1:VersaClock 可編程時脈產生器可支援多達八個時脈 (右側的 008A 欄) 或多達 12 個時脈 (012A 欄)。(圖片來源:Renesas)

圖 1:VersaClock 可編程時脈產生器可支援多達八個時脈 (右側的 008A 欄) 或多達 12 個時脈 (012A 欄)。(圖片來源:Renesas)

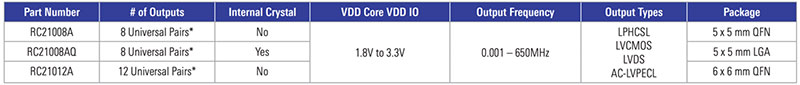

採用傳統方法建立具有 5 個獨立時脈的時序解決方案時,需要一個公用晶體振盪器電路 (佔用大約 3 x 3 mm 的電路板空間) 和四個子振盪器 (各佔用大約 5 x 3 mm)。或者可使用單一個 VersaClock IC,例如 RC21008A,只佔用 5 x 5 mm。而此相同 IC 可支援多達八個時脈輸出,可進一步縮小電路板空間、元件數量並降低成本。以下列出 RC21008A 的主要特點,還包括 VersaClock 7 系列的其他兩個 IC:RC21008AQ 和 RC21012A (表 1)。

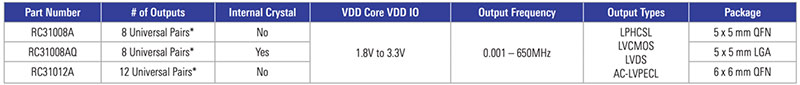

表 1:在此顯示 VersaClock 7 系列中 3 個時脈產生器的主要特點;「*」表示輸出可設定為差動或 LVCMOS。(表格來源:Renesas)

表 1:在此顯示 VersaClock 7 系列中 3 個時脈產生器的主要特點;「*」表示輸出可設定為差動或 LVCMOS。(表格來源:Renesas)

抖動衰減

RC31008A、RC31008AQ 及 RC31012A 可編程抖動衰減器具有網路同步功能,包括 JEDEC JESD204B/C,可在具備 AC 或 DC 耦合的單端或差動輸出上支援轉換器同步,並可支援同步乙太網路 (SyncE) 的網路式同步。這些抖動衰減器如同 VersaClock 時脈產生器 IC,可提供 8 或 12 個輸出,可縮減解決方案的尺寸和成本 (表 2)。

表 2:VersaClock 7 系列的抖動衰減器;「*」表示可設定為差動或 LVCMOS 的輸出數量。(表格資料來源:Renesas)

表 2:VersaClock 7 系列的抖動衰減器;「*」表示可設定為差動或 LVCMOS 的輸出數量。(表格資料來源:Renesas)

評估板

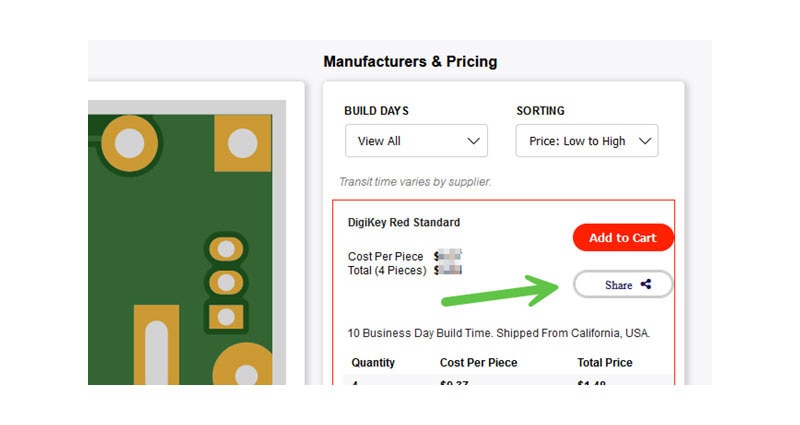

為了加速開發作業,Renesas 提供一系列評估板 (EVB),包括 RC21008-EVB (圖 2) 和 RC21012-EVB (分別適用於 8 和 12 個輸出時脈產生器的設計),以及 RC31008-EVB 和 RC31012-EVB 評估板 (分別適用於 8 和 12 個輸出抖動衰減器)。這些評估版可以在合成器模式下支援時脈產生,以達到 PCIe 合規性要求和展頻效能,同時還可以支援抖動衰減模式。在差動模式下支援的參考輸入頻率範圍為 1 kHz 至 650 MHz,在單端模式下為 1 kHz 至 200 MHz。典型功率耗散低於 1 W,抖動規格為:

- 150 fs RMS 相位抖動 (12 kHz–20MHz,整數)

- 200 fs RMS 相位抖動 (12 kHz–20MHz,分數)

圖 2:VersaClock 7 系列的 RC21008-EVB 等評估版可支援八個輸出解決方案的開發。(圖片來源:Renesas)

圖 2:VersaClock 7 系列的 RC21008-EVB 等評估版可支援八個輸出解決方案的開發。(圖片來源:Renesas)

結論

如本文所述,Renesas 的 VersaClock 時脈產生器和抖動衰減器,可在多種資料處理和工業應用中,針對 PCIe 和乙太網路匯流排開發高效能且緊湊的低成本時序解決方案。為了協助您開始開發,有幾款評估板可加速開發並縮短產品上市時間。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum