電路板用配電拓撲的「最佳」解決方案還是要靠經驗

工程師在日常工作中,會針對已知的問題,期望藉由分析以建立並提供「最佳」或「優化」的解決方案。但僅有一些,而非所有設計都能達到這個目標。原因很簡單:什麼參數和數值能被評斷為「最佳」?是否有一個關鍵的決定性因素?還是有許多不同的因素,以其微妙的平衡,自然而然達到最佳化?

真實情況:工程設計不光是執行與設計本身有關的專業技術,也需透過各種權衡和折衷,符合設計的個別需求。若不屬於設計團隊的人隨意提出批評,像是問「為什麼不用某種方式?」或「你難道不能順便加上那個東西嗎? 」這時候會讓設計人員倍感挫折。沒有身在其中,便不會瞭解設計人員所做的取捨,才會提出這些問題。

某些應用的設計會由一或兩項效能需求主導,例如深太空任務需低功耗和長期穩定性。其他情況下,則需滿足一些關鍵條件,但無須超越,因為最終產品不會因此從中獲益。

不過,設計人員在所有設計中都必須試著評估多項專案目標的性質和相關程度。舉例而言,如果多一點功耗,就能大幅提升速度或準確性,則會是一項良好的權衡。至於「成本」和「優點」的關係,要如何量化呢?我們幾乎無法這樣做,即使可以,其相關性的影響也微乎其微。一旦此類變數增加,其相關性就會變得更複雜、不明顯,並且難以辨識。

那麼,配電拓撲又如何呢?

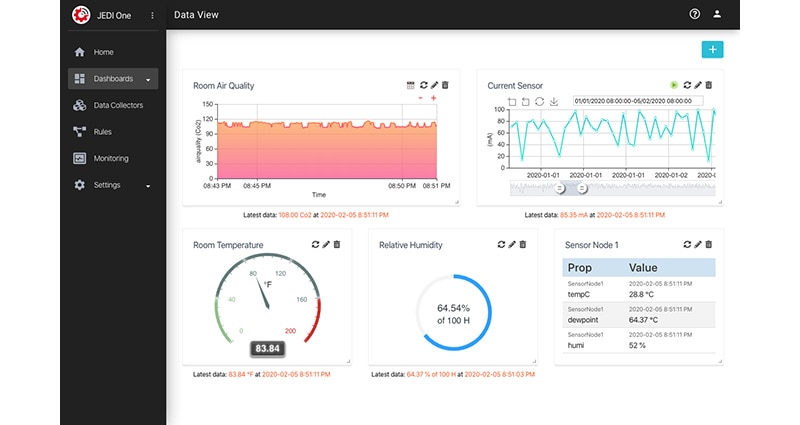

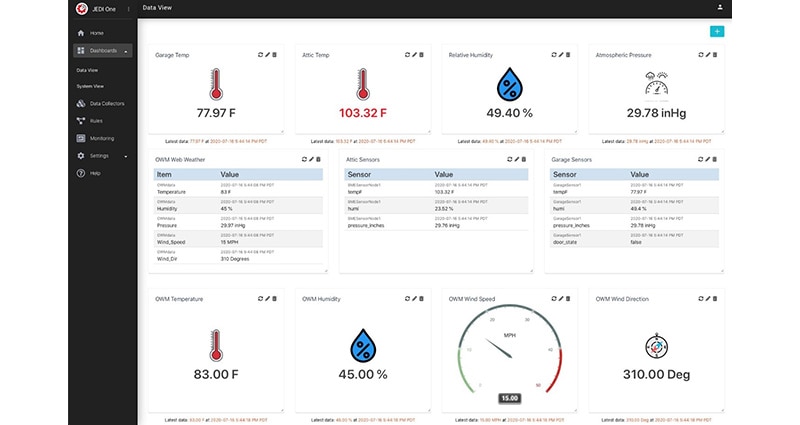

為了說明最佳化解決方案的複雜性,讓我們先來查看一個良好定義的系統功能:配電拓撲 (PDT)。每個電子設計都有一個電源子系統,但我們將著重在探討更小且固定在單一電路板上的子系統。這通常與數個電壓軌的值相關,以及任一獨立電壓軌的不同電流要求。我們先從兩個相同的 5 V 負載,每個負載為 0.9 A 的簡單案例來說明。

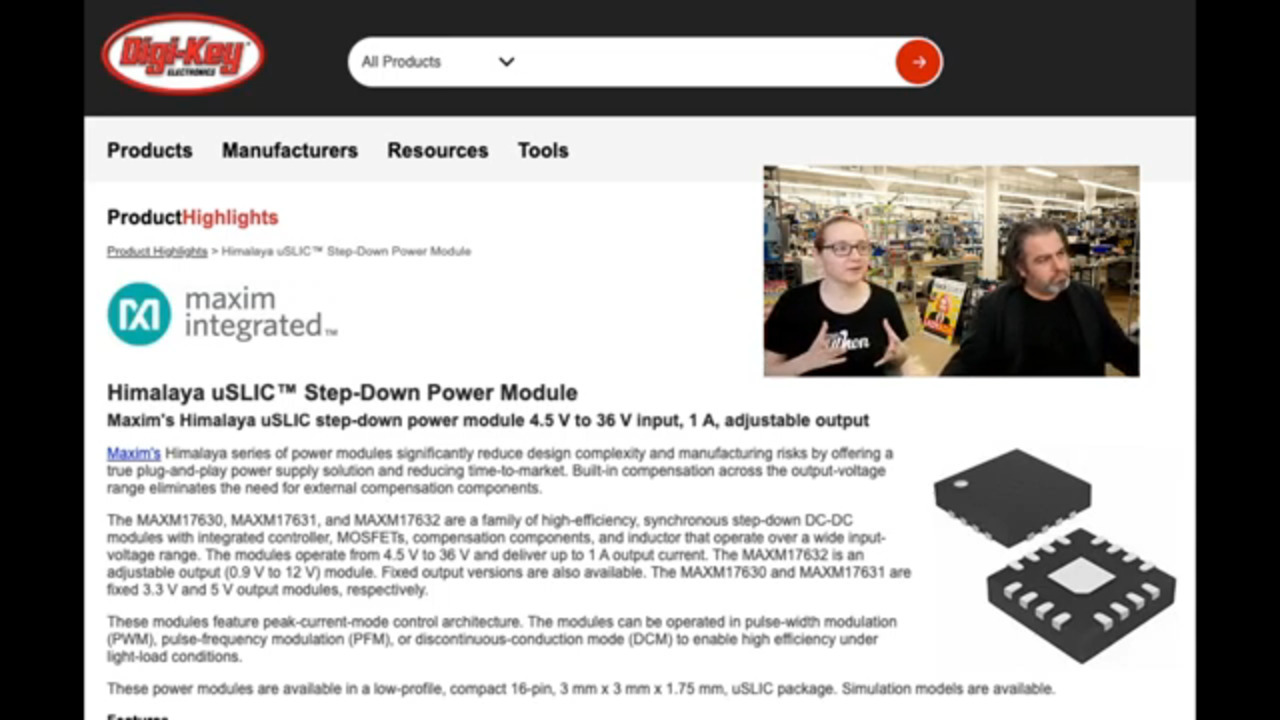

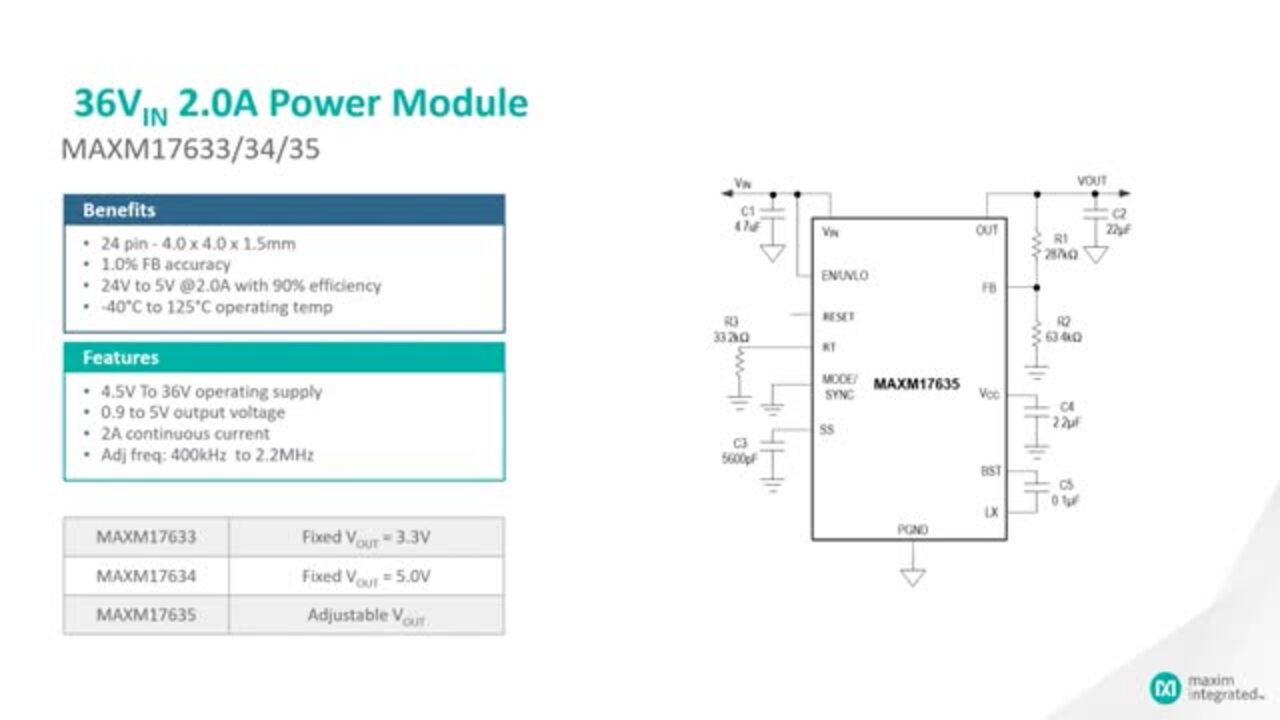

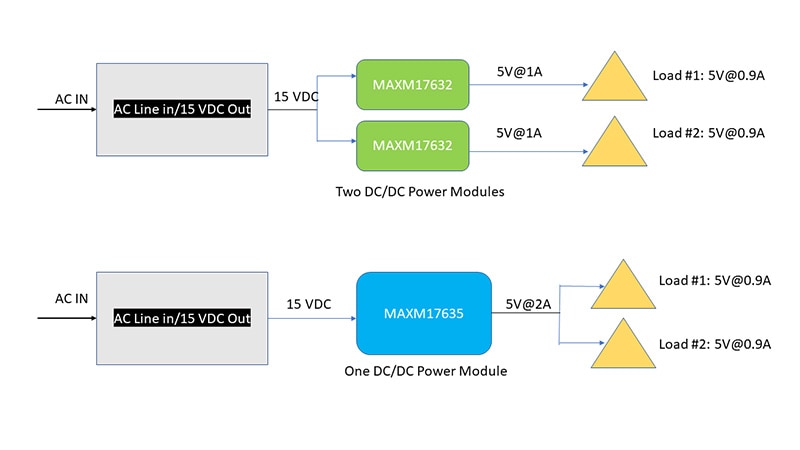

在這種極為簡單的情況下,也有兩個不同的選項 (圖 1),皆可透過 DC-DC 降壓模組進行實作,例如Maxim Integrated 的 uSLIC Himalaya 系列。其中之一是使用兩個 Maxim 的 MAXM17632 5 V/1 A 單元於各別負載,另一個則是使用 MAXM17635 5 V/2 A 模組同時供應兩個負載。進一步思考,如果其中一個負載僅 75 mA 而非 900 mA,您會使用 2 A 單元同時供應兩者,或使用 1 A MAXM17632 加上一個更小的 5 V/100 mA MAXM17900 於第二個負載呢?一如既往,答案是「視情況而定」。

圖 1:這兩種拓撲都可以針對兩個獨立的負載供應相同電壓的電源:使用兩個較小的 DC-DC 模組 (上圖),或一個較大的模組同時供應 (下圖)。(圖片來源:DigiKey)

圖 1:這兩種拓撲都可以針對兩個獨立的負載供應相同電壓的電源:使用兩個較小的 DC-DC 模組 (上圖),或一個較大的模組同時供應 (下圖)。(圖片來源:DigiKey)

兩個方式都可行,但有些因素需考量,例如兩個負載的相關位置、整體效率與負載的關係、整體耗散 (若其中一個負載有靜態期),以及來自電路板走線路徑的雜訊拾取。覆蓋區也會是一項因素:2 A 模組是 4 x 4 mm = 16 mm2;1 A 單元各為 3 x 3 mm,總共為 9 + 9 = 18 mm2。額外的 2 mm2 看似不太重要,卻會對緊湊的設計造成很大影響;分析得知,這會增加 12.5% 的覆蓋區。

問題不僅如此

在這樣簡單的 A 與 B 比較情境下,其中一個選項即使沒有極大差距,也可能勝出。不過,在包含許多負載的複雜案例中,即使在相同的標稱電壓下,通常還會有許多軟和硬因素必須考量:

- 負載數

- 各個負載的典型值、最大值、靜態電流

- 負載之間的相關位置

- 各個負載的動態

- 電源模組和負載之間由於具有較長走線,導致的雜訊拾起

- 負載的電壓準確性和調節:其中一個負載的需求可能為 ±0.5%,另一個則是 1%

- 負載平衡:如果其中一個負載需要 2 A,另一個需要 50 mA 時,針對 50 mA 的負載加上低壓降 (LDO) 穩壓器是否是個好主意?

- 接近負載點 (PoL) 電源轉換的優點和所需旁路

- 執行未調節主要 DC 電源所需的電路板區域,以及多重調節 DC 電源走線 (及其表面積);對佈局彈性的影響

- 電源模組和其支援元件合計的覆蓋區

- 電路板上的位置彈性

- 時脈頻率、EMI 和「拍頻」問題;使用通用時脈與個別 DC-DC 時脈的優缺點比較。

- 多種穩壓器配置的整體效率

- 所需被動元件的數量和類型

- 電流電阻 (IR) 壓降、走線寬度,以及在更高電流位準下可能需要的遠端感測

- BOM 元件成本

此清單顯示問題的多元複雜性。即使是單電壓的簡單情況,多種可能性和相關的自由度會隨著負載的數量增加而大幅提升。

解決問題的方法不在於竭盡心力尋找所有的可能性。EDA 軟體可以分析特定方式,並且針對目標分級,甚至可以適度協助查看各個方式的「假設」改變,但無法預見多種可能性及針對特定拓撲評定其「優點」與「成本及權衡」之間的比較 (至少現在無法達到,但有了人工智慧 (AI),也許在數年內可以達成!)。再加上現實中對多重電軌電壓的需求,此問題變得更加複雜,尤其是可以有不同中間匯流排轉換級。

因此,我看過一些工程師使用基本的試算表,而非 EDA 工具來針對許多拓撲路徑進行影響評分。最後,許多試算表欄位填入了定性評估,像是「差」、「好」、「非常好」,再加上在各欄位添加附註,例如「好-但只到 2 A」。

如果能創造實際的方程式,連結分析配電拓撲的眾多變因,應該不錯。目前還不會那麼快實現,因為有太多相互關聯的自由度,但由非線性關係、反曲點、飽和點和其他複雜且難以定量的相關性相連。

這就是為什麼在決定偏好的 PDT 方式時,工程專業、經驗、評斷,甚至於直覺會在此介入。針對最簡單的單一電路板決定「最佳」電源拓撲是個真實案例,展現工程的內涵,其所花費的心力超越冰冷的數值分析。

結論

若有人說他對設計問題有最佳解決方案時,最符合邏輯的問題是簡單且直接的:「『最佳』指的是什麼參數,以及達到什麼程度?」即使像是 PDT 如此簡單又明確的應用,也具備一長串的關鍵因素清單,有些密切相關,有些則否。

若您在設計審查時發表您的 PDT 解決方案,一定會被其他工程師詢問您為何採用所選的拓撲及如何做此決定。務必做好充分準備,報告您的分析、解釋您的想法,並且瞭解要使用經驗和判斷而非只是數字。如此一來,您應該可以清楚瞭解您的 DC-DC 電源模組和相關元件雖然不是唯一選項,卻很明顯最適當。

建議參閱:

使用小型化 PoL 轉換器達到最大增益

https://www.digikey.tw/zh/articles/maximize-gains-using-miniaturized-pol-converters

多即是少:使用更多穩壓器,節省寶貴的空間

https://www.digikey.tw/zh/articles/when-more-is-less-save-valuable-space-using-more-regulators

使用中階電流 DC/DC 穩壓器模組時應避免的常見錯誤

模組化 DC/DC 轉換器相較於離散式解決方案的優勢

https://www.digikey.tw/zh/articles/advantages-modular-dc-dc-converters-over-discrete-solutions

驅動 LED 陣列的電源供應器和拓撲解決方案

https://www.digikey.tw/zh/articles/advantages-modular-dc-dc-converters-over-discrete-solutions

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum