使用現成的元件來產生偽隨機二進位序列和白雜訊

資料提供者:DigiKey 北美編輯群

2018-03-22

雖然雜訊等隨機訊號通常會帶來問題,但通訊與裝置測試等應用卻仰賴隨機位元序列與雜訊的獨特特性。然而,對於一次性測試或預算緊繃的設計人員來說,購買專用的偽隨機二進位序列 (PRBS) 或任意波形產生器可能並不可行。在此情況下,較符合成本效益的作法是使用現成的 CMOS 裝置自行打造。

本文將說明 PRBS 及雜訊在電子產品中所扮演的實用角色。接著會介紹現成的 CMOS IC,並展示如何使用這些 IC 來產生所需的偽隨機雜訊及二進位序列。

「好」雜訊的作用

隨機的白雜訊在頻域中具有平譜。由白雜訊源激發的放大器或濾波器平均輸出振幅頻譜,將可導出該裝置的振幅頻率響應。

在通訊應用中,CDMA 發射器的數據流會透過偽隨機二進位序列 (PRBS) 加乘,然後與其他眾多訊號透過相同的 RF 通道進行發送。在接收器端將複合訊號與同一個 PRBS 相互關聯,便可擷取原始數據流,且僅有相當少甚至沒有干擾。由於這些隨機訊號相當有用,因此能在需要時產生這些訊號相當重要。

產生 PRBS

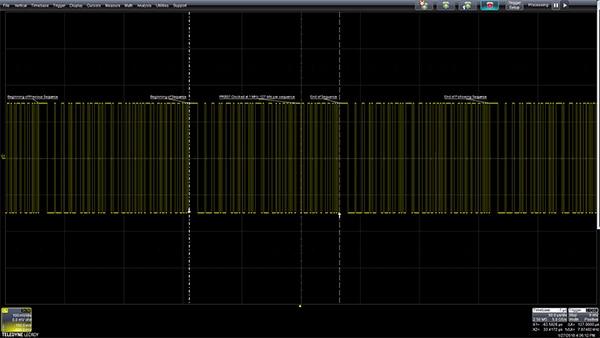

PRBS 是一種週期性的確定性訊號,由一連串的 0 與 1 數字組成。1 或 0 層的持續時間是 PRBS 產生器時脈週期的倍數。在產生器的排列模式重複週期內,1 與 0 排列模式是隨機的 (圖 1)。

圖 1:PRBS7 訊號屬於 7 位元長度的 PRBS 測試訊號,其週期為 27 – 1 (即 127 位元)。此訊號的時脈為 1 MHz,週期為 127 ms,如示波器游標所示。(圖片來源:DigiKey)

圖 1 的訊號是由七級產生器所產生的 PRBS7 測試訊號,每一個排列模式週期內包含 127 位元。在每個週期內,位元排列模式是隨機的,但整個序列每 127 個時脈週期,會以完全相同的形式重複。

這些測試訊號可在軟體或硬體中產生。測試時,在硬體中實作的優點在於,訊號可在外部取得,以便驅動受測裝置。

線性回饋移位暫存器

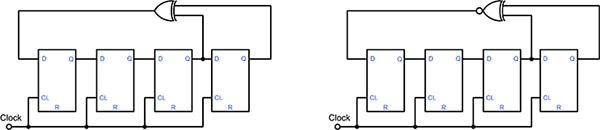

PRBS 的硬體實作使用線性回饋移位暫存器 (LFSR) 完成。有些移位暫存器是以串聯排列,使用 XOR/XNOR 閘,將後續級的回饋傳回到輸入端。使用的移位暫存器數量將決定排列模式的長度或持續時間 (圖 2)。

圖 2:使用 XOR 和 XNOR 回饋邏輯實作的四位元 LFSR 範例。回饋分接頭決定數據狀態的序列。(圖片來源:DigiKey)

雖然有許多種可能的回饋配置,但幾乎所有的設計都使用可產生最長序列的分接頭,使狀態的總數等於 (2N-1),其中 N 為移位暫存器級的數量。表 1 針對 2 至 32 的 LFSR 長度,統整了可達到最長序列的分接頭。這些分接頭不具互斥性。請注意,任何指定的移位暫存器長度都可能含有多個最大長度多項式。

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

表 1:2 至 32 LFSR 長度的最長序列分接頭摘要。(圖片來源:DigiKey)

此範例中使用了 15 級 LFSR,可產生長度為 32,767 位元的隨機序列,又稱為 PRBS15 測試序列。使用級數較高的 LFSR 即可拉長序列。PRBS 測試序列有所限制,即測試的持續時間。時脈為 500 kHz 的 15 位元序列需要 65 毫秒 (ms)。一個 31 位元序列需耗時 4295 秒,約 72 分鐘。

圖 2 的範例使用四個移位暫存器產生含有 15 種不同狀態的數據排列模式。請注意,兩種配置都有一個禁止狀態。在 XOR 回饋模型中,不使用全部為 0 的狀態,因為一旦載入後,移位暫存器就會鎖定在該狀態。同樣地,全部為 1 的狀態在 XNOR 實作中為禁止狀態。表 2 與表 3 顯示四位元 LFSR 的兩種配置的數據排列模式,使用的回饋分接頭分別來自第三與第四級。

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

表 2 與表 3:OR 和 NOR 配置的數據模式如圖 1 所示。(圖片來源:DigiKey)

兩種實作都從已知狀態開始,在 OR 配置中全都是 1,NOR 配置中則全都是 0。這些四位元最大長度 LFSR 都提供 15 種可能的狀態 (2N-1),如表格所示。

輸出數據排列模式是週期性的,每 15 個時脈就會重複。此排列模式也具有確定性,在指定配置和已知起始狀態下,即可預測輸出。然而,輸出模式在 15 個計次週期內是隨機的。

設計偽隨機二進位序列產生器

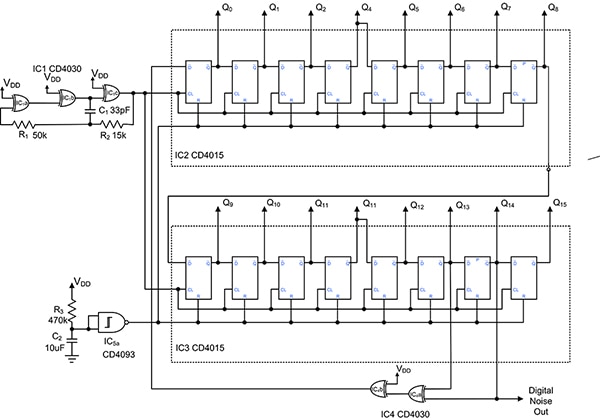

圖 3 的範例使用 Texas Instruments CD4015BM96 雙重四通道靜態移位暫存器以及 CD4030BM96 四通道 XOR 閘,打造一個以 LFSR 實作為基礎的實用且低成本 PRBS 產生器設計。

圖 3:使用 Texas Instruments CD4015BM96 雙重四通道靜態移位暫存器與 CD4030BM96 四通道 XOR 閘的 PRBS15 產生器簡圖。(圖片來源:DigiKey)

此產生器使用 16 個 D 型正反器 (每個 IC 八個),在第 14 與 15 級設有回饋分接頭,藉此產生 PRBS15 數據排列模式。回饋連結是透過 XOR 閘建立,然後逆轉成為 XNOR 設定的 LFSR。此數據模式的長度為 32767 位元,在 500 kHz 時脈率下的持續時間為 65 ms。若要達成更長的排列模式,可使用更長的移位暫存器,並在回饋分接頭上進行適當變動即可。若將設計延伸到 31 位元模式,會將模式的持續時間增加到 20 億個狀態以上 (在 500 kHz 時脈頻率下約 72 分鐘)。

使用 CD4093BM96 史密特觸發器 NAND 閘 (IC5) 與一個簡易 RC 網路,產生器會在啟動時初始化為全 0 狀態。時脈由一個以將近 500 kHz 運作的簡易 CMOS 振盪器提供。數位輸出可取自任一移位暫存器 Q 輸出。在此範例中,使用 Q14。

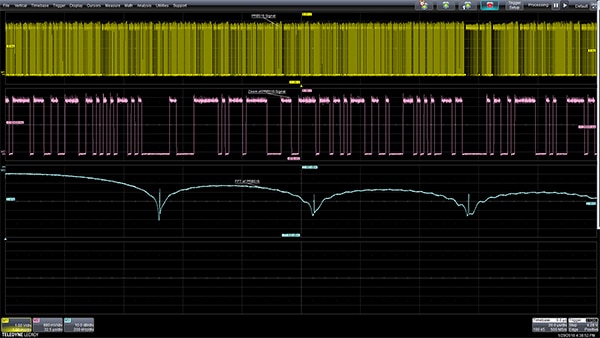

圖 4 的示波器中顯示了產生器的輸出以及輸出的快速傅立葉轉換 (FFT)。

圖 4:產生器的輸出 (頂部跡線) 在中段跡線橫向擴大,以便觀察細部結構。產生器輸出的 FFT (底部跡線) 顯示,在低於時脈率十分之一的部分為平譜。(圖片來源:DigiKey)

數位雜訊的 FFT 顯示出脈衝波型的預期 sin(x)/x 響應,且在時脈頻率倍數處都是 0。在大約時脈頻率 10% 處,頻譜相當平坦。這是使用低通濾波器從數位輸出擷取白雜訊的關鍵。

白雜訊產生器

白雜訊是在頻率範圍內頻譜平坦的雜訊。功率頻譜密度以及每單位頻寬功率,在雜訊頻寬範圍內保持恆定。PRBS 產生器會過濾數位雜訊輸出,然後產生白雜訊。

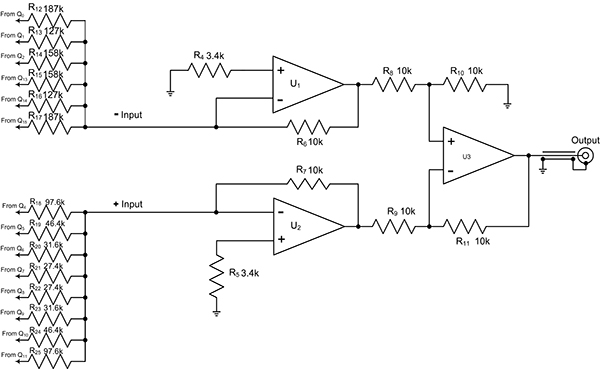

雖然也可以使用類比濾波器,但會限縮在特定時脈頻率。使用有限脈衝回應 (FIR) 低通數位濾波器,濾波器截止頻率會記錄時脈頻率的任何變化。另外,FIR 濾波器可提供非常低的截止頻率,若是類比濾波器的話,則需要非常大的電容。FIR 濾波器會合併移位暫存器輸出的加權總和。在頻域中產生矩形低通濾波器響應所需的加權為時域中的 sin(x)/x (圖 5)。

圖 5:產生器的輸出級採用來自移位暫存器輸出的 sin(x)/x 加權樣本來建置 FIR 低通濾波器。由於 sin(x)/x 加權需有負項,因此會使用差動放大器來加總正負加權分項。(圖片來源:DigiKey)

加權的移位暫存器輸出會在差動放大器中加總,此放大器是由 LM324KDR 四通道運算放大器的三個區段建立。上方的電阻排代表 sin(x)/x 加權中的負項。下方的電阻排則代表正值。輸出值 Q3 與 Q12 沒有相連,因為其代表 sin(x)/x 函數的零交叉點。產生的白雜訊輸出展現出典型的高斯概率密度函數 (PDF) (圖 6)。

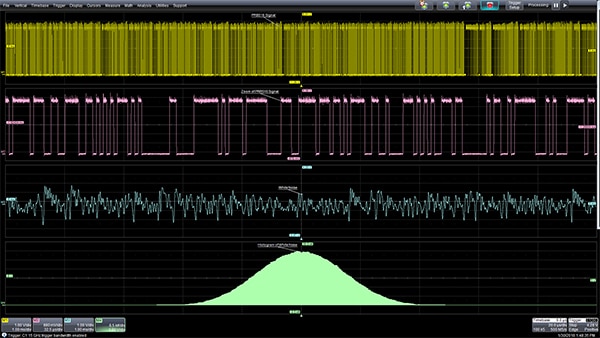

圖 6:PRBS 數位雜訊 (頂端兩條跡線) 與類比白雜訊輸出 (從頂端數來第三條跡線)。白雜訊的直方圖 (底部跡線) 展現出典型的鐘形常態曲線或高斯概率密度函數。(圖片來源:DigiKey)

白雜訊訊號是從頂端數下來的第三條。下方提供雜訊的直方圖,呈現出預期的常態曲線或高斯概率分布。白雜訊的頻寬限制在時脈頻率的 5%,即 25 kHz,適合音訊頻率測試用途。

結論

誠如本文所述,可使用現成的 CMOS IC 來產生偽隨機二進位序列及類比白雜訊,以進行通訊與測試用途。所需零件的 BOM 並不昂貴,因此非常適合學術研究、業餘愛好者以及有經濟考量的工程師和技術人員使用。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。