使用 HyperBus 擴充小型物聯網和穿戴式設計中的記憶體以節省空間和成本

資料提供者:DigiKey 北美編輯群

2018-08-01

隨著物聯網 (IoT) 節點和穿戴式裝置日漸縮小,設計人員需要善加運用微控制器的板載記憶體,以盡量降低電路板空間、功率和成本。然而,有時候無可避免必須擴充記憶體。與其預設成 32 位元控制器的匯流排結構,設計人員應考量使用 HyperBus,這是位址與數據兩者皆適用的高速 333 Mbit/s、8 位元、雙數據傳輸率 (DDR) 介面。

設計人員儘管想盡可能避免擴充,但在開發過程中往往仍由於記憶體需求增加而有此必要。或者,開發人員預期未來有擴充需要,純粹為了保障設計前瞻性而使然。

利用 HyperBus,微控制器可支援在同一個匯流排上設置外接式快閃記憶體與 RAM,相較之下,典型的 32 位元介面要有 16 位元數據與 16 位元位址匯流排和相關控制引腳。其適用於有 HyperBus 介面連接埠的任何記憶體元件,也是空間受限的應用中,以低引腳數擴充記憶體的高效、易用介面。

雖然匯流排的操作對韌體而言透明可見,但初識 HyperBus 的開發人員務必熟悉高速匯流排訊號的操作,以確保做出穩固的設計。本文首先描述 HyperBus 的操作。接著會介紹納入此介面的微控制器,也會向使用者說明如何著手高效運用和測試其設計。

HyperBus 的說明

如前所述,HyperBus 對於位址與數據兩者皆使用高速 8 位元 DDR 介面。此外,還為各記憶體元件使用差動時脈、讀/寫閂鎖訊號,和晶片選擇單元。HyperBus 可支援在同一個匯流排上設置外接式快閃記憶體與 RAM,並適用於有與 HyperBus 相容之周邊介面的任何微控制器。

HyperBus 可設定成為主控/從屬介面,其中以一個主機主控端接到匯流排上的一或多個從屬記憶體元件。HyperBus 快閃記憶體元件稱為 HyperFlash™,HyperBus DRAM 記憶體元件稱為 HyperRAM™。

匯流排使用一個差動時脈,訊號指定為 CK 和 CK#。因為 HyperBus 是 DDR 介面,所以在時脈的上升沿和下降沿皆會傳輸數據。時脈僅受主控端驅動,其頻率不可超過匯流排上最慢之 HyperBus 記憶體的額定時脈頻率。

雙向 8 位元匯流排指定為 DQ[0-7],可在主控與從屬元件之間傳輸位址、數據和命令。雙向讀/寫數據選通訊號 (指定為 RWDS),可用來閂鎖數據。RWDS 受到任何讀取數據的元件所控制,因此如果微控制器主機正在寫入數據到 HyperRAM,即由 HyperRAM 控制 RWDS 訊號。在 DQ[0-7] 上讀取的數據與時脈的兩個邊沿對齊。

利用低態動作晶片選擇單元選取各從屬元件,指定為 CS0#、CS1#、CS2# 等。任何時刻只能有一個晶片選擇單元可作用。指定晶片選擇單元由高態轉換為低態,啟動所有匯流排交易。指定晶片選擇單元由低態轉換為高態,終止所有匯流排交易。開發人員必須確保任何時刻皆有一個晶片選擇單元在作用。若未能做到,會導致不只一個 HyperBus 從屬元件同時驅動 RWDS,從而造成資料損毀。

低態動作硬體重置訊號 (指定為 RESET#) 由主控端驅動。被拉低時,會重置連線至此訊號之任何外接式 HyperBus 記憶體元件的狀態。這包括重置記憶體元件的內部組態暫存器。然而,並不會影響 HyperBus 記憶體元件內部記憶體的狀態。在大多數 HyperBus 主控微控制器介面上,RESET# 不屬於 HyperBus 周邊,而是通用 I/O 引腳。HyperBus 從屬元件在 RESET# 引腳的上拉電阻弱,因此若任由其浮動便會被拉至高態。

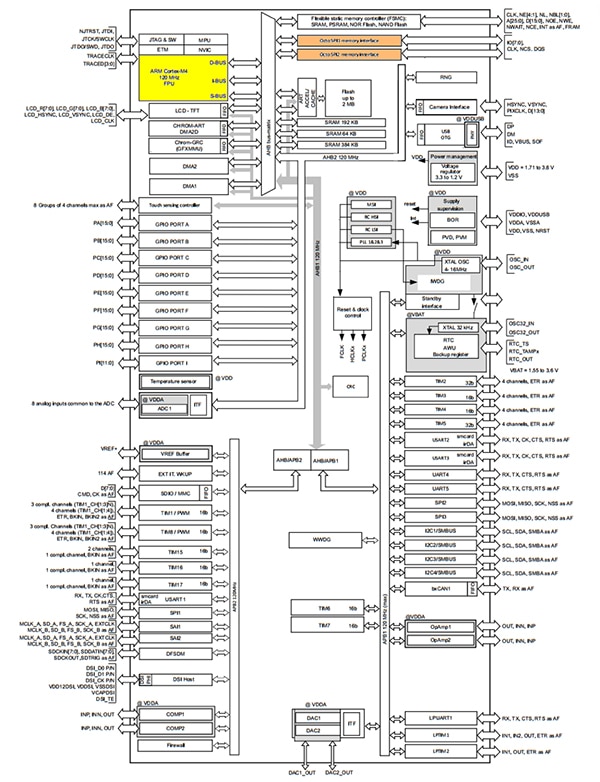

微控制器上任何與 HyperBus 相容的周邊,必須合乎 HyperBus 規格。STMicroelectronics 的 STM32L4R9 Arm® Cortex®-M4F (圖 1) 即為與 HyperBus 相容微控制器的良好一例。STM32L4R9 有 2 MB 的內部快閃記憶體和 640 KB 的 SRAM。此產品有廣泛的各種周邊,包括兩個 OctoSPI 介面,可配置為 HyperBus 介面。

圖 1:STMicroelectronics STM32F4L9 微控制器以 Arm® Cortex®-M4 核心與 FPU 為基礎,並且有兩個與 HyperBus 相容的介面,在此以橘色強調。(圖片來源:STMicroelectronics)

STM32L4R9 在記憶體對映至微控制器的 AHB 匯流排位址空間時,隨之存取 HyperBus 外接式記憶體位址,因此由核心存取外接式記憶體讀取和寫入的方式與內部記憶體相同。一旦將外接式記憶體元件配置完成,HyperBus 的操作對核心即為透明可見。

HyperBus 記憶體全是寬度 16 位元的記憶體,因此一律必須在 16 位元記憶體邊界對 STM32L4R9 存取。從 STM32L4R9 主控端的數據存取可以是 16 位元或是 32 位元,也必須在對齊的邊界上。

HyperBus 上的典型讀取或寫入交易為一連串循序的 16 位元、單一時脈週期的數據傳輸,經由兩個相對應的寬度 8 位元、半時脈週期的數據傳輸實現,在各單端時脈邊緣或差動時脈交叉上各一。讀取和寫入交易總是傳輸完整 16 位元的數據字組。讀取的數據字組總是含有兩個有效的位元組。寫入的數據字組可有一個位元組或兩個位元組皆遮蔽,以免在寫入突衝內寫入個別位元組。HyperBus 協定未支援位元組傳輸,亦不支援位元操作,例如位元帶操作。

STM32L4R9 上每個與 HyperBus 相容的連接埠各有一個專用 256 MB 對映記憶體的位址空間,對映情形如下:

HyperBus1 (OctoSPI1) 0x90000000 至 0x9FFFFFFF

HyperBus2 (OctoSPI2) 0x70000000 至 0x7FFFFFFF

所存取 HyperFlash 或 HyperRAM 記憶體元件的內部位址,會從上述位置的基底記憶體位址偏移。例如,若 STM32F4L9 自記憶體位置 0x90000047 讀取,會回讀在 HyperBus1 上的記憶體位置 0x0047 所存取之記憶體元件中儲存的數值。

Cypress Semiconductor 開發出 HyperBus 規格,亦有一個 HyperBus 記憶體產品線。Cypress 的ˊ S26KS512SDPBHI020 64 MB x 8 HyperFlash 記憶體可輕易接至其中一個 OctoSPI 連接埠。支援高達 32 個 16 位元字組的包覆突衝存取。最大 166.6 MHz 時脈率之下,S26KS512 HyperFlash 可支援 333 MB/s 的最高持續讀取率。在 OctoSPI 最大時脈 60 MHz 之下,STM32L4R9 能以最高 120 MB/s 的速率讀取任何外接式 HyperBus 記憶體。

如果是透過 Cortex-M4 系統匯流排存取 HyperFlash,STM32L4R9 能從這個快閃記憶體直接執行程式碼。作為程式碼記憶體使用時,OctoSPI 可支援有內建預擷取緩衝區的 eXecute In Place (XIP),其能自外接式記憶體載入下一個記憶體位址。

Cypress Semiconductor 的 S27KS0641DPBHI020 8 MB x 8 HyperRAM 記憶體是自我更新式 DRAM,能擴充 STM32L4R9 數據記憶體。支援高達 64 個 16 位元字組的包覆突衝存取。S27KS0641 HyperRAM 亦可支援高達 333 MB/s 的持續讀取率,並且能由 STM32L4R9 於最高 120 MB/s 之下讀取。

介接 HyperBus 記憶體

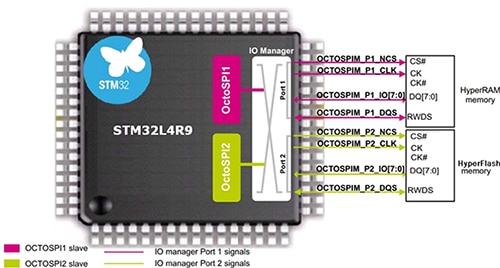

STM32L4R9 有兩個與 HyperBus 相容的連接埠,分別能介接 HyperRAM 和 HyperFlash 外接式記憶體元件 (圖 2)。RESET# 訊號為選用,因此圖中並未顯示。在兼具 Cypress HyperFlash 與 HyperRAM 之下,STM32L4R9 能在對 PC 板尺寸和設計複雜性影響甚小的情形下輕鬆擴充其內建記憶體。

圖 2:STM32L4R9 有兩個與 HyperBus 相容的連接埠,分別能接至 HyperRAM 和 HyperFlash 外接式記憶體元件。(圖片來源:STMicroelectronics)

對於佈局最重要的訊號是 DQ[0-7] 和 RWDS。為達最佳效能,這些訊號在 PC 板上微控制器與記憶體之間的長度應盡可能最短。

差動時脈訊號 CK 和 CK# 應相互比鄰,於訊號長度保持恆定間距。如可行,請將 CK 和 CK# 以 VSS 保護走線屏蔽,以盡量降低 EMI。為盡量降低阻抗不匹配,請將 PC 板頂層所有訊號分接,底下設置固態 VSS 層。

對初接觸 HyperBus 的開發人員而言,不妨加入探針測試點。對於 DQ[0-7] 和 RWDS,測試點應設在 STM32L4R9 微控制器與記憶體元件兩者。STM32L4R9 正在寫入時,最好觀察最接近記憶體元件的測試點。STM32L4R9 正在讀取時,觀察最接近 STM32L4R9 的測試點。對於 CK、CK# 和 CS,請讓測試點較接近記憶體元件。

因為 DDR 介面涉及高時脈頻率,對 STM32L4R9 和記憶體元件供應的電壓務必盡可能乾淨。雜訊多的供電會影響訊號時序,可導致匯流排傳輸錯誤,因此建議使用解耦電容。HyperBus 記憶體元件的 I/O 引腳有獨立的電源和接地,頂層或底層的 1 µF 和 0.1 µF 電容應加入至 I/O 電源 VCCQ。

韌體對 HyperBus 的存取

HyperBus 記憶體元件有晶片上暫存器,用以為元件設定選項和時序。HyperBus 將之稱為組態暫存器 (CR)。所有 HyperRAM 元件皆有內部 CR,允許設定某些操作特性。對於 HyperRAM S27KS0641,韌體能在外接式 8 位元數據匯流排上設定其低功率模式、包覆突衝長度、包覆突衝類型、讀寫時序參數,和輸出驅動強度。

HyperFlash 雖無 CR,但有狀態暫存器。S26KS512 HyperFlash 有三個狀態暫存器。可支援內部錯誤修正碼 (ECC) 以驗證寫入操作,並有 ECC 狀態暫存器可指出寫入錯誤。另一個暫存器含有任何 ECC 錯誤的位址。第三個暫存器可計算 ECC 修正數和無法修正的錯誤數。這些暫存器全都是唯讀。

HyperBus 交易可支援兩種記憶體操作。第一種是對外接式記憶體的讀取或寫入。第二種是對 CR 的讀取或寫入,或是讀取狀態暫存器。

STM32L4L9 OctoSPI 一旦配置為 HyperBus 連接埠,核心即可如同任何其他記憶體所對映的位置一般存取記憶體。記憶體所對映 HyperBus 空間中的每一讀取或寫入操作都會起始微控制器與外接式記憶體之間的交易。每次 HyperBus 交易各始於微控制器以命令/位址指令傳送三個 16 位元字組到外接式記憶體元件。命令/位址序列會告知外接式記憶體元件操作為讀取或寫入、記憶體空間或組態暫存器是否要定址、交易為包覆還是線性突衝交易,並提供目標位址的行與列。雖然這對於有操作韌體的微控制器而言全部透明可見,但除錯時命令/位址序列相當重要。

開始使用 HyperBus

開發人員一旦瞭解 HyperBus 協定,即建議以評估板執行一些實驗性的編程,尤其是初接觸此介面的開發人員。適用於 STM32L4R9 微控制器的 STMicroelectronics STM32L4R9I-EVAL 評估板為良好的著手起點 (圖 3)。HyperRAM 記憶體元件如紅色圓圈處所示,元件的測試點位於右側的排針座連接器。

圖 3:STMicroelectronics STM32L4R9I-EVAL 用來評估 STM32L4R9 微控制器。HyperRAM 記憶體元件如紅色圓圈處所示,元件測試點位於右側的排針座連接器。(圖片來源:STMicroelectronics)

STM32L4R9I-EVAL 具有廣泛特點,包括一個相機介面、兩個 MEMS 麥克風、一個搖桿,以及一個 4.3 in、480 x 272 像素的彩色 TFT LCD 顯示器。該評估板可支援 OctoSPI 介面,並有一個 ISSI 的 IS66WVH8M8BLL 64 MB HyperRAM 元件焊接到 PC 板上。

結論

對於重視空間的應用而言,HyperBus 協定是提供低引腳數記憶體擴充的適當介面,且容易使用。雖然匯流排的操作對韌體而言透明可見,初接觸 HyperBus 的開發人員務必熟悉高速匯流排訊號的操作,以確保達到穩固的設計。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。