利用無快閃記憶體微控制器來降低系統成本並提高效能

資料提供者:DigiKey 北美編輯群

2019-08-22

隨著物聯網 (IoT) 逐漸用於執行更加複雜的工作,IoT 端點的記憶體需求也不斷增加,特別是現今在邊緣執行更高階運算的端點。不過,晶片上微控制器的快閃記憶體受限於大約 1 Mbit 左右,而許多高端 IoT 端點所需要的記憶體,遠超出 1 Mbit 許多倍。

傳統的解決方法,都是利用外接快閃記憶體晶片擴充微控制器的程式記憶體。但當記憶體的需求高達 8 Mbit (或更多) 時,大多數程式記憶體最後都採用晶片外類型。

因此在許多情況下,設計人員可能最好完全捨棄晶片上快閃記憶體,而採用無快閃記憶體 (又稱為無 ROM) 微控制器,並搭配外接高速八線 SPI 晶片內執行 (XiP) 快閃晶片。這樣能大幅降低微控制器的成本,並能提高擴充性來滿足未來的設計需求。隨著極高速八進制記憶體介面的出現,無需擔心記憶體存取時間方面的問題。

本文將會討論無 ROM 微控制器與外接式記憶體,以及其如何進化成能用於需要大量程式記憶體的 IoT 端點及嵌入式系統。接著會展示如何利用 NXP Semiconductors 的無 ROM 微控制器與 Adesto Technologies 的八線 SPI XiP 快閃記憶體晶片,來實際應用此概念。

IoT 邊緣的記憶體擴充

大部分低至中效能的 IoT 端點,都使用微控制器來管理端點,將韌體儲存在晶片上的快閃記憶體裡。當新增額外的應用程式碼、無線 IP 通訊堆疊,以及增強型安全程式碼,韌體會逐漸隨之擴充。程式碼則可能在開發期間擴充,也會因現場更新作業而擴充。

這些 IoT 端點中,有一些如今用於執行更多的運算功能。這些 IoT 端點並未透過網路,將原始或經過部分處理的感測器資料傳輸到中央電腦進行處理,而是執行更複雜的工作,包括感測器融合式演算法、資料內插、圖形或影像辨識,以及越來越複雜的人工智慧 (AI) 運算。

這使得中央電腦只接收 IoT 節點的本機處理結果,而非原始感測器資料的每個位元組,因此能減少無線網路流量。由於 RF 發送器可能是 IoT 端點中最重要的功耗來源,因此邊緣運算往往能改善電池供電式端點的電池續航力。

對於需要在現場更新的系統,則面臨其他記憶體方面的難題。要處理這類更新,傳統系統所需要的空間,至少是預估的程式記憶體空間的兩倍。這是為了要應付現有的程式記憶體,以及任何空中 (OTA) 更新的大小。某些系統所需要的空間,可能是預估的程式記憶體空間的三倍,其中額外的記憶體會分配給唯讀原廠韌體映像。若出現某些類型的系統故障,包括偵測到駭入或損毀的韌體映像,系統可以載入最初的原廠韌體映像來復原系統。

對某些應用來說,這種記憶體擴充可能會迅速超越 1 Mbit 嵌入式快閃記憶體極限,需要進行外接式記憶體擴充。過去的解決方法都是新增外接式平行快閃記憶體晶片。但缺點是微控制器上會使用大約 36 個外接式引腳,而這些引腳本來是可以用於應用 I/O。此外,這也會浪費 PC 板空間,並增加板件發生電磁干擾 (EMI) 的機率。

SPI 程式記憶體擴充

除了採用平行匯流排,也能透過序列周邊裝置介面 (SPI) 擴充程式記憶體。雖然傳統 SPI 只使用一條數據線進行半雙工單位元傳輸,但過去幾年已成長為能支援兩條和四條數據線,而這使得數據傳輸量也相應增加,以至於足以介接大容量的外接 SPI 快閃記憶體晶片。

對於程式記憶體應用,傳統的雙線或四線 SPI 採用影子快閃記憶體設定,也就是外接式快閃資料記憶體,會複製到對應至程式記憶體空間的嵌入式靜態隨機存取記憶體 (SRAM)。雖然優點是能輕鬆擴充程式記憶體,還能藉著使用快速 SRAM 來改善執行速度,但還是有顯著的缺點。由於內建的 SRAM 容量有限,當快閃記憶體按需要交換到內建 SRAM 中時,記憶體會以分頁模式存取。雖然在晶片上增加更多 SRAM 能消除這個瓶頸,但由於 SRAM 是所有半導體中最昂貴的區塊之一,因此會大幅增加微控制器的成本。

SPI 最近一波的技術革命就是 XiP 功能。SPI XiP 可讓微控制器的 CPU,直接從外接式 SPI 快閃記憶體來執行韌體程式碼。藉由在 SPI XiP 介面增加快取,能大幅改善程式執行速度。

SPI XiP 的廣泛使用造成近期介面達到八條數據線。這個八線 SPI XiP 介面提升了傳輸量,以至於比晶片上快閃記憶體還快上許多—高於 100 Mbit/s。

SPI 記憶體革命

這使得 30 年前的一波奇特的革命再次重演。想想有個系統具備 1 Mbit 的晶片上快閃記憶體,以及 32 Mbit 的外接式程式記憶體快閃,後者透過八線 SPI XiP 介面存取。此晶片上程式記憶體非常小,小到令人納悶:假如撤除晶片上微控制器快閃記憶體,還能是個具成本效益的系統嗎?

長久以來一直認為,搭載快閃記憶體微控制器的中程系統,比搭載含有外接快閃晶片的無快閃記憶體微控制器,總是更具成本效益。但最近這個情況改變了。

如果移除晶片上快閃記憶體,當然會降低微控制器的成本。但深究之後發現,如果再也不需要使用快閃記憶體,則也能捨棄只用於快閃記憶體的製程技術特點。這能降低製造製程的成本,進而大幅降低微控制器的成本。因此,30 多年前所謂的「無 ROM」微控制器,再次浮現於世。今日,我們將其稱為無快閃記憶體。

「再次」引入無快閃記憶體微控制器

NXP Semiconductors 的無快閃記憶體 MIMXRT1052DVL6B (RT1052),就是一種能善用快閃記憶體速度的高效能微控制器。RT1052 是 NXP 的 i.MX RT1050 處理器系列產品之一,採用 600 MHz 的 Arm® Cortex®-M7,以及 32 KB 指令快取和 32 KB 資料快取。其移除快閃記憶體,並採用不受內建快閃記憶體限制的高速 CMOS 製程技術,使得時脈速率達 600 MHz。RT1052 擁有大量的 SRAM,高達 512 KB,可分割用於程式或資料記憶體用途。

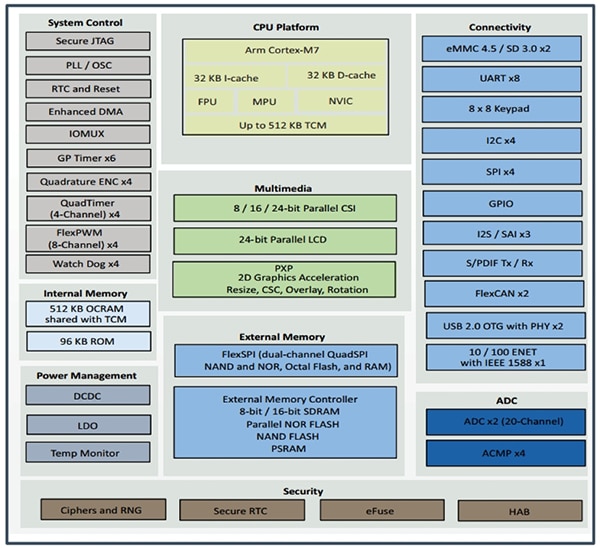

微控制器擁有多樣的高端周邊裝置,包括 LCD 介面、數位攝影機感測器介面 (CSI) 與像素處理管線 (PXP) (以支援高端攝影機)、SPDIF 介面 (用於數位音訊)、兩個 USB OTG 介面、兩個 eMMC/SD 快閃記憶卡介面、兩個 20 通道類比數位轉換器 (ADC),以及加密模組。圖 1 方塊圖中提供完整的周邊裝置清單。

圖 1:NXP 的 RT1052 具有許多種高端周邊裝置,包括 SPI XiP 序列介面,並支援資料加密。(圖片來源:NXP)

圖 1:NXP 的 RT1052 具有許多種高端周邊裝置,包括 SPI XiP 序列介面,並支援資料加密。(圖片來源:NXP)

另一個選擇是 NXP 的 MIMXRT1051DVL6B (RT1051)。除了 LCD 介面、CSI 與 PXP 外,該元件擁有與 RT1052 相同的特點。

RT1052 具有 FlexSPI 介面,可利用雙線、四線或八線 SPI XiP 快閃介面來執行程式碼。為了增加韌體的安全性,這款微控制器支援透過 SPI XiP 連接加密性程式記憶體。Adesto Technologies 的 ATXP032-CCUE-T 就是個很好的範例。

現代 XiP 快閃記憶體作業

Adesto 的 ATXP032-CCUE-T 是個 32 Mbit 八線快閃記憶體晶片,八條線路支援雙通道傳輸速率 (DTR) 模式下每秒高達 266 MB 的資料傳輸,這比晶片上微控制器快閃記憶體還快得多。該元件需要單一 1.8 V 供應電壓,典型八線模式待機電流為 35 µA,亦支援最多 133 MHz 的 SPI 時脈。

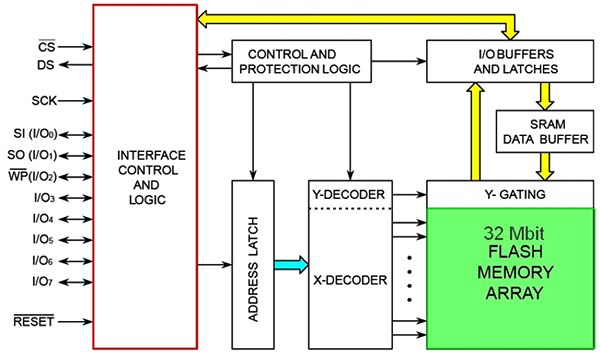

圖 2:Adesto 的 ATXP032-CCUE-T 快閃記憶體使用八線 SPI (I/O0 至 I/O7) 來連接微控制器。SRAM 寫入資料緩衝能改善寫入至快閃記憶體作業的效能。(圖片來源:Adesto Technologies)

圖 2:Adesto 的 ATXP032-CCUE-T 快閃記憶體使用八線 SPI (I/O0 至 I/O7) 來連接微控制器。SRAM 寫入資料緩衝能改善寫入至快閃記憶體作業的效能。(圖片來源:Adesto Technologies)

在動態快閃記憶體讀取期間,ATXP32 的電流消耗是 142 µA/MHz 外加額外 1 mA 負荷 (典型值)。八線模式下,最高 SPI 時脈速率為 133 MHz,電流消耗量僅為 19.9 mA。

此外,ATXP032-CCUE-T 也支援標準 SPI 模式 0 和 3,以及四線 SPI 模式。256 位元組安全暫存器擁有 128 位元組的原廠編程式唯一識別碼,以及 128 位元組的一次可編程 (OTP) 記憶體,而此記憶體可用來儲存乙太網路媒體存取控制 (MAC) 位址或安全金鑰等元件資訊。

值得一提的是 ATXP032-CCUE-T 記憶體的配置。此記憶體分割成四組,每組 8 Mbit。內部邏輯會設定成讓主機微控制器能從一組來執行程式碼,同時編程或清除另一組。這個作業對主機微控制器是透明的,不需要特別的設定。

此外,ATXP032-CCUE-T 還有三個狀態與控制暫存器,用於設定元件的作業參數 (例如低功率模式)、啟用或停用 DTR 模式,以及設定標準、四線或八線 SPI 模式 (預設為標準 SPI)。透過讀取狀態暫存器,可指出編程或清除作業狀態、功率過低狀態,以及是否有任何記憶體受到寫入保護。

組合無快閃記憶體微控制器和外接式 XiP

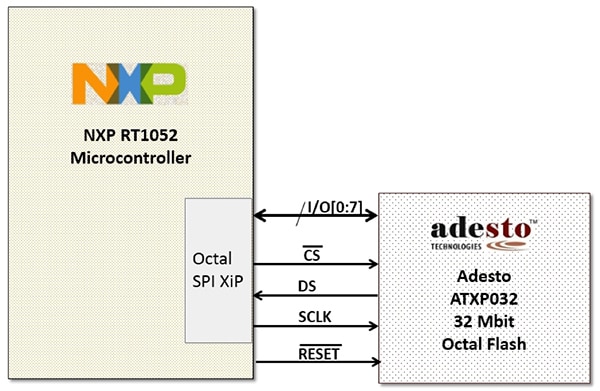

RT1052 和 ATXP032-CCUE-T 輕鬆就能組合在一起 (圖 3)。電源啟動後,RT1052 會開始從 96 KB 的晶片上開機唯讀記憶體來執行程式碼。開機唯讀記憶體會讀取 14 個開機模式設定引腳的狀態,這些引腳會從眾多 RT1052 外接式記憶體介面中選擇要用於程式記憶體的部分。選項包括外接式 eMMC 卡、micro SD 卡、傳統的外接式平行介面,或是 SPI XiP (在此例中就是 Adesto 的 ATXP032-CCUE-T)。

圖 3:NXP 的 RT1052 無快閃記憶體微控制器具有八線 SPI XiP 介面,能輕易連接到 Adesto 的 ATXP032-CCUE-T。八線 SPI XiP 介面作業對 Arm 核心來說是透明的。(圖片來源:DigiKey)

圖 3:NXP 的 RT1052 無快閃記憶體微控制器具有八線 SPI XiP 介面,能輕易連接到 Adesto 的 ATXP032-CCUE-T。八線 SPI XiP 介面作業對 Arm 核心來說是透明的。(圖片來源:DigiKey)

RT1052 的開機選項還包括從 USB OTG 或 UART 下載程式碼並從 SRAM 執行。只要熔斷 RT1052 內的保險絲,開機模式選項也能在製造期間設定,而不必使用開機模式設定引腳。一旦啟用八線 SPI XiP 介面,以讓 RT1052 的開機唯讀記憶體執行程式記憶體後,就能立即執行程式。接著,Arm 核心會從 Adesto 的 ATXP032-CCUE-T 執行韌體,其方式與從外接式並聯快閃元件或內建快閃記憶體相同。

由於涉及高速數據傳輸,在 PC 板上放置八線序列快閃記憶體時,應儘可能讓其靠近微控制器的八線 SPI XiP 埠。為減少干擾,所有 PC 走線都不應該超過 120 mm。時脈訊號應遠離其他訊號,距離至少為電路板走線寬度的三倍,以避免干擾。I/O [0:7] 雙向數據訊號應彼此相距 10 mm 之內,以免發生偏斜。

結論

邊緣運算趨勢、OTA 更新需求,以及相關的記憶體擴充需求,使得 IoT 端點的記憶體需求越來越大。有些時候,這些端點元件的設計人員可能會發現,使用無快閃記憶體微控制器是個值得考慮的選擇。

如前文所述,無快閃記憶體微控制器、高速介面,以及八線 SPI XiP 快閃記憶體晶片的進步,讓設計人員能打造出高效能且具成本效益的 IoT 端點或嵌入式系統,取代傳統以快閃記憶體為基礎的微控制器作法。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。