使用現成的 IEEE 802.3bt 解決方案,進行高功率乙太網路供電設計

資料提供者:DigiKey 北美編輯群

2019-05-09

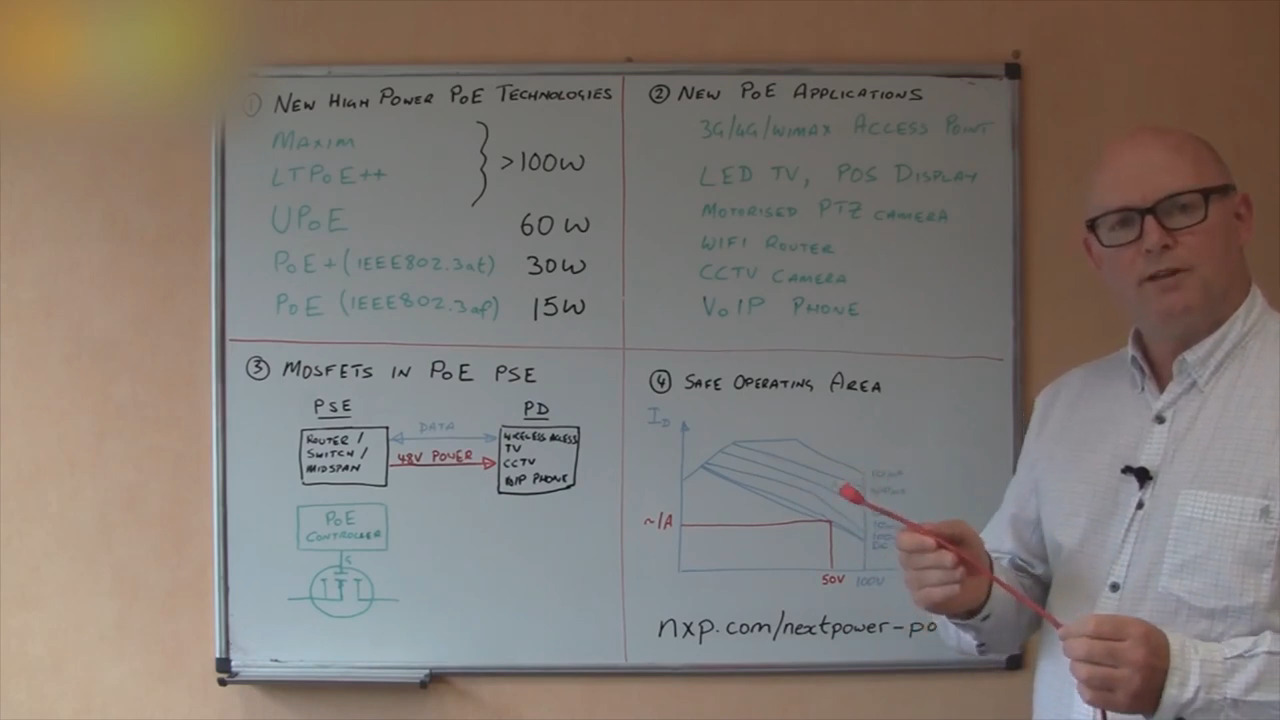

乙太網路供電 (PoE) 技術於 2003 年問世。之後,其電力傳輸能力從原來的 15.4 W 大幅提升至 30 W,但設計人員仍然需要更高的功率來實作相關應用。最新修訂的 PoE 規範 (IEEE 802.3bt) 能因應這項需求,在電源端提供高達 60 W (在某些應用中可高達 90 W) 的功率。

這項修訂標準於 2018 年底通過批准。首批商用的整合式供電裝置 (PSE) 控制器與受電裝置 (PD) 介面現已推出,能讓設計工程師充分利用所謂的「高功率 PoE」技術。

本文將探討 IEEE 802.3bt 和舊版 PoE 標準的不同之處,然後介紹來自 Microsemi、Texas Instruments (TI)、Linear Technology 以及 Nexperia 的整合式 PSE 控制器與 PD 介面。本文將說明如何最有效地運用這些裝置來打造系統,內容涵蓋電路保護、設計和佈局要求等重要考量因素。

什麼是 IEEE 802.3bt?

原來的標準 (IEEE 802.3af) 規定在電源端最高提供 15.4 W 的功率,這對應付 IP 電話及 Wi-Fi 存取點等應用來說綽綽有餘,但對一些較新的應用來說還是不夠,比如說 IP 影像電話或全方迴轉伸縮鏡頭 (PTZ) 攝影機。此項規範在 2009 年推出修訂版 (IEEE 802.3at),規定在電源端提供 30 W 的功率,從而解決了這個問題。近年來,愈發需要更高的功率來支援乙太網路連線式應用,例如銷售點 (POS) 終端器、IEEE 802.11ac 存取點,以及連網式 LED 照明。

為了滿足對更高功率的需求,新版的 IEEE 802.3bt (高功率 PoE) 標準對以前的 PoE 與 PoE+ 規範作出修訂,提高了 PSE 的最低輸出功率以及 PD 的最低輸入功率。主要的變化在於,電力可透過 Cat5e 乙太網路線纜的全部四對雙絞線進行傳輸。PoE 與 PoE+ 僅使用其中兩對雙絞線,即「替代方案 A」應用當中的數據線,或「替代方案 B」應用當中的備用線路。(請參閱 DigiKey 知識庫文章「乙太網路供電介紹」。)

這項全新的規範也催生出「Type 3」與「Type 4」PSE 及 PD (分別能處理 60 W 和 90 W 功率),以及額外的輸出及輸入功率等級 (5-8) (表 1)。設計人員應該注意,此修訂版的目的是遵守 ISO/IEC 60950 對電力限制型電源以及安全超低電壓 (SELV) 的要求,將每個連接埠的功率上限設為 100 W。

|

表 1:高功率 PoE (IEEE 802.3bt) 與 PoE (IEEE 802.3af) 及 PoE+ (IEEE 802.3at) 的比較。IEEE 802.3bt 不僅引入更高的功率,以及全新類型的 PSE 與 PD,還引入了新的等級。(表格來源:Microsemi)

IEEE 802.3bt 所帶來的增強功能

除了高功率 PoE 帶來更多的電力之外,此規範還引入其他功能。重大增強功能包括:

- 自動分類功能

- 支援低待機功率

- 在通道 (纜線) 長度為已知的情況下支援更高的供電能力

自動分類 (Autoclass) 是高功率 PoE 特有的全新分類機制 (可選配),能讓 PD 向 PSE 傳達其最高的有效功耗,進而讓 PSE 設定功率預算,以精確符合該耗電量 (以及為通道損失以及「安全」餘裕預留的耗電量),提高系統的效率。

為了驅動具有嚴格待機要求的應用,高功率 PoE 對用來確保 PSE 維持電力的最低脈衝電流持續時間做出了重大更改。以前,Type 1 與 Type 2 PD 採用「維持功率特徵 (MPS)」,每 325 ms 至少能供應 10 mA 的脈衝電流 75 ms,而與 0.05 μF 並聯的 AC 阻抗值低於 26.3 kΩ。IEEE 802.3bt 規範做出了一些變動 (適用於 Type 3 與 Type 4 PSE),導致脈衝持續時間是 Type 1 及 Type 2 PSE 的 10%。

另一項重要變化是擴展的功率特點。PD 會量測纜線的電阻並計算功率損耗,進而得出所需的功率保留量,以確保 PD 能接收規範所詳述的最低輸入功率。此值最差頂多等於先前修訂版所指定的功率保留量,但在實際的應用當中可能會更低,從而達到省電作用。

高功率 PoE 啟動

由於引入額外四個等級的 PSE 輸出功率 (Class 5 至 Class 8) 及相應的 PD 輸入功率,以及兩類新型 (Type 3 和 Type 4) 的 PSE 與 PD,這項技術的啟動順序變得更為複雜。這可能會對開發人員設計高功率 PoE 系統以及選擇 PSE 控制器造成影響。

一般來說,符合 IEEE 802.3af 或 IEEE 802.3at 標準的裝置,稱為 Type 1 (Class 0 至 Class 3) 或 Type 2 (Class 4) 裝置。符合 IEEE 802.3bt 標準的裝置,稱為 Type 3 (Class 5、Class 6) 或 Type 4 (Class 7、Class 8) 裝置。高功率 PoE 定義 PSE 如何透過纜線安全地為 PD 供電,然後在 PD 與纜線中斷連接時切斷電源。

此外,IEEE 802.3bt 還規定湧入電流與時間限制,以確保任何類型或等級的 PSE 與 PD 都能相容。對於 Class 0 至 Class 4,湧入電流限制為 400 mA 至 450 mA,Class 5 至 Class 6 為 400 mA 至 900 mA,Class 7 至 Class 8 為 800 mA 至 900 mA。PSE 湧入電流限制會在啟動後作用長達 75 ms。之後,Type 2、Type 3 或 Type 4 PSE 會依據分類支援更高的輸出電流。

高功率 PoE 啟動程序開始後,PSE 會先切斷電源,同時檢查纜線是否已連接任何裝置。接著,PSE 會對 PD 進行分類,然後供應 PD 所要求的電力;如果 PSE 無法為 PD 提供全部供電,則會供應 PSE 的最大功率。Type 3 與 Type 4 PSE 還會使用第四個操作狀態,來檢查 PD 在每對雙絞線上是否具有相同的分類特徵。

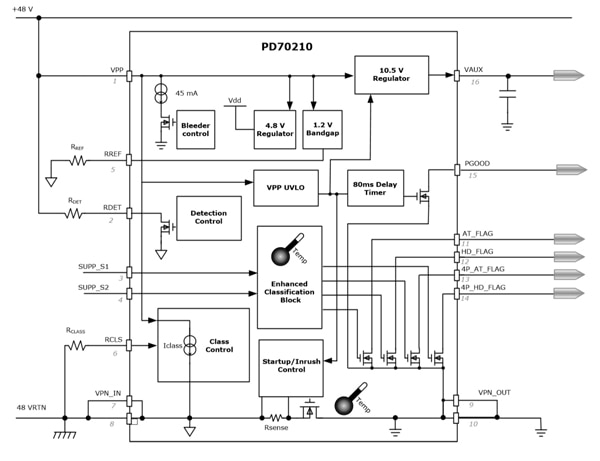

自動分類是可選功能,並非所有符合高功率 PoE 標準的 PSE 和 PD 都支援此功能,因此如果開發人員系統的規格中包含這項功能,則需要檢查規格書。Microsemi 的 PD70210ILD-TR 前端 PD 介面控制器,藉由「增強型分類區塊」做到了這點。此外,PD70210ILD-TR 還會從四對纜線中識別是哪些真正接收電力並產生相應的標示 (圖 1)。

圖 1:Microsemi 的 PD70210ILD-TR 前端 PD 介面控制器內含增強型分類區塊,能輕鬆對高功率 PoE 中引入的新等級與 PD 類型進行分類。此外,該晶片還會透過 SUPP_S1 及 SUPP_S2 引腳,從四對雙絞線中識別是哪些真正接收電力。(圖片來源:Microsemi)

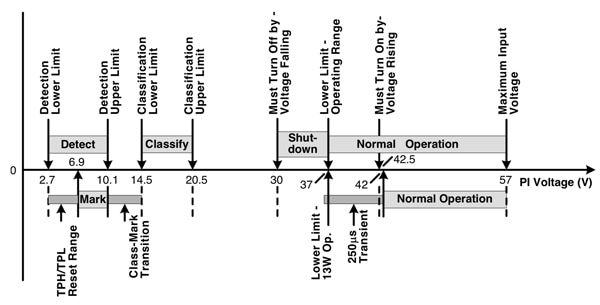

實作自動分類的 PSE,首先會檢查等級電流在短暫的延遲後,是否落至 Class 0 電流位準,以檢查 PD 是否支援自動分類。如果支援,PSE 會在電源啟動後立即繼續進行自動分類測量,而 PD 在接下來的 1.35 至 3.65 秒內需要汲取其最高的功率。PD 在啟動之後必須立即提供 MPS,以向 PSE 確保其仍然連線。失去 MPS 會觸發 PSE 切斷電力 (圖 2)。

圖 2:由於引入新的 PSE 及 PD 等級與類型,因此高功率 PoE 的啟動程序比以前的版本更複雜。此處顯示程序的三個主要階段 (偵測、分類和操作),以及發生這些階段時的輸入電壓。(圖片來源:Texas Instruments)

新款控制器符合高功率 PoE 規範

自從 PoE 獲得批准之後,開發人員便可方便地取得整合式 PSE 控制器以及 PD 介面,並基於這些裝置進行設計。IEEE 802.3bt 延續了這一趨勢。隨著一些製造商設計出符合規範草案的產品,市面上除了上述的 Microsemi 裝置外,還有多款 PSE 控制器與 PD 介面可供選擇。

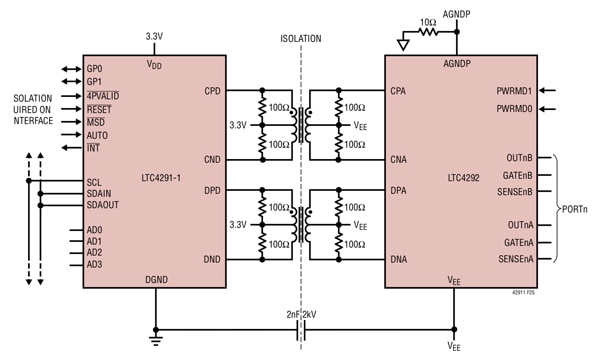

例如,Linear Technology 提供 LTC4291-1/LTC4292 晶片組。這些元件可協同構成 Type 3 或 Type 4 PSE 控制器。其電源管理功能包括每連接埠 14 位元電流監測、可編程電流限制,以及預選連接埠的多用途關斷。PD 偵測採用專屬的多點偵測機制,有助於避免錯誤的 PD 識別。此晶片組除了支援自動分類,也可對引腳或 I2C 進行編程,並在 PD 端協商高達 71.3 W 的功率。

LTC4291-1/LTC4292 晶片組以高整合度而著稱,幾乎包含所有必要的電路,來實作符合 IEEE 802.3bt 標準之 PSE 設計,且只需要幾個額外的周邊裝置。此裝置分為兩個晶片 (處理器以及電源供應器),可將 LTC4291-1 放置在非隔離側,藉此簡化 PSE 隔離。其在此側可從主邏輯電源接收電力,並直接連接到 I2C/SMBus 匯流排。晶片組使用自行研發的隔離機制進行晶片間通訊,利用低成本變壓器來取代光隔離器和隔離式電源供應器。這些變壓器均為 10BASE-T 或 10/100BASE-T 單元,具有 1:1 的匝數比以及共模扼流圈 (圖 3)。

圖 3:Linear Technology 的 LTC4291-1/LTC4292 四埠 IEEE 802.3bt PoE PSE 控制器採用自行研發的隔離機制,利用低成本變壓器來取代光隔離器與隔離式電源供應器,從而簡化了設計。(圖片來源:Linear Technology)

若要充分發揮高功率 PoE 的效能,PD 需要使用 Type 3 或 Type 4 介面,否則 PSE 僅會供應 IEEE 802.3af 所定義的最大功率,即 15.4 W (PD 端為 12.95 W)。對於該介面,一個選擇便是 TI 的 TPS2372-4RGWT。該元件包含實作 IEEE 802.3bt Type 1 至 Type 4 PD 介面所需的所有功能。

由於內部切換阻抗值較低,TPS2372-3 與 TPS2372-4 可分別支援高達 60 W 與 90 W 的高功率 PoE 應用,而其自動 MPS 功能可支援那些需要超低功率待機模式的應用。請注意,IEEE 802.3bt 對 PD 的 MPS 要求適用於纜線的 PSE 端。也就是說,視纜線長度與其他參數 (包含大電容) 而定,可能需要更長的 MPS 持續時間來進行確認。為此,TPS2372 提供三種不同的 MPS 脈衝持續時間與工作週期,可透過其 MPS_DUTY 輸入引腳進行選擇。

TPS2372 實作了與所有 PSE 類型都相容的湧入電流位準。此外,這款晶片還實作了延遲功能,讓 PSE 能夠在釋放電源良好 (PG) 輸出前完成湧入相位,確保達到 IEEE 802.3bt 啟動要求。利用此晶片的自動分類致能輸入,則可使用 IEEE 802.3bt 中規定的所有先進系統功率最佳化模式。

開始使用高功率 PoE

使用 LTC4291-1/LTC4292 等高度整合的晶片組時,雖然許多充滿挑戰性的設計作業已經由矽晶片廠商完成,但還是要仔細選擇外部元件,並且考慮 PC 板佈局準則。除了遵守 PoE 系統設計的一般設計準則之外,還要選擇適當的元件,使其適用於高功率 PoE 所引入的高電壓與高電流位準。

例如,圖 3 中所示的 VDD 與 VEE 線路,便需要用到數位電源供應器以及 PoE 主電源供應器。VDD 需要 3.3 V,而 VEE 則需要負電壓達到 -51 至 -57 V (Type 3 PSE) 或 -53 至 -57 V (Type 4 PSE)。在 VDD 到 DGND 之間應放置一個至少 0.1 μF 的陶瓷解耦電容,並使其盡可能靠近每個 LTC4291-1。為了維持所需的隔離,千萬不要連接 LTC4292 AGNDP 和 LTC4291-1 DGND。

VEE 為主要的隔離 PoE 電源,用於向 PD 供電。由於其供應相當大的電力且容易受到大電流暫態的影響,因此相較於簡單的邏輯電源,需要更小心地進行設計。為了獲得最佳的系統效率,VEE 應設為接近最大振幅 (57 V),僅留下剛好夠的餘裕來應對過衝、欠衝、溫度漂移以及線路調節。AGNDP 與 VEE 之間需要至少 47 μF 的大容量電解電容,以便在發生電氣暫態時,將雜散重置降到最低。

對開發人員來說,選擇外部 MOSFET 是另一個關鍵的設計決策。該 MOSFET 構成控制 PSE 輸出的功率切換裝置。元件的選擇對系統的可靠性具有重要的影響,設計人員必須針對各種 PSE 電流限制條件,來分析和測試 MOSFET 的安全運作範圍 (SOA)。對於設定為在 PD 端提供最高 51 W 功率的 PSE,Linear Technology 建議使用 Nexperia 的 PSMN075-100MSEX,對於在 PD 端提供 71.3 W 功率的 PSE,則建議使用 PSMN040-100MSEX。這些 MOSFET 已證實能在 PoE 應用中可靠地運作。

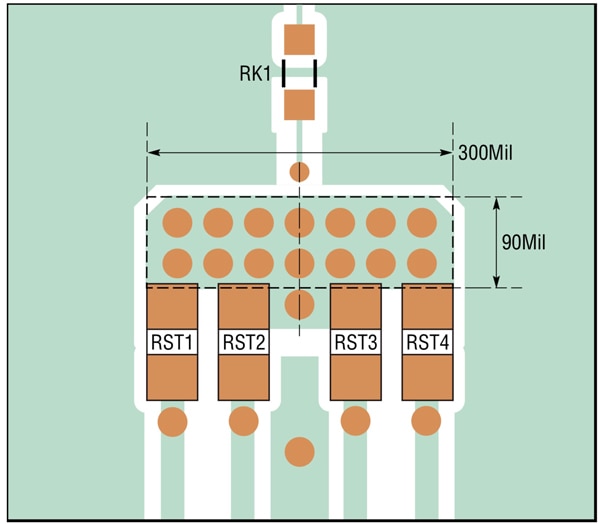

LTC4291-1/LTC4292 晶片組每個通道的電流感應電阻都是 0.15 Ω。開發人員必須加入兩個並聯的 0.3 Ω 電阻,放置方式如圖 4 所示。為了滿足高功率 PoE 規範,這些感應電阻必須具有 ±1% (或更佳) 的容差值,且溫度係數不超過 ±200 ppm/°C。

圖 4:圖中顯示 LTC4292 所需的頂層與底層感測電阻區塊佈局。為了滿足高功率 PoE 規範,感測電阻 (RSTx) 的選擇與放置至關重要。(圖片來源:Linear Technology)

每個連接埠在 OUTnA 和 OUTnB 至 AGNDP 之間需要一個 0.22 μF 的電容 (再次參見圖 3),以在啟動或過載期間,保持 LTC4292 穩定在電流限制內。X7R 陶瓷電容的額定值建議至少為 100 V,且必須放在 LTC4292 的附近。

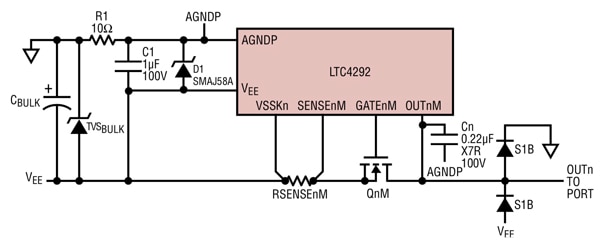

乙太網路埠容易受到大電流暫態的影響。對 PoE 系統提供全面的突波防護,是個很複雜的主題,需要額外單獨撰文說明。不過,至少需要使用暫態電壓抑制 (TVS) 二極體 (TVSBULK) 以及大電容 (CBULK) 等大容量電壓抑制器,將每個連接埠的突波電流與電壓抑制到安全的位準 (圖 5)。此外,在電源 AGND 到 LTC4292 AGNDP 引腳之間還需要放置一個 10 Ω 串聯電阻 (R1)。在 LTC4292 AGNDP 引腳和 VEE 引腳之間應放置一個 58 V 的 TVS 二極體 (D1),並在 LTC4292 引腳附近放置一個 1 μF、100 V 的旁路電容 (C1)。最後,每個連接埠都需要一對 S1B 箝位二極體,一個從 OUTnM 接到電源 AGND,一個從 OUTnM 接到電源 VEE。這些元件會將任何電氣暫態都導入電軌中,並由突波抑制器吸收。

圖 5:PSE 控制器需要抗電氣暫態保護。圖中顯示 Linear Technology 的 LTC4292,此產品具有所需的電壓/電流抑制器與元件,能將電氣暫態導離敏感的晶片。(圖片來源:Linear Technology)

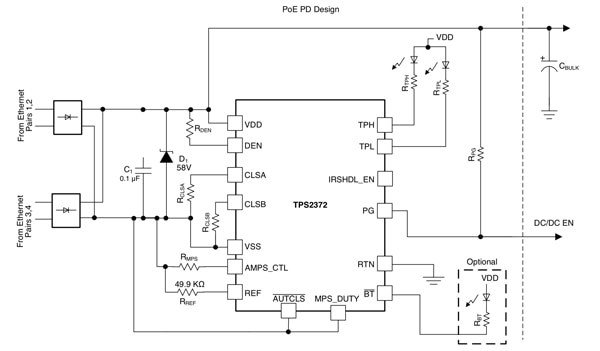

在 PD 介面上,雖然 TI 的 TPS2327 等晶片的高整合度再次為開發人員提供了便利,但還是需要使用一些外部元件 (圖 6)。

例如,PD 介面的纜線輸入端需要使用二極體。對於 TPS2327,TI 建議在高功率 PoE 應用中使用額定值為 3 A 至 5 A、100 V 的離散式或橋式肖特基二極體,而不是傳統的二極體,這是因為這類二極體的功率耗散量降低 30%。開發人員需要考慮到,肖特基二極體的反向漏電流通常比一般 PN 接面二極體要高,因此難以滿足規範中定義的 2.8 V 最大回授電壓。為了補償,應該對這個實作使用保守的二極體工作溫度限制與低漏電元件。與傳統的二極體相比,肖特基二極體更容易受到電氣暫態的影響,因此建議使用鐵氧體磁珠以及電容來保護電壓/電流。

IEEE 802.3bt 規範要求在 VDD 到 VSS 之間使用 0.05 至 0.12 μF 的輸入旁路電容 (通常為 0.1 μF、100 V、±10% 的陶瓷電容)。另外,此規範還要求使用偵測電阻 RDEN、分類電阻 RCLSA 和 RCLSB,以及 MPS 電阻 RMPS。對於 RDEN,建議使用 24.9 kΩ、±1% 的電阻。分類電阻應從 CLSA 與 CLSB 連接到 VSS,以根據 IEEE 802.3bt 標準對分類電流進行編程。這些電阻的值以及分配的等級功率,是由 PD 在運作期間所汲取的最大平均功率所決定。RMPS 設定 MPS 工作週期。例如,1.3 kΩ 的電阻,可將工作週期設為 26.4%。對 MPS_DUTY 到 RSS 短路,可將工作週期設為 12.5%。

另外,高功率 PoE PD 介面需要在電源線上使用 TVS 二極體以及大電容 (D1,CBULK) 電壓抑制元件,以吸收纜線末端的電氣暫態。

圖 6:TI 的 TPS2372 高功率 PoE PD 介面應用示意圖,顯示了完成設計所需的周邊裝置元件,主要包括輸入二極體、抑制元件,以及偵測、分類與 MPS 電阻。(圖片來源:Texas Instruments)

有許多設計準則可確保 PC 板佈局、零件佈局以及配線要求在參數測量準確度、系統可靠性和散熱等方面,滿足 IEEE 802.3bt 規範的要求。Linear Technology 和 TI 都為其 PSE/PD 介面提供了滿足該規範的公版設計,可為開發人員提供實用的指引。

結論

高功率 PoE 不僅延伸了 PoE 的應用範圍,還提高了此類應用的效率。然而,由於引入更多類型和等級的 PSE 控制器與 PD 介面,以及額外的運作與安全功能,實作起來更為複雜。

整合式 PSE 控制器和 PD 介面解決方案將這些功能納入為標準功能,為設計人員提供了極大的便利。這些方案能以更少的周邊裝置元件來完成系統,可大幅簡化並加速設計流程。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。