Unlock the RISC-V Naming Code

The RISC-V instruction set architecture (ISA) provides a unique opportunity. Its structure allows developers to use processors with a wide range of sizes and performance that offer unprecedented software compatibility. The key to leveraging this compatibility is understanding the RISC-V core naming code.

Unlike most processor architectures, RISC-V is open-source, available to developers without licensing or royalty fees. Further, the ISA is designed to be flexible, allowing developers to choose what instruction blocks they wish to implement and omit what they don’t need, even adding custom instructions if desired. The intent is to stimulate the development of multiple processor cores with varying size and performance attributes that share a common basis.

This common basis provides a high level of software compatibility among processors regardless of their feature sets. The code for a minimal RISC-V processor implementing only the integer instruction set, for instance, will run unmodified on a more powerful processor having both integer and floating-point capability. Code that uses the floating-point instructions will not, of course, run on the integer-only machine, but neither will it cause the processor to crash. Unimplemented instructions will simply generate an illegal instruction trap.

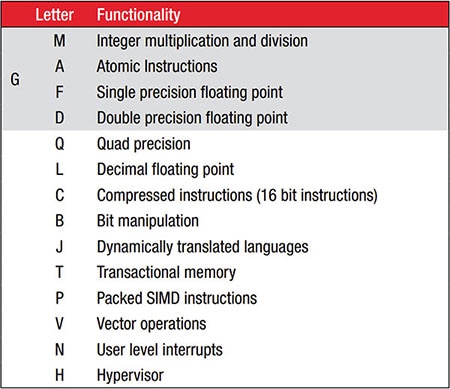

The RISC-V ISA achieves this flexibility by partitioning its instructions into essentially independent groups having machine codes that do not overlap. These instruction groups are called “standard extensions”, and the ISA has defined numerous such standard extensions that provide most of the functionality developers might need. Each standard extension is identified by a letter code. The “M” standard extension, for instance, provides instructions for multiplying or dividing two integer numbers held in registers. Similarly, the “F” standard extension provides instructions for single-precision floating-point operations.

Because processor developers can mix-and-match standard extensions when implementing a RISC-V core, it might seem that users would need to read spec sheets and programming manuals carefully to determine what the processor they intend to design for can actually do. But there is a simpler solution. RISC-V uses a core numbering convention that immediately tells users the core’s capabilities.

The numbering convention starts with the base specification. RISC-V has defined four base specifications:

- RV32I has a 32-bit integer instruction set and offers 32 general purpose registers

- RV32E uses a 32-bit instruction set targeting embedded applications with 16 registers

- RV64I has a 64-bit integer instruction set with 32 registers

- RV128I has a 128-bit integer instruction set with 32 registers

These base specifications define a completely functional, if bare-bones, processor. Most developers, however, will choose to add one or more standard instruction set extensions to their design. These standard extensions and their identifying letters are listed in Figure 1.

Figure 1: The standard instruction set extensions for RISC-V processors use letter codes to denote their presence in a core’s numbering convention. (Image source: DigiKey)

Figure 1: The standard instruction set extensions for RISC-V processors use letter codes to denote their presence in a core’s numbering convention. (Image source: DigiKey)

A complete RISC-V core designation gives the base specification appended with the letters of the standard extensions it implements, in the order listed in Figure 1. A small SoC using minimal resources, then, might have the designation RV32EMAB. This means the core implements the 32-bit integer instruction set for embedded devices, has 16 registers and runs integer multiplication and division as well as atomic instructions. It has no floating-point math but does support bit manipulation.

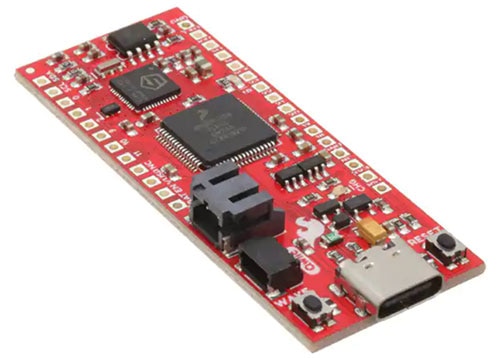

Thus, when choosing a RISC-V chip for their design, users need only to look at the core designation to understand what functionality it provides. For example, the processor in SparkFun Electronics’ DEV-15799 FE310 Thing Plus RISC-V evaluation board is listed as an RV32IMAC core (Figure 2).

Figure 2: The DEV-15799 board’s RISC-V processor is named the RV32IMAC, meaning, among other features, it has a 32-bit integer instruction set, 32 registers, and offers atomic instructions. (Image source: SparkFun Electronics)

Figure 2: The DEV-15799 board’s RISC-V processor is named the RV32IMAC, meaning, among other features, it has a 32-bit integer instruction set, 32 registers, and offers atomic instructions. (Image source: SparkFun Electronics)

This means it has a 32-bit integer instruction set, 32 registers, implements integer multiplication and division, offers atomic instructions, and supports compressed (16 bit) instructions to minimize code space. Any code developed on this board will be able to run on any other RV32I core with the multiply and accumulate (MAC) standard extensions as well.

In another example, Seeed Technology’s 114991684 Sipeed MAXIX-I RISC-V SoC module lists its RISC-V core as an RV64IMAFDC. It has a 64-bit instruction set with integer multiply and divide, atomic instructions, single and double-precision floating-point, and compressed instructions. Code developed for this processor should run on any RISC-V processor with the same core designations, although the memory mapping of peripherals and such might need to be adjusted.

Conclusion

With the RISC-V naming code in hand, users are well-positioned to confidently begin experimenting with this powerful architecture. By matching core codes, users can be sure that their programming efforts with one processor will be highly portable to other RISC-V processors.

A great place to begin this experimentation might be to check out the Guide to RISC-V, which walks through the initial setup and use of several different RISC-V evaluation boards.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum