使用合適的切換式穩壓器,達到高效率、低電軌雜訊、快速暫態響應

資料提供者:DigiKey 北美編輯群

2025-06-26

在依賴低訊號位準類比電路的無線連接等應用,以及具有低電源軌電壓的數位設計中,直流軌的品質是維持系統效能的關鍵要素。直流電源軌的品質除了考量轉換效率、輸出準確度、穩定性以及線路和負載調節之外,還取決於其固有雜訊和對動態負載變化的暫態響應。

Analog Devices 強大的 Silent Switcher 系列經過多代演變,此技術只要正確運用,即可提供必要的低雜訊直流輸出和超快速暫態響應。

本文著重於介紹這些容易使用的高效能 DC/DC 切換式穩壓器,包含可解決的問題以及所具備的優勢。以 Analog Devices 的應用為例,展示如何達到最高效能。

Silent Switcher 系列

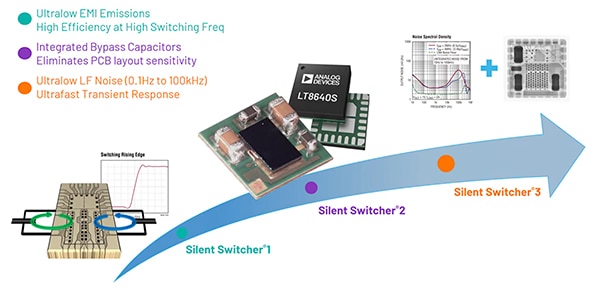

Analog Devices 的 Silent Switcher 系列 DC/DC 切換式穩壓器現已發展到第三代。第一代的 Silent Switcher 1 專注於降低與切換式穩壓器相關的高頻雜訊。亦提供三個關鍵優勢:低電磁干擾 (EMI)、高效率、高切換頻率 (適用於較小的相關組件)。

Analog Devices 接著推出的 Silent Switcher 2,保留前代產品的特點,並添加整合式精密電容、更緊湊的外形尺寸,以及消除對印刷電路板 (PCB) 佈局的敏感性。

第三代 Silent Switcher 3 以前兩代產品的獨特功能為基礎,增加快速暫態響應和低頻帶超低雜訊等優勢 (圖 1)。

圖 1:Silent Switcher DC/DC 穩壓器的每一代產品都保留前代產品的特點和功能,並進一步擴展。(圖片來源:Analog Devices)

圖 1:Silent Switcher DC/DC 穩壓器的每一代產品都保留前代產品的特點和功能,並進一步擴展。(圖片來源:Analog Devices)

Simple Switcher 雜訊解決方案

要達到前兩代產品的低雜訊,設計人員檢驗各種雜訊源,並探索創新的方法加以避開,或最小化雜訊甚至予以消除。這需要從各個角度切入。例如,在切換式電源供應器中的主要雜訊源為電流切換,而非穩態電流。在傳統的切換式穩壓器拓撲中,有一個稱為熱迴路的電流路徑。熱迴路是高頻雜訊的主要來源;此雜訊會發射到空氣中,產生 EMI。第一代 Silent Switcher DC/DC 穩壓器以創新方式,將熱迴路分成兩個對稱的電流迴路。如此產生兩個極性相反的磁場,讓輻射雜訊盡可能相互抵消。

Silent Switcher 2 把輸入電容直接整合到 IC 封裝中,將關鍵熱迴路縮至最短。

此架構支援以高切換頻率快速切換邊緣來達到高效率,同時達到良好的 EMI 效能。DC 輸入電壓 (VIN) 採用內部陶瓷電容,可確保所有快速 AC 電流迴路夠小,進一步提升效能。Silent Switcher 架構亦採用自行研發的設計與封裝技術,可在極高頻率下發揮最大效率,並通過 CISPR 25 Class 5 峰值 EMI 限制。

此外,亦採用主動電壓定位 (AVP) 技術,會依據負載電流決定輸出電壓。在輕負載下,輸出電壓會調節至高於標稱值;在滿載下,輸出電壓會調節至低於標稱值。直流負載會進行調整,以提高暫態效能,並將輸出電容的要求降至最低。

Silent Switcher 3 和暫態響應

暫態響應是指穩壓器回應負載突然變化的能力,現在已經成為越來越重要的參數。因此,第三代除了能將低頻雜訊 (10 Hz 至 100 kHz) 降至超低,還重視提供超快速暫態響應。

人們對暫態響應越加重視,這是因為訊號處理單元和系統單晶片 (SoC) 經常會出現突然變化的負載暫態曲線。這種負載暫態會干擾電源電壓,在高效能 RF 設計中尤其需要注意。例如,電源電壓變化將明顯影響系統時脈頻率。

因此,RF SoC 通常在負載暫態期間施加遮沒時間。在 5G 應用中,轉換期的遮沒時間對於資訊品質有極大關聯。將電源供應器上的負載暫態影響降低,可提升系統級效能。

為了達成這些目標,單晶片 Silent Switcher 3 裝置採用超高效能誤差放大器設計,即使在激進補償下,也能提供額外的穩定性。最大切換式頻率為 4 MHz,能讓 IC 在固定頻率峰值電流控制模式下,將控制迴路頻寬擴大至數百 kHz 範圍。此外,還有多項創新可緩減對暫態響應造成的影響:

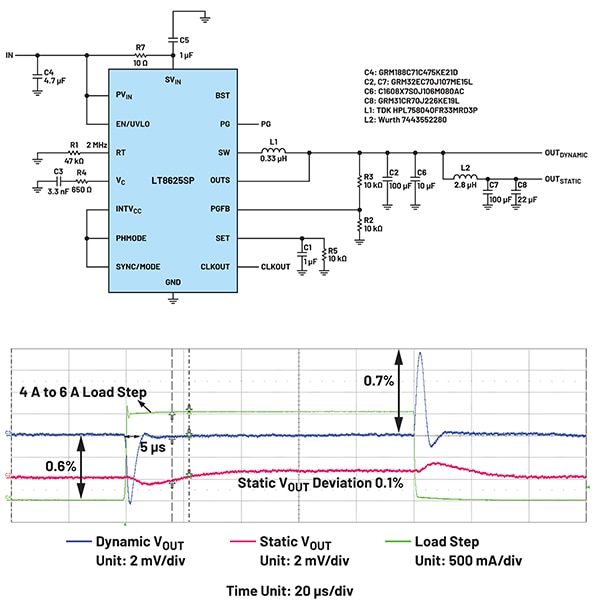

負載分離 - 典型設計中,1 V 負載由發射和接收電路、局部振盪器 (LO)、壓控振盪器 (VCO) 組成。在分頻雙工 (FDD) 作業期間,發射/接收負載會經歷負載電流的突然變化。同時,LO 和 VCO 承受恆定負載,但需要高準確度和低雜訊。

這些元件的高頻寬特性讓設計人員能夠以第二個電感 (L2) 分離動態和靜態負載,從穩壓器 IC 為兩個關鍵的 1 V 負載組供電 (圖 2,上)。 負載暫態響應很快,VOUT 偏差極小,且不會影響靜態負載 (圖 2,下)。

圖 2:Silent Switcher 的應用電路,此電路使用電感 (L2) 隔離動態和靜態 RF 負載,以增強效能 (上);負載暫態響應快速,具有最小 VOUT 偏差,並且不會影響靜態負載 (下)。(圖片來源:Analog Devices)

圖 2:Silent Switcher 的應用電路,此電路使用電感 (L2) 隔離動態和靜態 RF 負載,以增強效能 (上);負載暫態響應快速,具有最小 VOUT 偏差,並且不會影響靜態負載 (下)。(圖片來源:Analog Devices)

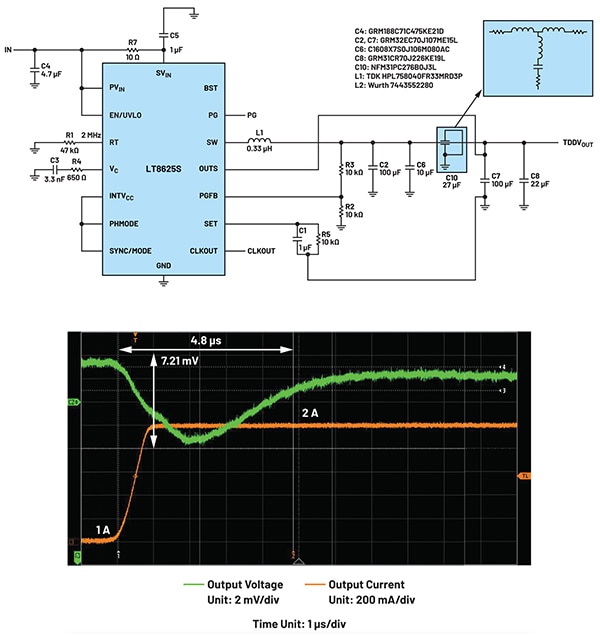

採用最小化等效電感進行後濾波-在分時雙工 (TDD) 模式下,對雜訊敏感的 LO 和 VCO 會隨著發射/接收模式的變化而加載和卸載。由於所有負載都被視為動態,因此可以使用簡化的電路;同時,需要更關鍵的後濾波以保持 LO 和 VCO 的低漣波和雜訊特性。

饋通模式下的三端電容可以用最小的等效電感,達到足夠的後濾波效果,進而保持負載暫態的快速頻寬 (圖 3,上)。饋通電容與遠端輸出電容一同形成兩個額外的電感-電容 (LC) 濾波器級。所有的電感都是由三端電容的等效串聯電感 (ESL) 引起,此電感非常小,且對負載暫態的危害較小。饋通電容可增強暫態響應,同時將輸出電壓漣波減至最低 (圖 3,下)。

圖 3:動態/靜態 RF 負載組合的應用電路;此電路使用三端子饋通電容 (右上) 提供後濾波,並具有最小等效電感,可為負載暫態保持快速頻寬。饋通電容增強暫態響應,同時將輸出電壓漣波降至最低 (下)。(圖片來源:Analog Devices)

圖 3:動態/靜態 RF 負載組合的應用電路;此電路使用三端子饋通電容 (右上) 提供後濾波,並具有最小等效電感,可為負載暫態保持快速頻寬。饋通電容增強暫態響應,同時將輸出電壓漣波降至最低 (下)。(圖片來源:Analog Devices)

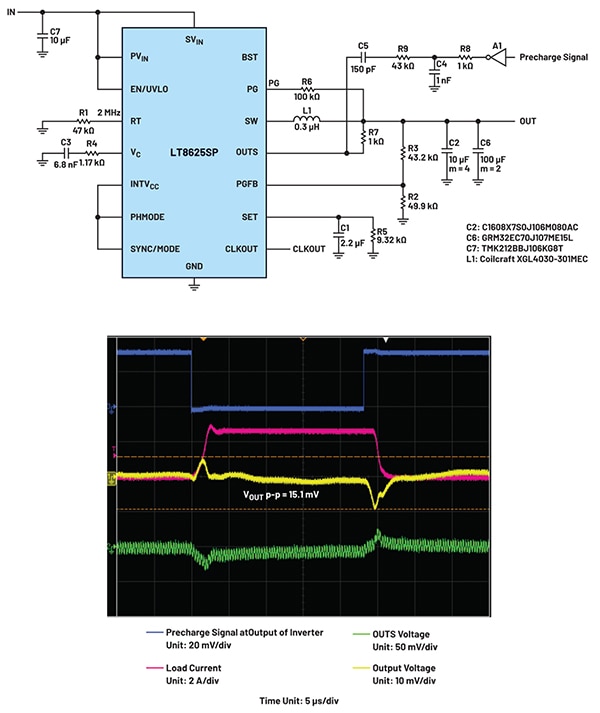

預充電-在某些情況下,訊號處理單元具有一般用途 I/O(GPIO);此外,訊號處理已排程進行,且可預先得知暫態事件。這通常會在一些 FPGA 電源供應器設計中,可產生預充電訊號,輔助供應器的暫態響應。

在典型的應用電路中 (圖 4,上),若 FPGA 產生預充電訊號,在實際負載前提供偏壓,則該轉換允許裝置有額外的時間適應負載擾動,同時最大程度減少 VOUT 偏差和恢復 (圖 4,下)。

圖 4:饋入誤差放大器負輸入引腳 (OUTS) 的預充電訊號,用於產生快速暫態響應;穩壓器的回授同時受到預充電訊號和負載暫態的影響 (下)。(圖片來源:Analog Devices)

圖 4:饋入誤差放大器負輸入引腳 (OUTS) 的預充電訊號,用於產生快速暫態響應;穩壓器的回授同時受到預充電訊號和負載暫態的影響 (下)。(圖片來源:Analog Devices)

主動下降-在波束成形器應用中 (圖 5,上),電源電壓會持續變化,適應不同的功率等級。因此,電源電壓的準確度通常要求為 5% 至 10%。在此應用中,穩定性比電壓準確度更重要,因為將負載暫態的恢復時間縮至最短可大幅提升資料處理效率。下降電路非常適合此應用,因為下降電壓將減少甚至消除恢復時間 (圖 5,下)。

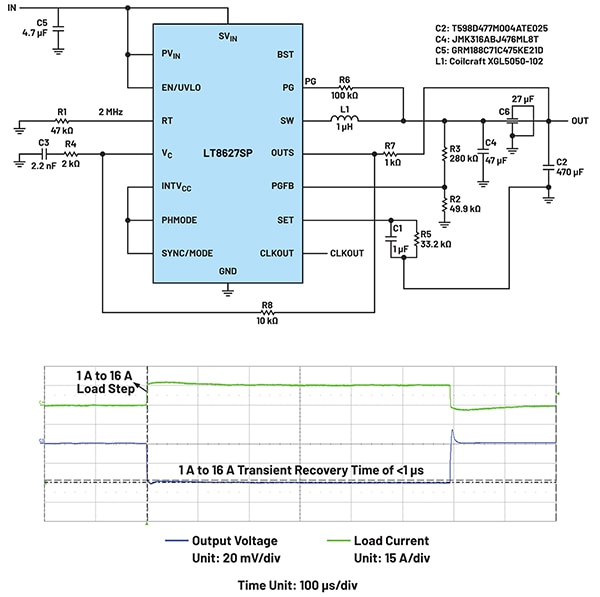

圖 5:在 OUTS 和 VC 之間放置一個主動下降電阻 (R8) 有助於達到快速暫態恢復 (上);下降暫態響應可以自訂,大幅縮短暫態恢復時間 (下)。(圖片來源:Analog Devices)

圖 5:在 OUTS 和 VC 之間放置一個主動下降電阻 (R8) 有助於達到快速暫態恢復 (上);下降暫態響應可以自訂,大幅縮短暫態恢復時間 (下)。(圖片來源:Analog Devices)

元件實作及驗證創新

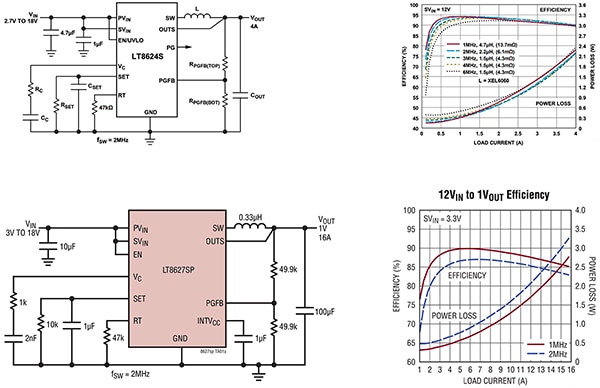

在單晶片 Silent Switcher 3 系列元件中已納入這些雜訊抑制和暫態改善的概念。此系列支援各種電壓和電流最大值,同時為使用者提供無須妥協的靈活性和效能。由以下兩例清楚說明:LT8622SAV#PBF (圖 6,上) 和 LT8627SPJV#TRPBF (圖 6,下)。

LT8622SAV#PBF 在電流和功率範圍的低端,是 2 A 連續輸出切換器,適用於 2.7 V 至 18 V 的輸入。其輸出電壓範圍為 0 V 至 VIN - 0.5 V,能以單一電阻進行編程。其大部分輸出電流範圍內的效率至少為 90%,最高可達 95%。

圖 6:典型應用配置中的 2 A LT8622,以及其效率和功率損耗曲線 (上) (註:LTC8624 與 LT8622 的線路圖相同,有相同的曲線,但額定電流為 4 A);圖中亦顯示 16 A LT8627 的相同資訊 (下)。(圖片來源:Analog Devices)

圖 6:典型應用配置中的 2 A LT8622,以及其效率和功率損耗曲線 (上) (註:LTC8624 與 LT8622 的線路圖相同,有相同的曲線,但額定電流為 4 A);圖中亦顯示 16 A LT8627 的相同資訊 (下)。(圖片來源:Analog Devices)

LT8622SAV#PBF 在切換式穩壓器中提供絕佳的低頻 (0.1 Hz 至 100 kHz) 輸出雜訊效能,其 RMS 雜訊僅 4 μVRMS。工作頻率可在 300 kHz 至 6 kHz 內同步調節。此元件納入小型 20 引線 4 mm × 3 mm LQFN 封裝。

功率較高的 16 A LT8627SPJV#TRPBF 的輸入電壓為 2.8 V 至 18 V,而輸出電壓可透過電阻調節範圍為 0 至 VIN - 0.5 V。效率超過 80%,在 1 MHz 切換式頻率的中間範圍最佳點達到 90%。其低頻輸出雜訊效能與 2 A LT8622SAV#PBF 相同。

工作頻率也可調,在 300 kHz 至 4 MHz 範圍內運作和同步,低於其低電流同類產品的頻率。其封裝是稍大的 24 引線 4 mm × 4 mm LQFN,背面裸露,可選用散熱片。

結論

創新產品的設計人員要求高效率,尤其是在尖端的 RF 領域中,但必須伴隨電源電壓的低雜訊和快速暫態響應。Analog Devices 的 Silent Switcher 3 系列 DC/DC 穩壓器是新一代高效能單晶片元件,針對多種應用中的雜訊敏感、動態負載暫態效能經過最佳化。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。