使用 FPGA 捷徑打造高效能、低功耗的邊緣 AI 應用

資料提供者:DigiKey 北美編輯群

2021-01-12

對於想要在邊緣的推斷處理器上實作人工智慧 (AI) 演算法的開發人員來說,單單為了降低功耗和縮短開發時間就已承受了巨大的壓力,偏偏處理需求還不斷增加。現場可編程閘極陣列 (FPGA) 所提供的速度和功率效率組合,能夠有效實作邊緣 AI 所需的神經網路 (NN) 推斷引擎。然而,對於不熟悉 FPGA 的開發人員來說,傳統的 FPGA 開發方式可能比較複雜,往往導致開發人員改用次佳的解決方案。

本文將介紹 Microchip Technology 使用的一種簡化作法,可讓開發人員擺脫傳統的 FPGA 開發方式,直接使用 FPGA 和軟體開發套件 (SDK) 來建立已訓練的神經網路;或者使用 FPGA 影像套件,立即開始開發智慧型嵌入式視覺應用。

為何要在邊緣使用 AI?

在工業自動化、安全系統、智慧家庭等不同領域的物聯網 (IoT) 應用中,邊緣運算可以帶來許多好處。在針對廠區的工業物聯網 (IIoT) 應用中,邊緣運算可消弭雲端型應用的往返延遲,大幅改善流程控制迴路中的反應時間。同樣地,即使雲端連線遭意外或蓄意中斷,邊緣型安全系統或智慧家庭門鎖仍可持續運作。在許多情況下,在這些應用中使用邊緣運算,可以減少產品對雲端資源的依賴,有助於降低總營運成本。當產品需求突然增加時,開發人員可以仰賴產品內建的本機處理能力,以維持穩定的營運支出,而無須新增昂貴的雲端資源。

由於機器學習 (ML) 推斷模型迅速廣受採用,並且這方面的需求不斷增加,邊緣運算的重要性便大幅提升。對於開發人員來說,本機處理推斷模型不僅有助於降低反應延遲,亦可降低雲端型推斷所需的雲端資源成本。對使用者來說,即使網路連線偶有中斷,或產品供應商的雲端型產品供貨發生了變化,使用本機推斷模型讓他們有信心能夠維持產品運作。此外,安全和隱私方面的疑慮可進一步帶動本機處理和推斷的需求,藉以限制透過公共網路傳輸敏感資訊到雲端的數量。

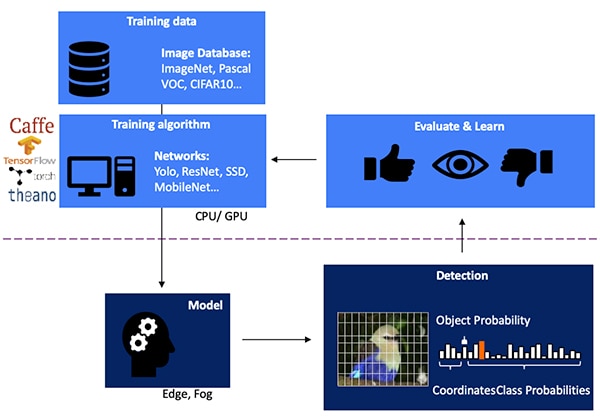

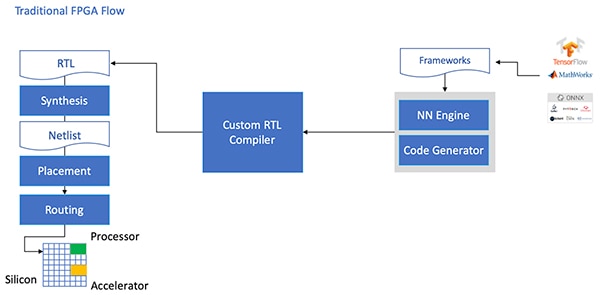

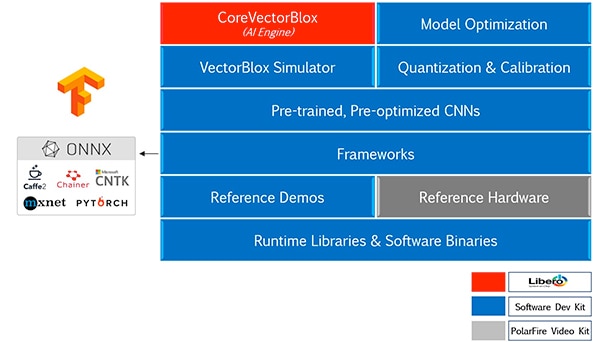

開發視覺型物件偵測用的神經網路推斷模型是一個多步驟流程;本流程首先需進行模型訓練,一般均在 TensorFlow 等機器學習框架上使用公開可用的標示圖像或客製化標示圖像進行訓練。為因應處理需求,通常會透過雲端或其他高效運算平台的圖形處理單元 (GPU) 來訓練模型。一旦訓練完成,模型會轉換成能在邊緣或霧運算等資源上運作的推斷模型,並以一組物件類型機率呈現推斷結果 (圖 1)。

圖 1:此多步驟過程最後要實作邊緣 AI 推斷模型,其中需要使用現有或客製化訓練資料框架,以便針對神經網路進行訓練和最佳化。(圖片來源:Microchip Technology)

圖 1:此多步驟過程最後要實作邊緣 AI 推斷模型,其中需要使用現有或客製化訓練資料框架,以便針對神經網路進行訓練和最佳化。(圖片來源:Microchip Technology)

為什麼推斷模型會有運算瓶頸

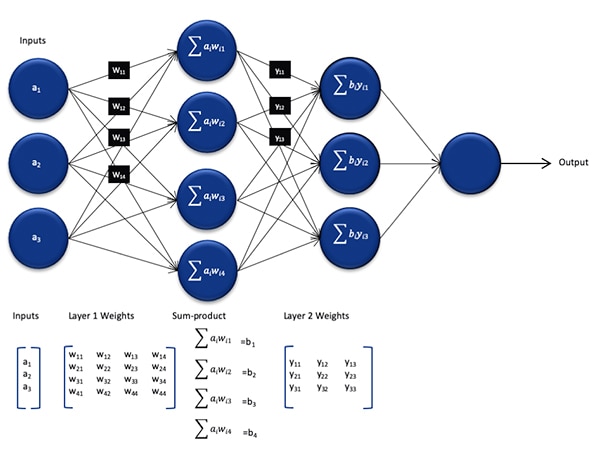

與訓練過程使用的模型相比,神經網路推斷模型的大小和複雜性儘管較低,但由於需要進行大量運算,因此對於一般用途的處理器而言,建立神經網路推斷模型仍會遭遇運算瓶頸。一般而言,深度神經網路模型是由多層神經元組成。在全連接神經網路的每一層中,每個神經元 nij 需要計算每個輸入值和相關權重 wij 之乘積的總和 (圖 2)。

圖 2:神經網路推斷所需的計算量可能會大幅增加運算工作量。(圖片來源:Microchip Technology)

圖 2:神經網路推斷所需的計算量可能會大幅增加運算工作量。(圖片來源:Microchip Technology)

圖 2 並未顯示啟用函式所增加的額外運算需求。此函式用於將負值對應為 0,將大於 1 的值對應為 1 以及類似功能,以此修改每個神經元的輸出值。每個神經元 nij 啟用函式的輸出值,將成為下一層 (i+1) 的輸入值,每層神經元均保持相同的運作方式。最後,神經網路模型的輸出層產生一個輸出向量,代表原始輸入向量 (或矩陣) 對應至監督式學習過程中所用的其中一個類別 (或標籤) 機率。

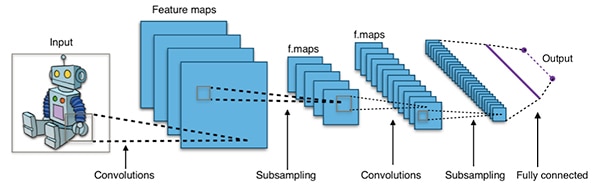

要建立有效的神經網路模型,其架構大小和複雜度將超越上述具代表性的一般神經網路架構。例如,用於圖像物件偵測的卷積神經網路 (CNN),係採用區塊的方式應用這些原理。卷積神經網路將對輸入圖像的寬度、高度和顏色深度進行掃描,產生一系列特徵對應圖,最終產生輸出預測向量 (圖 3)。

圖 3:用於圖像物件偵測的 卷積神經網路在許多層裡包含大量的神經元,對運算平台的要求更高。(圖片來源:Aphex34 CC BY-SA 4.0)

圖 3:用於圖像物件偵測的 卷積神經網路在許多層裡包含大量的神經元,對運算平台的要求更高。(圖片來源:Aphex34 CC BY-SA 4.0)

使用 FPGA 加速神經網路數學運算

儘管在邊緣執行推斷模型的選擇日新月異,但要在邊緣進行實用的高速推斷功能必須兼具靈活性、效能和節能等方面,而能夠提供這些條件的替代方案卻寥寥無幾。在眾多現成的邊緣 AI 替代方案中,FPGA 尤其有效,因為這類產品可以執行高效能硬體型運算密集式操作,而且消耗電力相對較少。

儘管 FPGA 具備多項優點,但沒有豐富 FPGA 經驗的開發人員,可能會因為傳統開發流程而感到卻步,因而捨棄 FPGA。為了建立能有效實作 FPGA 的神經網路模型 (模型由神經網路框架產生),開發人員需要瞭解的細微差別在於,將模型轉換為暫存器傳輸語言 (RTL)、合成設計,以及完整運作流程,最後導向實體設計階段,以產生最佳化實作 (圖 4)。

圖 4:為了在 FPGA 上實作神經網路模型,開發人員現在需要瞭解如何將其模型轉換成暫存器傳輸語言,並透過傳統的 FPGA 流程來運作。(圖片來源:Microchip Technology)

圖 4:為了在 FPGA 上實作神經網路模型,開發人員現在需要瞭解如何將其模型轉換成暫存器傳輸語言,並透過傳統的 FPGA 流程來運作。(圖片來源:Microchip Technology)

Microchip Technology 透過自家的 PolarFire FPGA、專用軟體和相關智慧財產 (IP) 提供一款解決方案,可讓不具備 FPGA 經驗的開發人員也可以廣泛使用高效能、低功率的邊緣推斷功能。

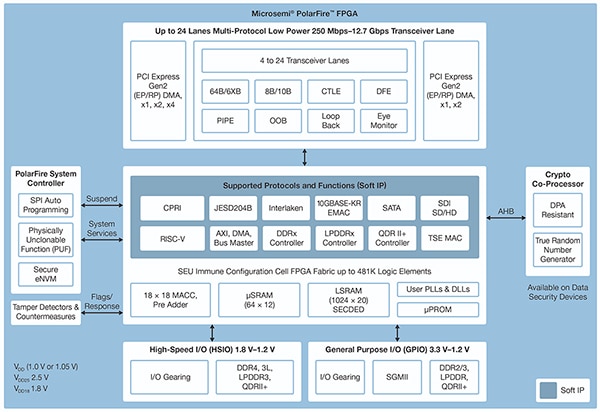

PolarFire FPGA 採用先進的非揮發性製程技術,旨在最大程度地提高靈活性和效能,同時將功耗降至最低。除了用於通訊和輸入/輸出 (I/O) 的大量高速介面外,這款產品還具有深度的 FPGA 結構,能夠支援使用軟體 IP 核心的進階功能,包括 RISC-V 處理器、進階記憶體控制器和其他標準介面子系統 (圖 5)。

圖 5:Microchip Technology 的 PolarFire 架構提供了一種深度結構,旨在滿足高效能設計需求,包括密集運算型推斷模型的實作。(圖片來源:Microchip Technology)

圖 5:Microchip Technology 的 PolarFire 架構提供了一種深度結構,旨在滿足高效能設計需求,包括密集運算型推斷模型的實作。(圖片來源:Microchip Technology)

PolarFire FPGA 結構提供眾多邏輯元件和專用區塊,其中有 PolarFire FPGA 系列的不同產品支援的眾多功能,系列產品包括 MPF100T、MPF200T、MPF300T 和 MPF500T (表 1)。

|

表 1:PolarFire 系列提供的各式 FPGA 結構特點和功能。(表格來源:DigiKey 基於 Microchip Technology 的 PolarFire 規格書)

在眾所矚目的推斷加速功能中,PolarFire 架構包括一個專用的數學區塊,其中包括了 18 位元 × 18 位元簽署的乘積累加運算能力 (MAC) (含預加器)。內建的點積模式使用單個數學區塊來執行兩個 8 位元乘積運算,該模式提供的機制,可利用模型精度量化影響可忽略不計的優點,來增加運作能力。

除了加速數學運算之外,PolarFire 架構還能有助於緩解在一般用途架構上實作推斷模型時所遇到的記憶體壅塞問題。例如,神經網路演算法執行過程產生的中間結果,可儲存在小型分散式記憶體中。此外,神經網路模型的權重和偏移值可以儲存在一個深度為 16 的 18 位元係數唯獨記憶體 (ROM) 中,此記憶體是由數學區塊附近的邏輯元件構成。

若與其他的 PolarFire FPGA 結構特性相結合,則數學區塊可為 Microchip Technology 更高等級的 CoreVectorBlox IP 提供所需的基礎。此為彈性的神經網路引擎,能夠執行不同類型的神經網路。除了一組控制暫存器之外,CoreVectorBlox IP 還包括三個主要功能區塊:

- 微控制器:這個簡易型的 RISC-V 軟體處理器,可從外部儲存裝置讀取 Microchip 韌體二進位的大型物件 (BLOB) 和使用者特定的神經網路 BLOB 檔案。此處理器可執行來自韌體 BLOB 的指令,控制整個 CoreVectorBlox 的運算。

- 矩陣處理器 (MXP):軟體處理器由八個 32 位元算數邏輯單元 (ALU) 組成,此處理器將視需要使用混合的 8 位元、16 位元和 32 位元精確度,並透過逐元素張量運算 (add、sub、xor、shift、mul、dotprod 等其他運算子),對資料向量執行平行運算。

- 卷積神經網路加速器:使用二維陣列 MAC 功能來加速 MXP 運算;MAC 功能則是使用數學區塊並以 8 位元精確度運算來實作。

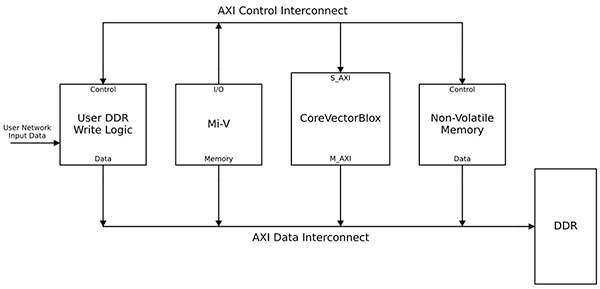

完整的神經網路處理系統將合併 CoreVectorBlox IP 區塊、記憶體、記憶體控制器和主機處理器 (如 Microsoft RISC-V (Mi-V) 軟體處理器核心) (圖 6)。

圖 6:CoreVectorBlox IP 區塊可配合 Microchip 的 Mi-V RISC-V 微控制器等主機處理器使用,以實作神經網路推斷模型。(圖片來源:Microchip Technology)

圖 6:CoreVectorBlox IP 區塊可配合 Microchip 的 Mi-V RISC-V 微控制器等主機處理器使用,以實作神經網路推斷模型。(圖片來源:Microchip Technology)

在視訊系統實作中,主機處理器將從系統快閃記憶體中載入韌體和網路 BLOB,並將兩者複製到雙倍數據傳輸率 (DDR) 隨機存取記憶體 (RAM) 中,以供 CoreVectorBlox 區塊使用。當視訊訊框傳輸抵達時,主機處理器會將訊框寫入 DDR RAM,並向 CoreVectorBlox 區塊傳送訊號,以便開始處理圖像。在 CoreVectorBlox 區塊執行了網路 BLOB 中定義的推斷模型後,會將包含圖像分類在內的結果寫入 DDR RAM 中,以供目標應用使用。

開發流程簡化了神經網路 FPGA 的實作

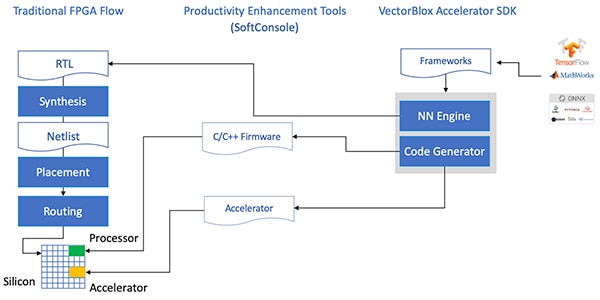

Microchip 消弭了開發人員在 PolarFire FPGA 實作神經網路推斷模型時所面臨的複雜性。神經網路模型開發人員不必再處理傳統 FPGA 流程的相關細節,而是如往常一樣使用神經網路架構,並將產生的模型載入 Microchip Technology 的 VectorBlox Accelerator 軟體開發套件 (SDK) 當中。SDK 產生所需的檔案集 (包括正常 FPGA 開發流程所需的檔案集),以及先前提及的韌體和網路 BLOB 檔案 (圖 7)。

圖 7:VectorBlox Accelerator SDK 可在 FPGA 上實作神經網路模型時管理相關細節,此套件可自動產生設計並執行 FPGA 型推斷模型所需的檔案。(圖片來源:Microchip Technology)

圖 7:VectorBlox Accelerator SDK 可在 FPGA 上實作神經網路模型時管理相關細節,此套件可自動產生設計並執行 FPGA 型推斷模型所需的檔案。(圖片來源:Microchip Technology)

由於 VectorBlox Accelerator SDK 流程會將神經網路設計覆蓋至 FPGA 中實作的神經網路引擎上,因此不同的神經網路可在同一 FPGA 設計上執行,無需重做 FPGA 設計合成流程。開發人員可以為產生的系統建立 C/C++ 程式碼,並且能在系統內即時切換模型,或於使用時間切片的同時執行模型。

VectorBlox Accelerator SDK 集結了 Microchip Technology 的 Libero FPGA 設計套件與神經網路推斷模型開發用的綜合功能組。除了模型最佳化、量化和校準服務外,SDK 還提供了一個神經網路模擬器,可讓開發人員在將模型用於 FPGA 硬體實作之前,使用相同的 BLOB 檔案來評估模型 (圖 8)。

圖 8:VectorBlox Accelerator SDK 提供了一套完整的服務,旨在將架構產生之推斷模型的 FPGA 實作進行最佳化。(圖片來源:Microchip Technology)

圖 8:VectorBlox Accelerator SDK 提供了一套完整的服務,旨在將架構產生之推斷模型的 FPGA 實作進行最佳化。(圖片來源:Microchip Technology)

VectorBlox Accelerator SDK 支援開放神經網路交換 (ONNX) 格式模型,以及來自其他多種架構的模型,包括 TensorFlow、Caffe、Chainer、PyTorch 和 MXNET。可支援的卷積神經網路架構包括 MNIST、各種 MobileNet 版本、ResNet-50、Tiny Yolo V2 和 Tiny Yolo V3。Microchip 正在努力擴展支援範圍,將大多數網路納入預先訓練模型中的開源 OpenVINO toolkit open model zoo 中,包括 Yolo V3、Yolo V4、RetinaNet 和 SSD-MobileNet。

影像套件展示了 FPGA 的推斷能力

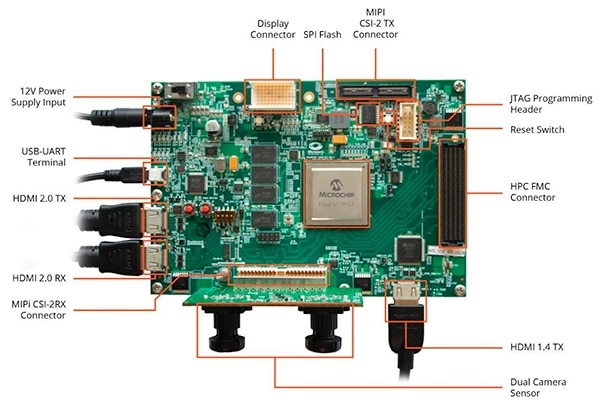

為了幫助開發人員立即開發智慧型嵌入式視覺應用,Microchip Technology 提供了一個全面的範例應用,旨在執行在該公司的 MPF300-VIDEO-KIT PolarFire FPGA 影像和圖像套件和公版設計。

該套件的電路板以 Microchip 的 MPF300T PolarFire FPGA 為基礎,結合雙相機感測器、雙倍數據傳輸率 4 (DDR4) RAM、快閃記憶體、電源管理和各種介面 (圖 9)。

圖 9:MPF300-VIDEO-KIT PolarFire FPGA 影像和圖像套件以及相關軟體,使開發人員在智慧型嵌入式視覺應用中快速使用 FPGA 型推斷功能。(圖片來源:Microchip Technology)

圖 9:MPF300-VIDEO-KIT PolarFire FPGA 影像和圖像套件以及相關軟體,使開發人員在智慧型嵌入式視覺應用中快速使用 FPGA 型推斷功能。(圖片來源:Microchip Technology)

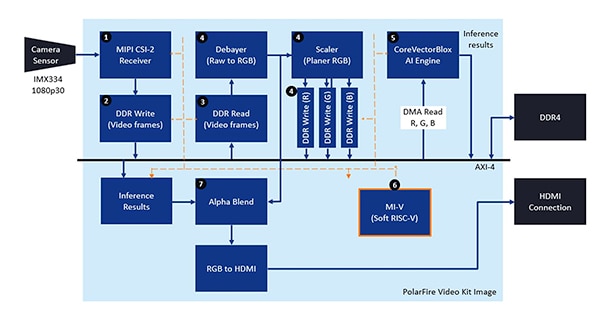

該套件隨附一個完整的 Libero 設計專案,可用來產生韌體和網路 BLOB 檔案。將 BLOB 檔案編程到板載快閃記憶體後,開發人員按一下 Libero 中的執行按鈕即可開始展示,展示過程將處理相機感測器拍攝的影片圖像,並在顯示器上顯示推斷結果 (圖 10)。

圖 10:Microchip Technology 的 PolarFire FPGA 影像和圖像套件展示了如何設計並使用 FPGA 實作,以便打造出一個以 Microchip 的 CoreVectorBlox 神經網路引擎為主的智慧型嵌入式視覺系統。(圖片來源:Microchip Technology)

圖 10:Microchip Technology 的 PolarFire FPGA 影像和圖像套件展示了如何設計並使用 FPGA 實作,以便打造出一個以 Microchip 的 CoreVectorBlox 神經網路引擎為主的智慧型嵌入式視覺系統。(圖片來源:Microchip Technology)

對於每個輸入視訊訊框,FPGA 型系統將執行以下步驟 (步驟編號與圖 10 對應):

- 從相機載入訊框

- 將訊框儲存在 RAM 中

- 從 RAM 讀取訊框

- 將原始圖像轉換為 RGB、平面 RGB,並將結果儲存在 RAM 中

- Mi-V 軟體 RISC-V 處理器啟動 CoreVectorBlox 引擎,該引擎從 RAM 擷取圖像、執行推斷,並將分類機率結果回存至 RAM

- Mi-V 使用這些結果建立一個帶有邊界框、分類結果和其他中繼資料的疊加訊框,並將此訊框儲存在 RAM 中

- 原始訊框與疊加訊框混合並寫入 HDMI 顯示器

這個展示可支援 Tiny Yolo V3 和 MobileNet V2 模型的加速功能,但是開發人員亦可以使用前述方式執行其他 SDK 支援的模型,只需將程式碼稍做更改,將模型名稱和中繼資料新增到包含兩個預設模型的現有清單中即可。

結論

諸如神經網路模型的 AI 演算法通常會為造成密集運算型工作負載,需要比一般用途處理器更強大的運算資源才可負荷。儘管 FPGA 具備足夠的能力,可滿足推斷模型執行所需的效能和低功耗要求,但傳統的 FPGA 開發方式可能比較複雜,往往導致開發人員改用次佳的解決方案。

如前文所述,若使用 Microchip Technology 的專用 IP 和軟體,即使不具備 FPGA 經驗的開發人員仍可實作出推斷式設計,進而更好地滿足效能、功耗和設計進度等需求。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。