使用整合式降壓 DC/DC 模組進行低 EMI 的高密度、高效率電源轉換

資料提供者:DigiKey 北美編輯群

2020-11-24

隨著電子裝置的整合度和普及性增加,設計人員承受提升效率,同時降低成本、尺寸、電磁干擾 (EMI) 的設計壓力。電源供應器能提升功率密度和效率,設計人員目前面臨的挑戰是開發異質處理架構 (可能會包含 ASIC、DSP、FPGA、微控制器的混合) 的多軌電源解決方案。

傳統上此類架構以降壓 DC/DC 轉換器供電,但隨著電源軌的數量增加,使用傳統具有控制 IC 和內建或外加功率 MOSFET 的離散式降壓 DC/DC 轉換器,加上外部電感和電容,不但複雜且耗時。不過,設計人員可以使用含多軌和可編程定序功能的自足式降壓 DC/DC 轉換器模組,達到更佳 EMI 控制,且具有更低熱生成和更小覆蓋區。

本文將回顧嵌入式設計所需的電源系統,並探討多種方式及設計人員的考量,接著介紹自足式降壓 DC/DC 模組的概念。然後採用 Monolithic Power Systems 的範例,簡要說明設計人員在進行設計和佈局時的考量,以便讓這些模組達到最大效能。

為何嵌入式系統需要許多電源軌

5G 基地台等嵌入式設計旨在支援來自智慧型手機和智慧連接裝置不斷增加的資料量需求,應用領域包含家庭和工業自動化、自駕車、健康照護、智慧穿戴式裝置。此類基地台通常使用 48 V 輸入供應器,藉由 DC/DC 轉換器降壓至 24 V 或 12 V,接著進一步降壓至介於 3.3 V 至低於 1 V 的許多子電源軌,以便在基頻處理階段中驅動 ASIC、FPGA、DSP,以及其他元件。電源軌常需要定序以啟動或關斷,替設計人員增加電源系統的複雜性。

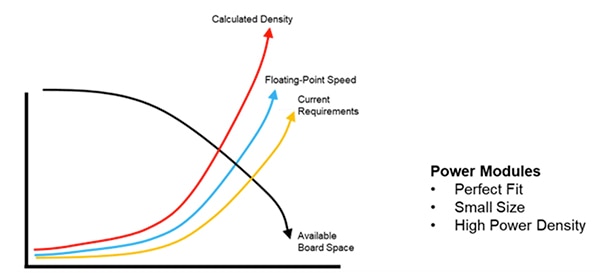

在 5G 基地台的例子中,傳統 CPU 本身已無法符合處理的需求。不過,使用加速器卡搭配 FPGA 用於系統具備優勢,可提供重新配置能力、彈性、短開發時間、高平行運算、低延遲。但 FPGA 電源供應器的可用空間正縮減,且電源軌的效能要求很複雜 (圖 1):

- 輸出偏移:電源軌的輸出電壓偏移必須小於 ±3%,且在設計中必須留有足夠餘裕。可藉由將控制迴路最佳化以提升頻寬,並確保其穩定性,解耦電容必須妥善施加及設計。

- 單調啟動:所有的電源軌必須以單調啟動,且必須避免輸出電壓回到其初始值。

- 輸出電壓漣波:穩態操作時,所有電源軌 (除了類比電源軌) 的輸出電壓漣波不得超過 10 mV。

- 計時:FPGA 在啟動和關斷時,必須符合特定計時需求。

圖 1:運算需求增加,導致加速器卡上處理器的尺寸增加,更使得電源供應器的可用空間縮減。(圖片來源:Monolithic Power Systems)

圖 1:運算需求增加,導致加速器卡上處理器的尺寸增加,更使得電源供應器的可用空間縮減。(圖片來源:Monolithic Power Systems)

資料處理頻寬需求提升,促使處理器需要更多電流和功率。加速器卡的運算密度和浮點速度需求也讓產業難以追隨。加速器卡槽通常使用 PCIe 標準,因此板尺寸為固定。運算需求增加,導致處理器的尺寸增加,進一步使得電源供應器的可用空間縮減。

電源系統設計替代品

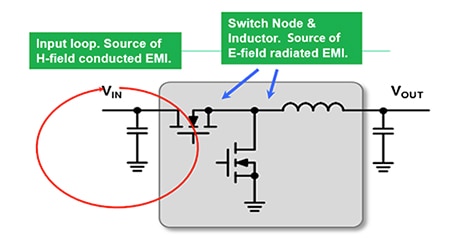

其中一個驅動嵌入式系統的方式是使用傳統離散式降壓 DC/DC 轉換器,搭配一個控制 IC 和內建或外加功率 MOSFET,以及外部電感和電容。如上所述,對設計人員來說,需要多軌電源解決方案時,這不僅複雜且耗時。除了考量到如何達到最大效率和最小解決方案尺寸,設計人員還必須注意濾波器元件的佈局和置放,以達到轉換器和電感電路在切換時的最低傳導和放射 EMI (圖 2)。

圖 2:設計人員面臨離散式降壓 DC/DC 轉換器的多重 EMI 來源。(圖片來源:Monolithic Power Systems)

圖 2:設計人員面臨離散式降壓 DC/DC 轉換器的多重 EMI 來源。(圖片來源:Monolithic Power Systems)

DC/DC 轉換器一般會在輸出功率 MOSFET 切換節點至接地以及輸入電容至接地的電流迴路路徑磁場產生傳導 EMI。也會從 MOSFET 切換節點至電感連接產生放射電場 EMI。由於持續切換自高輸入電壓位準至接地,以及電感內產生的電磁場,因此具有高 dV/dt。不正確的設計會導致耗時的 EMI 實驗室重新測試和多重設計疊代。

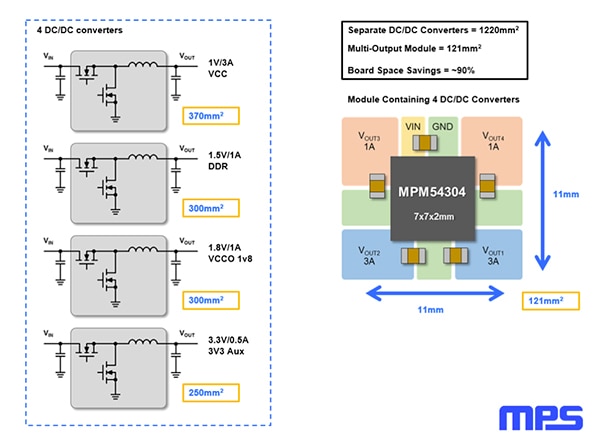

使用離散式降壓 DC/DC 轉換器驅動 ASIC 或 FPGA 的四軌解決方案會佔用 1220 mm2 (圖 3)。若使用電源管理 IC (PMIC) 架構解決方案,則能縮減至約 350 mm2。作為替代方案,設計人員可以使用自足式四輸出 DC/DC 轉換器模組,將解決方案尺寸縮減至僅 121 mm2,同時簡化設計流程並加快上市。半導體製程技術和封裝結構的進展能讓最新一代的 DC/DC 模組在小型外型中達到超高功率密度、高效率、優良的 EMI 效能。

圖 3:相較於離散式解決方案,使用整合式 DC/DC 模組解決方案可以節省高達 90% 的板空間。(圖片來源:Monolithic Power Systems)

圖 3:相較於離散式解決方案,使用整合式 DC/DC 模組解決方案可以節省高達 90% 的板空間。(圖片來源:Monolithic Power Systems)

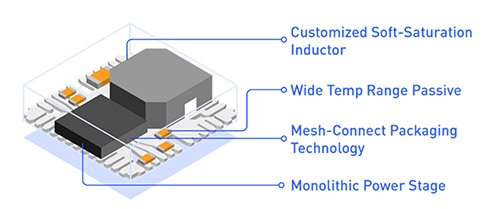

新的結構技術,例如封裝內覆晶和「網狀連接」引線框架技術,能讓 IC、電感、被動元件直接安裝入引線框架,而無須電線連接或額外的內部電路板 (圖 4)。相較於使用內部電路板基板或以電線連接的較舊結構,可縮短走線長度,並且直接連接至被動元件,進而維持低電感值且將 EMI 降至最低。

圖 4:新的架構樣式使用引線框架進行互連,具有多種優勢:能更佳控制 EMI、提升熱耗散、縮減覆蓋區。(圖片來源:Monolithic Power Systems)

圖 4:新的架構樣式使用引線框架進行互連,具有多種優勢:能更佳控制 EMI、提升熱耗散、縮減覆蓋區。(圖片來源:Monolithic Power Systems)

使用柵格陣列 (LGA) 封裝直接進行表面黏著至目標電路板,可提供相較於替代單列直插式 (SIL) 或 SIL 封裝 (SIP) 樣式更低的 EMI 曲線,這是因為後者具有引線,會放射 EMI。

四輸出可編程整合式 DC/DC 模組

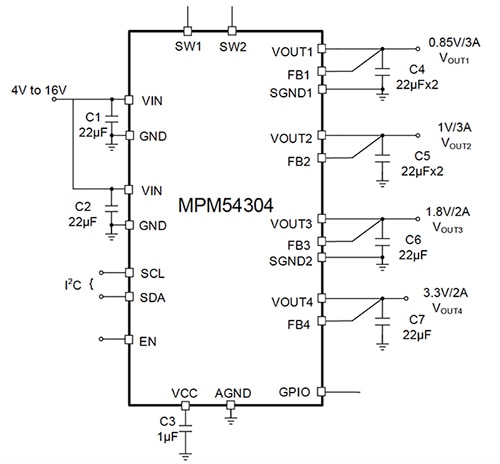

為達到嵌入式系統的多軌、高功率密度需求,設計人員可以使用 Monolithic Power Systems 的 MPM54304 (圖 5)。MPM54304 是一款完整的電源管理模組,整合有四個高效率的降壓型 DC/DC 轉換器、電感和一個彈性的邏輯介面。MPM54304 能在 4 V 至 16 V 的輸入電壓範圍內操作,可支援介於 0.55 V 至 7 V 的輸出電壓。四個輸出軌可以支援高達 3 A、3 A、2 A、2 A。兩個 3 A 和兩個 2 A 軌可以並聯,分別提供 6 A 和 4 A。設計人員需注意,並聯模式的最大輸出電流也受限於總功率耗散。這能提供彈性,產生數種輸出配置 (受到總功率耗散限制):

- 3 A、3 A、2 A、2 A

- 3 A、3 A、4 A

- 6 A、2 A、2 A

- 6 A、4 A

圖 5:MPM54304 是完整 4 V 至 16 V 電壓數入四輸出降壓電源管理模組。(圖片來源:Monolithic Power Systems)

圖 5:MPM54304 是完整 4 V 至 16 V 電壓數入四輸出降壓電源管理模組。(圖片來源:Monolithic Power Systems)

MPM54304 還提供內部定序,用於啟動和關斷。軌配置和定序可以透過多時可編程 (MTP) 電子保險絲或 I2C 匯流排進行預先編程。

此固定頻率恆定導通時間 (COT) 控制 DC/DC 轉換器提供快速暫態響應。其預設的 1.5 MHz 切換頻率可大幅縮小外部電容的尺寸。切換時脈在連續電流模式 (CCM) 操作下為鎖定及從降壓 1 到降壓 4 相移。輸出電壓可透過 I2C 匯流排進行調節,或以 MTP (多次可編程) 電子保險絲進行預設。

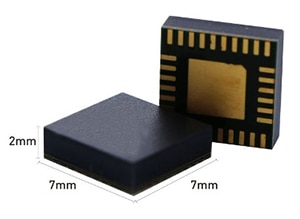

完整的保護功能包括過壓關斷 (UVLO)、過電流保護 (OCP) 與熱關斷。MPM54304 僅需最少的外部元件,並且採用節省空間的 LGA (7 mm x 7 mm x 2 mm) 封裝 (圖 6)。LGA 的薄型特點適合置放於板後方或散熱片下。

圖 6:MPM54304 的 LGA 封裝提供小型且薄型的解決方案,具有低 EMI (圖片來源:Monolithic Power Systems)

圖 6:MPM54304 的 LGA 封裝提供小型且薄型的解決方案,具有低 EMI (圖片來源:Monolithic Power Systems)

設計和佈局的考量

MPM54304 沿著邊緣具有簡單的引腳配置,可輕鬆進行佈局和電路板設計。只需要五個外部元件,讓整體解決方案小型且緊湊。LGA 封裝提供堅固的平面覆蓋模組底下的大部分區域,有助於封閉渦流迴路,進一步降低 EMI。

此降壓轉換器具有不連續輸入電流,並需要一個電容供應 AC 電流至轉換器,同時維持 DC 輸入電壓。設計人員需要使用低等效串聯電阻 (ESR) 電容以取得最佳效果。建議使用具有 X5R 或 X7R 介電材料的陶瓷電容,因其具有低 ESR 和低溫度係數。針對大多數應用,22 µF 電容已足夠。

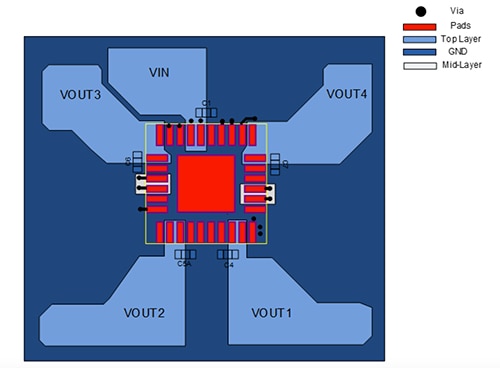

高效率的電路板佈局對於 MPM54304 的穩定操作很重要。建議使用四層電路板,以達到更加的熱效能 (圖 7)。為達到最佳效果,設計人員需要遵循以下準則:

- 將電源迴路保持越小越好

- 使用大型接地平面直接連接至 PGND若底層為接地平面,在 PGND 附近添加導通孔

- 確保 GND 和 VIN 的高電流路徑為短、直接、寬的走線

- 將陶瓷輸入電容盡可能靠近元件

- 將輸入電容和 IN 距離盡可能縮短及寬廣

- 將 VCC 電容儘可能接近 VCC 和 GND 引腳

- 連接 VIN、VOUT、GND 至大型銅區域,以提升熱效能和長期可靠性

- 分離輸入 GND 區域與其他頂層 GND 區,並且在內部層和底層透過多重導通孔連接

- 確保內部層或底層有整合式 GND 區域

- 使用多重導通孔連接電源平面至內部層

圖 7:使用 MPM54304 四輸出電源模組時,建議使用四層電路板佈局。(圖片來源:Monolithic Power Systems)

圖 7:使用 MPM54304 四輸出電源模組時,建議使用四層電路板佈局。(圖片來源:Monolithic Power Systems)

結論

處理架構不斷演進以因應具有高要求的資料應用。設計人員面臨的難題在於開發多軌電源解決方案,以便支援增加的處理功率和外型縮減或不變的電子裝置。降壓 DC/DC 轉換器在設計這些系統的電源解決方案時為關鍵元件,但可能複雜且難以實作。

如上所述,設計人員可以轉用具有多電源軌和可編程定序的自足式降壓 DC/DC 轉換器模組,簡化設計流程並加速上市。此外,新的結構技術也讓這些自足式模組具備多種效能優勢:更佳的 EMI 控制、提升的熱耗散、縮減的覆蓋區。

推薦閱讀

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。