使用高效的多核心處理器,打造更智慧的語音啟動式產品

資料提供者:DigiKey 北美編輯群

2020-02-14

隨著使用者更加熟悉和信賴 Amazon Alexa、Google Assistant、Apple Siri 及 Microsoft Cortana 等虛擬數位助理,幾乎每個應用領域對更高智慧產品的需求都在提升。這些助理在工業系統及醫療保健應用上,除了提供便利性外,在增強各種產品的安全性上扮演著重要的角色。但對開發人員來說,這些產品的底層設計需求,有時會對處理器互相衝突,因為既要能提升效能、最佳化成本和覆蓋區,又要能以高效率運行。

本文將介紹開發人員如何使用多核心處理器 (本例為 NXP 的 i.MX 8M Nano) 滿足眾多應用對新興智慧型產品的各種處理及介面要求,應用領域涉及智慧住家、工業自動化以及醫療系統等。特別是,本文會重點介紹開發人員如何使用此處理器,更輕鬆地實作具有進階音訊處理能力的新一代語音啟動式解決方案。

智慧型產品的發展方向

語音助理技術的快速崛起,令使用者從智慧型產品中尋求更多的功能。新興產品不僅需要回應語音指令,還需要嵌入更多智慧,使用來自感測器、攝影機及其他產品的各種輸入資料。只是以智慧照明開關開燈和關燈,或讓洗碗機根據語音指令運作,還遠遠不夠。隨著應用變得越來越複雜,其底層元件將需要支援更多元的感測器組合、使用人工智慧 (AI) 方法加強處理能力,並支援 3D 圖形顯示。

之所以需要更智慧的產品,不只是渴望提高便利性而已。在工業自動化和醫療保健等關鍵應用領域,元件必須要能主動提醒使用者注意危險或病況,這一點非常重要。工廠工人若頭戴可即時監測周遭狀況的安全帽,將能更迅速避開危險;高危險群病患若配戴可連續監測生命徵象的小型醫療監視器,則能獲得所需的介入措施,解除危機。

上述及其他智慧型產品提出的特定設計需求,雖與其目標應用一樣多元,但大部分都需要高效能處理、安全運作以及多媒體功能。對開發人員來說,要滿足這些功能需求和應用基本要求,解決方案不僅要能夠進行擴充,以支援更穩健的應用,還要能夠進行實體縮減,以符合使用者的期望,實現更小的尺寸、更少的成本和更低的功耗。NXP 的 i.MX 8M Nano 應用處理器系列以異質多核心架構為基礎,可滿足新興智慧型產品的各種設計需求。

高效能核心

NXP 的 .MX 8M Nano 是 i.MX 8M 處理器系列的最新成員,專為提供可擴充的多核心處理平台而設計。對於高端視訊應用,NXP 的 i.MX 8M 旗艦處理器 (如 MIMX8MQ5DVAJZAB),可提供高達 4K 顯示解析度,以及 4K 高動態範圍 (HDR) 視訊的硬體解碼能力。對於 1080p 視訊,NXP 的 i.MX 8M Mini 處理器 (如 MIMX8MM6CVTKZAA) 可支援 1080p 硬體解碼。i.MX 8M 和 8M Mini 系列整合了多達四個 Arm® Cortex®-A53 應用處理器和一個 Arm Cortex-M4F 微控制器核心。

相較之下,NXP 的 i.MX 8M Nano MIMX8MN6CVTIZAA 處理器則整合了四個 Arm Cortex-A53 核心和一個 Arm Cortex-M7 核心。而相對於 Arm Cortex-M 系列的其他核心 (包括 Cortex-M4F),Arm Cortex-M7 核心提供的效能最高。

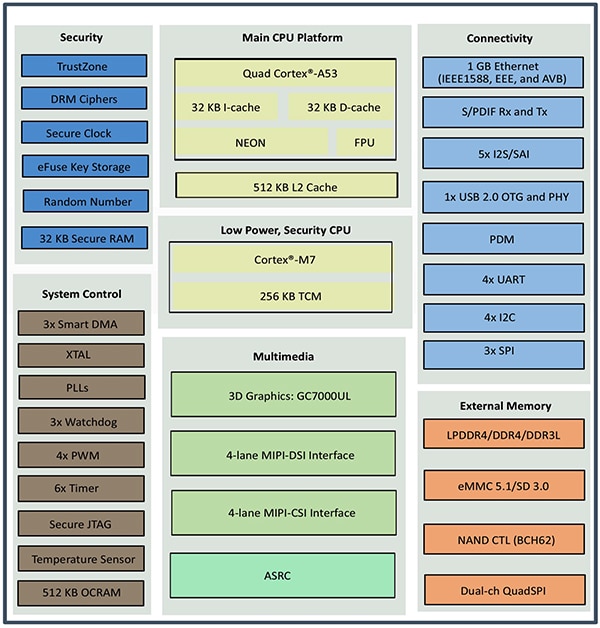

除了為處理器核心提供補充外,i.MX 8M Nano 處理器還支援各種外部記憶體元件,並提供消費性和工業應用通常所需的各種外部周邊裝置介面 (圖 1)。

圖 1:NXP 的 i.MX 8M Nano 處理器整合了多達四個 Arm Cortex-A53 應用處理器、一個 Arm Cortex-M7 微控制器、專用硬體子系統,以及消費性和工業應用通常使用的各種外部周邊裝置介面。(圖片來源:NXP)

圖 1:NXP 的 i.MX 8M Nano 處理器整合了多達四個 Arm Cortex-A53 應用處理器、一個 Arm Cortex-M7 微控制器、專用硬體子系統,以及消費性和工業應用通常使用的各種外部周邊裝置介面。(圖片來源:NXP)

i.MX 8M Nano 處理器系列提供了不同的型號,能讓開發人員輕鬆滿足成本和效能方面的特定需求。例如,高效能成員整合了廣泛的專用子系統,可用於安全、3D 圖形顯示及音訊處理等。另一些 i.MX 8M Nano 系列成員則提供了較少 Cortex-A53 核心的選項,以及圖形能力較低的「輕量」版。

不過,i.MX 8M Nano 處理器系列的所有成員都能提供新興智慧型產品所需的應用效能和即時能力。

每個 Arm Cortex-A53 應用處理器核心,都能讓應用軟體達到高執行效能,這些核心能以高達 1.5 GHz 的時脈頻率運作,並可從專用的 L1 32 KB 指令快取 (I-cache)、32 KB 數據快取 (D-cache) 和共用的 L2 512 KB 通用快取工作。結合內建的浮點單元 (FPU),這些核心支援 Arm 的 Neon 技術,可實現數位訊號處理所用的進階單指令多資料 (SIMD) 作業,以及資料密集應用的其他進階演算法。

對於嵌入式系統要求,Arm Cortex-M7 微控制器核心能以高達 750 MHz 的頻率執行,並為需要低延遲和確定性作業的即時程序,提供高效能的執行。為了進一步加快處理速度,該核心整合了 FPU 和 256 KB 緊密耦合記憶體 (TCM),以用於指令與資料快取。

不過,對於複雜的即時處理任務,能夠快速識別獨立的中斷來源與原始處理能力同樣重要。在 i.MX 8M Nano 處理器中,每個 Arm Cortex-A53 核心內建的全域中斷控制器 (GIC) 以及 Arm Cortex-M7 核心內建的嵌套向量中斷控制器 (NVIC),支援從將近 128 個不同的中斷要求來源,進行精細中斷處理,這些來源包括核心狀態、計時器、周邊裝置介面事件、直接記憶體存取 (DMA) 作業以及專用硬體程序等。

異質多核心處理

每個 i.MX 8M Nano 處理器核心都可單獨提供可靠的運算資源。若一同使用,此處理器的多個核心則可提供強大的運算平台,良好管理即時效能需求與應用軟體執行需求的衝突,從而避免讓智慧型產品的設計陷入混亂。例如,以此處理器為基礎的智慧型產品可使用 Cortex-M7 核心來即時處理音訊流,同時使用在一個或多個 Cortex-A53 核心上執行的演算法來分析所產生的資料,並以 3D 圖形為使用者顯示結果。

然而,若想可靠地執行這種協調的異質多核心處理,多核心系統需要精心協調處理作業以及在各個核心、專用硬體區塊與周邊裝置之間的資料交換。在 i.MX 8M Nano 處理器中,此協調功能內建於以硬體為基礎的旗號和訊息傳送機制中,通常為多重處理環境中的低階軟體服務所使用。

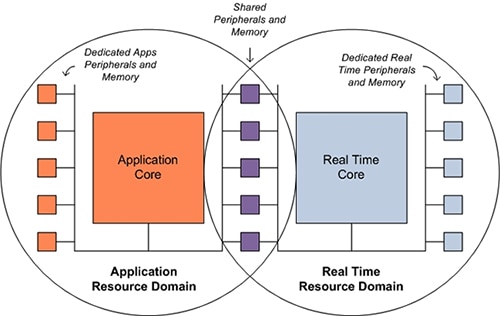

在嵌入式系統中,這種協調執行還擴展到記憶體和周邊裝置等硬體資源。針對此任務,此處理器整合了專用的資源域控制器 (RDC),可確保在適用情況下安全地共用資源或在需要時進行可靠的隔離。因此,應用軟體和即時程式碼可各自控制專屬於其域的資源,同時共用一組通用的資源 (圖 2)。

圖 2:NXP 的 i.MX 8M Nano 處理器以硬體為基礎的機制,可確保隔離專用於 Cortex-A53 應用域或 Cortex-M7 即時域的資源,同時在需要時實現安全的資源共用。(圖片來源:NXP)

圖 2:NXP 的 i.MX 8M Nano 處理器以硬體為基礎的機制,可確保隔離專用於 Cortex-A53 應用域或 Cortex-M7 即時域的資源,同時在需要時實現安全的資源共用。(圖片來源:NXP)

對智慧型產品的專業支援

只需使用 i.MX 8M Nano 處理器的多重核心和資源共用能力,開發人員便能為搭載語音助理和 3D 圖形的新興智慧型產品打造複雜的應用。i.MX 8M Nano 處理器為智慧型產品內建了專業的硬體支援,能讓這些應用獲得更高的效能並減少軟體覆蓋區。

在圖形方面,該處理器內建的圖形處理單元 (GPU) 可提供 2D 和 3D 圖形加速並支援標準的圖形資料庫,包括 Vulkan、開放運算語言 (OpenCL) 和開放圖形庫 (OpenGL)。內建的液晶顯示介面 (LCDIF) 控制器支援以 1080p60 (1080 逐行掃描,每秒 60 格) 格式顯示。

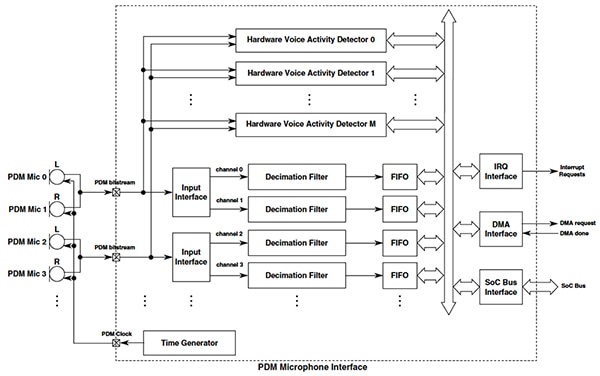

晶片上 GPU 可為核心分擔顯示處理任務,另一組硬體子系統則會分擔各種音訊處理任務,而這些任務通常會拖慢以傳統處理器為基礎的系統。對於麥克風輸入的處理,處理器的脈衝密度調變 (PDM) 麥克風介面 (MICFIL) 提供了多級管線,可從 PDM 麥克風所接收的 1 位元輸入,產生經過濾波的 16 位元脈衝編碼調變 (PCM) 資料 (圖 3)。

圖 3:NXP 的 i.MX 8M Nano 處理器具有 PDM 麥克風輸入介面子系統,該系統整合了獨立的硬體管線,可實現音訊訊號處理和語音活動偵測。(圖片來源:NXP)

圖 3:NXP 的 i.MX 8M Nano 處理器具有 PDM 麥克風輸入介面子系統,該系統整合了獨立的硬體管線,可實現音訊訊號處理和語音活動偵測。(圖片來源:NXP)

對於典型的語音型應用,設計人員只需要將 PDM 麥克風連接到該處理器支援的八個 PDM 通道之一。在 PDM 麥克風介面子系統中,輸入介面整合了一對麥克風的分時多工 PDM 資料,形成以左聲道和右聲道組成的線道 (lane)。

在每個聲道的下一個階段,專用的可編程抽取濾波器可提供不同的通帶,具體取決於所需輸出率和六個品質選擇 (QSEL) 設定之一 (包括高、中、低品質,以及三個額外的極低品質等級)。例如,在 48 kHz 輸出率下,極低品質模式會將濾波器通帶設定在 10.5 Hz 至 11.25 kHz,而高、中和低品質模式的通帶則為 21 Hz 至 22.5 kHz。最後,每個聲道的結果會在每個聲道的單獨先進先出 (FIFO) 緩衝器中提供,以產生中斷、透過 DMA 進行傳輸或存取匯流排。

以硬體為基礎的語音活動偵測

在這個語音訊號調整管線之外,PDM 麥克風介面還提供了一組硬體語音活動偵測器 (HWVAD),可監測所需的麥克風輸入聲道。(請注意:上圖指明每個 HWVAD 都與線道 (lane) 關連,但文件中稱為聲道 (channel),由暫存器的名稱 VADCHSEL 表明這點)。為了支援 HWVAD 作業,處理器提供了豐富的元件暫存器,可讓開發人員定義應用所需的特定 HWVAD 配置 (表 1)。

|

表 1:NXP 的 i.MX 8M Nano 處理器暫存器常用於配置處理器 PDM 麥克風介面 (MICFIL) 內建的硬體語音活動偵測器。(表格來源:DigiKey,基於 NXP 的資料)

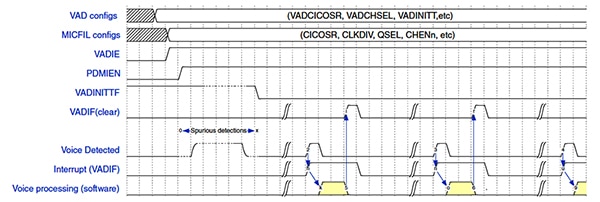

根據這些暫存器設定,HWVAD 會使用內建的語音偵測演算法來識別語音活動。偵測到活動時,HWVAD 會產生中斷指令來喚醒核心 (通常是 Cortex-M7) 進行進一步的處理 (圖 4)。

圖 4:根據開發人員所編程的配置設定,NXP 的 i.MX 8M Nano 處理器硬體語音活動偵測器會讓處理器核心進入睡眠或執行其他處理,直至偵測到語音並需要進行進一步的語音處理。(圖片來源:NXP)

圖 4:根據開發人員所編程的配置設定,NXP 的 i.MX 8M Nano 處理器硬體語音活動偵測器會讓處理器核心進入睡眠或執行其他處理,直至偵測到語音並需要進行進一步的語音處理。(圖片來源:NXP)

在語音助理應用中,核心會檢查音訊流是否含有相關的喚醒詞。若偵測到喚醒詞,核心通常會將音訊流提供給應用所支援的雲端型語音助理服務。

除了 PDM 麥克風介面子系統,i.MX 8M Nano 處理器還提供五個同步音訊介面 (SAI) 模組。這些模組支援多種標準音訊格式,包括 Inter-IC Sound (I2S)、音訊編解碼器 97 (AC97)、分時多工 (TDM) 音訊、直接流數位 (DSD) 以及編解碼器或數位訊號處理 (DSP) 資料。

為了滿足特定的應用要求,開發人員常要將音訊輸入樣本轉換成其他一些所需的取樣率和解析度。i.MX 8M Nano 處理器整合了專用的非同步取樣率轉換器 (ASRC) 子系統,而不是以處理器週期來完成這項常見任務。

ASRC 能夠同時處理多達 32 個聲道,可自動將源樣本轉換成所需的取樣率 (8 kHz 至 384 kHz) 及解析度 (IEEE 單精度浮點或固定點格式,每樣本 16、20、24 或 32 位元)。在此過程中,ASRC 會將所有輸入資料轉換成 64 位元 IEEE 浮點格式,以確保能準確地向上或向下轉換音訊樣本,實現所需的結果。

使用通用電源控制器管理電源

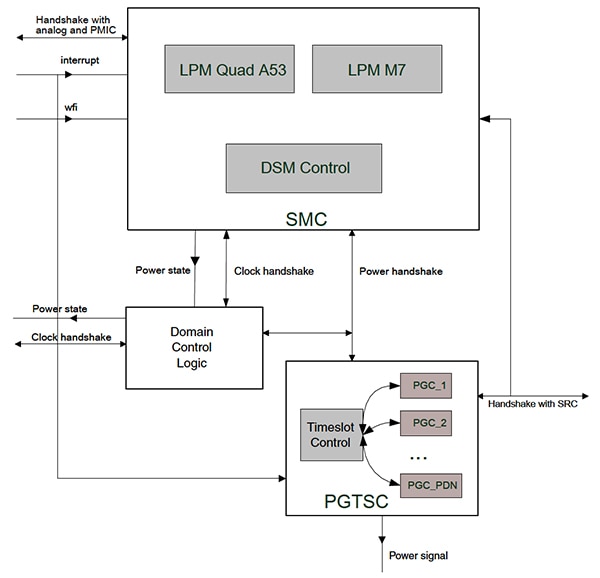

NXP 的 i.MX 8M Nano 處理器架構廣泛整合了處理器核心與硬體子系統,將多個獨立的電源域和電源模式內建於各個核心和子系統中。為了管理這些核心與專用區塊的電源,i.MX 8M Nano 處理器包含一個複雜的通用電源控制器 (GPC),來協調多個電源管理功能。在 GPC 中,系統模式控制器 (SMC) 會管理每個核心的低功率模式 (LPM) 及整體深度睡眠模式 (DSM),電源閘控時槽控制器 (PGTSC) 則會管理時脈閘控功能,透過停用閒置子系統的電源來降低系統功耗 (圖 5)。

圖 5:為了更好地最佳化系統級電源,NXP 的 i.MX 8M Nano 整合了全面的電源控制器,以管理處理器核心內建的電源閘控功能和低功率模式。(圖片來源:NXP)

圖 5:為了更好地最佳化系統級電源,NXP 的 i.MX 8M Nano 整合了全面的電源控制器,以管理處理器核心內建的電源閘控功能和低功率模式。(圖片來源:NXP)

在軟體或硬體的控制下,GPC 會使用 PGTSC 的 20 個不同時槽,對處理器內的多個時脈閘控電源域進行加電或斷電。此時,時槽控制器會依照順序完成這些時槽,並在啟動任何加電或斷電請求後再繼續下一個時槽。除了滿足特定的電源定序要求外,此方法還能讓開發人員在系統加電期間或從低功率或深度睡眠模式中喚醒系統時減少升電電流。

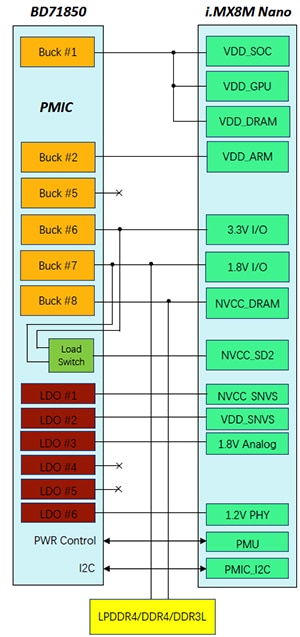

對於 i.MX 8M Nano 處理器,為其多個電源域供電相當簡單。ROHM Semiconductor 的 BD71850MWV 電源管理積體電路 (PMIC) 專為支援 NXP 的 i.MX 8M Nano 處理器而設計,可提供處理器及其他系統周邊裝置所需的所有電軌。事實上,BD71850MWV PMIC 整合有自己的電源定序器,不僅能讓處理器,還能讓外部記憶體、感測器或系統的其他元件更輕鬆地執行安全加電與斷電 (圖 6)。對於開發人員而言,在設計中加入 BD71850MWV PMIC 後,除了常見的解耦電容 (未顯示) 外,不再需要搭配其他的元件。

圖 6:NXP 的 iMX 8M Nano 處理器具有多個核心和硬體子系統,因此需要使用多個電軌,而 ROHM 的 BD71850MWV 電源管理積體電路 (PMIC) 提供了一個現成的解決方案。(圖片來源:NXP)

圖 6:NXP 的 iMX 8M Nano 處理器具有多個核心和硬體子系統,因此需要使用多個電軌,而 ROHM 的 BD71850MWV 電源管理積體電路 (PMIC) 提供了一個現成的解決方案。(圖片來源:NXP)

開發支援

雖然以 i.MX 8M Nano 為基礎的設計對硬體介面的要求相對較簡單,但 NXP 讓開發人員甚至不必進行這項相對簡單的設計任務,即可評估處理器或開發新智慧型產品的原型。8MNANOD4-EVK 評估套件為 i.MX 8M Nano 處理器提供完全實作的開發套件和公版設計,其整合 i.MX 8M Nano 處理器、BD71850MWV PMIC 和 Murata Electronics 的 LBEE5HY1MW Wi-Fi/藍牙收發器模組,為即時評估和原型開發提供了相應的平台。除了多個介面選項與相關的連接器,此評估套件還包含一整套外部記憶體元件,包括靜態動態 RAM (SDRAM)、NOR 快閃記憶體以及 NAND 快閃記憶體。利用此評估套件,開發人員可探索不同的工作模式和配置,包括從外部快閃記憶體開機或使用簽署的開機映像檔進行安全開機等。

若開發人員準備進行自己的客製化軟體開發,NXP 提供了可配合其自己的 MCUXpresso 整合開發環境及第三方 IDE 使用的驅動程序、電路板支援套件 (BSP) 以及中介軟體。若想打造利用機器學習方法的應用,開發人員可求助於 NXP 的 eIQ 機器學習開發環境和針對 i.MX 最佳化的推斷庫,例如 TensorFlow Lite 的 eIQ 環境 (用於以 Cortex-M7 為基礎的推斷),或 NXP 的 Arm 神經網路軟體開發套件 (NN SDK) 連接埠 (用於以 Cortex-A53 為基礎的推斷)。

結論

隨著語音助理產品迅速普及,人們對新一代智慧型產品的期望越來越高,不僅要求更好地支援音訊,還要求更高的效能、更強的圖形能力及更好的能效。但對開發人員來說,要為這些產品進行有效的系統設計,就需要高度的應用軟體執行效能以及低延遲的即時效能,而要在相關的尺寸、成本和功率限制下達到這些需求很有難度。NXP 提供可擴充的多核心處理器系列,可讓開發人員輕鬆滿足各種應用領域智慧型產品的設計需求,包括消費性、工業以及醫療領域等。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。