使用多核心處理器打造低功率但媒體功能強大智慧型產品

資料提供者:DigiKey 北美編輯群

2019-03-26

在智慧型產品中,將傳統的即時嵌入式設計要求,與更高要求的應用層級軟體相結合,這種做法日益普遍。除了更高的運算負載,這些產品還需要在觸控螢幕、高解析度 3D 繪圖和影像感測器等進階媒體服務上,支援使用者互動作業。

隨著需求不斷擴大,開發人員在降低功率、成本和系統尺寸方面遭遇更大壓力,因此不得不尋找比傳統多重子系統式設計更有效的替代方案。

本文將探討設計要求的演進,以及現今的處理器如何滿足這些要求。接著會介紹並說明如何使用 NXP Semiconductors 的新款處理器。這些處理器為開發人員提供更簡單的解決方案,可滿足設計上與日俱增的需求,如此即可符合即時運算和應用運算的要求。

以擴充處理器的方式維護程式碼投資

開發人員經常採用的作法是使用微處理器並搭載符合特定應用處理需求的額外內核,來擴充設計所需的運算能力。如此一來,開發人員不僅能增進效能,還能保持與現有程式碼資料庫的相容性,並且累積該裝置系列的使用經驗。

以 NXP 的 i.MX 6 應用處理器系列為例,設計人員不僅能維持與程式碼的相容性,更可使用 i.MX 6Solo 微處理器 (搭載單一 Arm® Cortex®-A9 應用處理器核心)、i.MX 6Dual (搭載雙核心),或是 i.MX 6Quad (搭載四核心) 來擴充效能。

對於曾考慮傳統嵌入式系統的設計而言,同樣也需要可擴充的應用處理能力,而且此需求正快速演變。針對這些設計,產品製造商期望在家電、工業控制器、醫療儀器等其他眾多產品中添加智慧能力。半導體廠商的因應之道就是推出整合應用處理器核心和嵌入式處理器核心的異質多核心處理 (HMP) 裝置。例如,NXP 的 i.MX 8M 系列就結合最多四個 Arm Cortex-A53 應用處理器核心,以及一個 Arm Cortex-M4 嵌入式處理器核心。

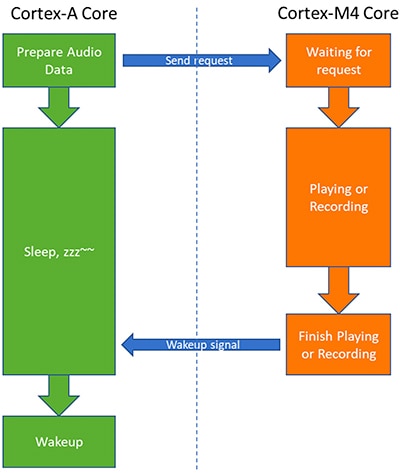

藉由此單一裝置,開發人員即可建構智慧型音訊產品。這些產品充分發揮應用處理器的優勢,透過增強、濾波或其他方式來處理音訊數據。接著,音訊系統會依靠嵌入式處理器核心來執行播放時所需的即時功能 (圖 1)。在嵌入式處理器進行即時作業時,應用處理器可切換至低功率模式以降低整體功耗。完成即時操作後,嵌入式處理器只需向應用處理器送出喚醒訊號即可。

圖 1:異質多核心處理器能在有限的功率預算下,提供高效能運算和即時處理能力,因此對於智慧型產品設計特別有效。(圖片來源:NXP Semiconductors)

除了異質核心,NXP 的 i.MX 8M 系列還整合了豐富的多媒體資源組,其中包括 4K 視訊處理單元 (VPU) 及高效能 3D 圖形處理單元 (GPU)。因此,此系列可為種類日益繁複的視訊和 3D 圖形智慧型產品,提供有效的解決方案。

不過,開發人員在建置高效能系統時,仍在電池和線路供電式系統上面臨日益增長的更低功耗需求。為解決這個問題,NXP 的 i.MX 8M Mini 處理器系列採用先進的半導體製程技術製造,順利解決了高效能混合式負載處理,以及降低功耗這兩項彼此衝突的要求。

高效能、低功率運算

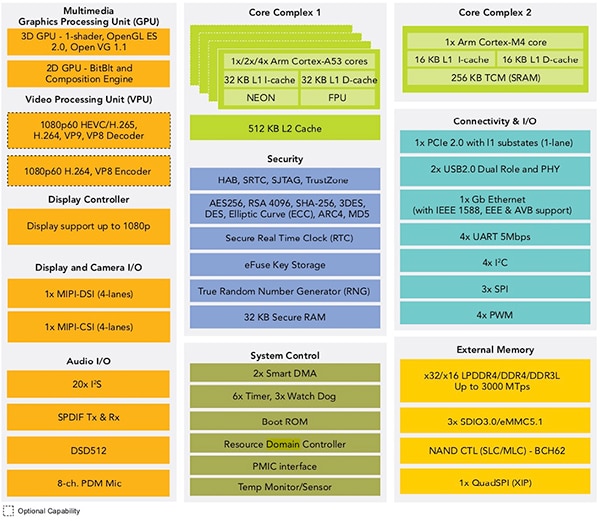

NXP 的 i.MX 8M Mini 處理器是 NXP HMP 系列中第一款採用 14 nm FinFET 製程技術製造的產品,並針對新興的工業與物聯網 (IoT) 系統進行設計,融合了高效能、高安全性和低功耗等要求。與 NXP 的 i.MX 8M 系列一樣,NXP 的 i.MX 8M Mini 內建一個 Arm Cortex-M4 (用於嵌入式處理) 及最多四個 Arm Cortex-A53 核心 (用於應用處理),還有一個全方位安全子系統,以及多個連線與 I/O 選項 (圖 2)。

圖 2:NXP 的 i.MX 8M Mini 處理器結合最多四個 Arm Cortex-A53 應用處理器核心,以及一個 Arm Cortex-M4 嵌入式核心,具備新興智慧型產品所需的全套安全、多媒體和系統功能,以及 I/O 介面。(圖片來源:NXP Semiconductors)

為了在嵌入式設計中充分發揮作用,i.MX 8M Mini 與 NXP 之前的 i.MX 8M 相比,在一些 I/O 通道數量上有所減少,並降低了多媒體子系統的高解析度能力。例如,i.MX 8M Mini 元件包括商用 (MIMX8MM6DVTLZAA) 和工業用 (MIMX8MM6CVTKZAAA) 款式,可提供單著色器 GPU 和 1080p 60 Hz 的 VPU,而 NXP 的 i.MX 8M 則提供四著色器 GPU 和 4K VPU。i.MX 8M Mini 系列的其他產品,包括商用 (MIMX8MM5DVTLZAA) 和工業用 (MIMX8MM5CVTKZAA) 款式則完全捨棄 VPU。與 NXP 之前的 i.MX 8M 一樣,i.MX 8M Mini 能讓開發人員利用處理器對多種記憶體類型提供支援,包括第三代雙倍數據傳輸率低電壓 (DDR3L)、DDR4 及低功率 DDR4 (LPDDR4),藉此進一步在效能與成本之間取得平衡。

降低功耗

若要進一步優化效能與功耗,開發人員可利用 NXP 的 i.MX 8M Mini 功能,以自動或編程方式,切換至較低功率的操作模式。在特定情況下,應用核心可以自動切換至閒置模式,並且關閉 GPU、VPU 和應用核心,同時對大部分內部邏輯進行時脈閘控,但維持對 L2 資料快取的供電。在此模式下,Arm Cortex-M4 核心仍可繼續運行,以執行感測器數據採集等更多的傳統嵌入式處理工作。

暫停模式是最省電的模式,可將管理記憶體介面的雙倍數據傳輸率控制器 (DDRC) 停用,藉此進一步降低閒置狀態下的功率。最後,安全的非揮發性儲存 (SNVS) 模式僅會維持對 SNVS 邏輯和即時時脈的供電。

i.MX 8M 的 14 nm FinFET 製程技術擁有降低功率的特性,在暫停和 SNVS 模式中更為明顯。在採用 FinFET 技術的 i.MX 8M Mini 中,暫停模式的功耗約為 7.81 mW。在之前的 i.MX 8M 中,功能類似的模式 (稱為深度睡眠模式),其功耗為 197 mW。SNVS 模式也有類似的功率降低特性,在此模式下,i.MX 8M Mini 的功耗約為 0.11 mW,而之前的 i.MX 8M 則約為 17 mW。

由於 i.MX 8M Mini 這類複雜元件具有各種功能區塊及精密微調的操作模式,工程師在實作上面臨許多嚴格限制。如同此類別的其他元件,i.MX 8M Mini 依靠多個電源域來達到最佳化的電源管理和效率。若要啟動或停止這些元件,需要嚴格遵循指定的電源啟動和關閉順序。

啟動 i.MX 8M Mini 電源時,第一步通常是向 SNVS 組的 GPIO 前置驅動器提供 1.8 V 的電源。在 2 ms (最多 2.4 ms) 內,必須再向 SNVS 核心邏輯提供 0.8 V (典型值) 的電源。此程序將持續在其他 12 個步驟中,在 0.015 ms 至 20 ms 的間隔時間內,依序向 i.MX 8M Min 引腳提供指定的訊號或電源。

關閉元件電源時,則需按照相反順序進行,但在每個順序階段之間統一延遲 10 ms。無論是啟動還是關閉電源,若違反這些準則,可能會導致無法啟動、在啟動期間造成過大電流,甚至在最嚴重的情況下造成元件永久損壞。

處理器的 PC 板實體設計有自身嚴格的要求。若要對處理器的 486 焊球 14 x 14 mm 封裝進行佈局,NXP 建議使用最少八層的 PC 板堆疊,以確保電軌有足夠的層數,符合電流電阻 (IR) 下降準則。同時,佈局工程師必須確保高速線路僅有最小的串音,包括以 1.5 GHz 速度和 3,000 MT/s 運行的受支援記憶體元件的線路。

快速開發

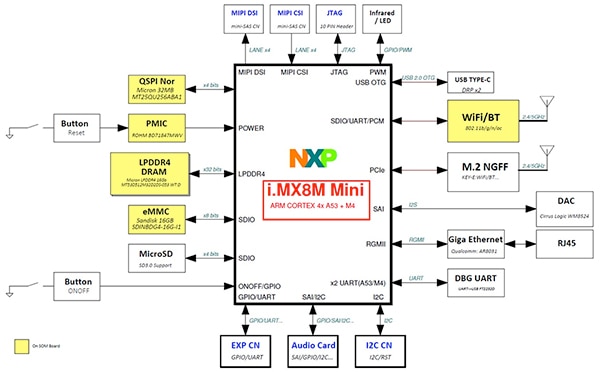

為協助工程師快速著手開發應用,或加速自訂硬體設計的開發,NXP 提供 NXP i.MX 8M Mini EVK (評估套件) 和相關的公版設計 (圖 3)。評估套件內含基板和系統模組 (SOM) 板,是一套完整的系統,其中包括外接式 LPDDR4 記憶體和快閃記憶體,以及 USB 和其他介面。

圖 3:NXP 的 i.MX 8M Mini EVK 板組合是完整的系統平台,可立即評估 i.MX 8M Mini 處理器,並可快速開發異質多核心處理器應用。(圖片來源:NXP Semiconductors)

除了 Gigabit 乙太網路,此套件還包含 Wi-Fi 及藍牙連線選項。提供的附加板包括:MINISASTOCSI 攝影機模組及 MX8-DSI-OLED1 有機發光二極體 (OLED) 觸控螢幕,能滿足視訊和顯示應用的設計需求。

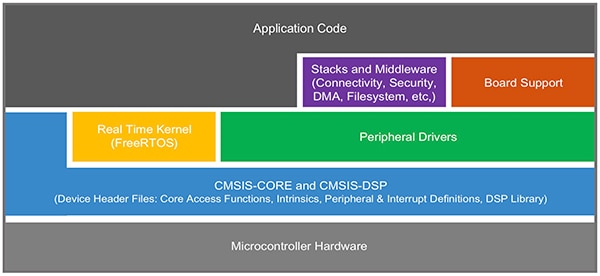

藉由嵌入式 Linux® 和嵌入式 Android® 作業環境的預建映像,開發人員能即刻使用此套件評估 i.MX 8M Mini 處理器,並執行範例應用。若想開發專屬的軟體應用,NXP 提供免費的 MCUXpresso 軟體開發套件 (SDK),其中含有一整套軟體組件,可用來建構典型的高效能嵌入式應用 (圖 4)。

圖 4:MCUXpresso 軟體開發套件 (SDK) 架構含有一整套軟體層,其中包括驅動程式、板支援套件,以及開發大多數嵌入式應用所需的選配零組件。(圖片來源:NXP Semiconductors)

利用 NXP 的線上 MCUXpresso SDK 儀表板,開發人員可針對 GCC Arm Embedded 工具鏈或 Arm 用的 IAR Embedded Workbench 設定 SDK 組態。另外,此儀表板還可讓開發人員添加選配的中介軟體元件,包括 Arm Cortex 微控制器軟體介面標準 (CMSIS) DSP 函式庫及 Amazon FreeRTOS。經設定的 SDK 將完整隨附 Arm 標準函式庫、周邊裝置驅動程式、FreeRTOS 的周邊裝置驅動程式封套,以及大量的軟體範例。在 SDK 隨附的軟體範例中,有一組應用程式展示了一個重要的訊息交換設計模式,這是異質運算的基礎架構。

在任何多核心運算環境中,各個處理器需要有效的機制來傳送請求及分享資料。對於 i.MX 8M Mini EVK 應用,NXP 會使用本身的 RPMsg-Lite,這是一種輕量版的遠端處理器訊息傳遞 (RPMsg) 協定。RPMsg 協定專為開放式非對稱多工處理 (OpenAMP) 架構專案而建立,可在異質多核心系統中,提供多核心間的標準通訊介面。NXP 的 RPMsg-Lite 解決了小型嵌入式系統的資源限制問題,可提供更小的覆蓋區,並去除與這些系統不一致的功能。

SDK 隨附一個 rpmsg_lite_pingpong_rtos 範例應用程式,其使用 RPMsg-Lite 在不同處理器間執行簡單的「乒乓」式互動,藉此展示單純的交換 (清單 1)。針對其他「遠端」處理器建立 RPMsg 佇列 (my_queue) 和端點 (my_ept) 後,「主機」應用處理器會向遠端核心發送訊號。收到遠端核心的握手回覆後,主機會開啟一個迴圈,使用封鎖等待來等候來自遠端的「乒」訊息,然後再送出自己的「乓」回應。

複製 void app_task(void *param) { ...my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS); while (!rpmsg_lite_is_link_up(my_rpmsg)) ; PRINTF("Link is up!\r\n"); my_queue = rpmsg_queue_create(my_rpmsg); my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue); ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL); rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE); PRINTF("Nameservice announce sent.\r\n"); /* Wait Hello handshake message from Remote Core.*/ rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK); while (msg.DATA <= 100) { PRINTF("Waiting for ping...\r\n"); rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL, RL_BLOCK); msg.DATA++; PRINTF("Sending pong...\r\n"); rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK); } PRINTF("Ping pong done, deinitializing...\r\n"); rpmsg_lite_destroy_ept(my_rpmsg, my_ept); my_ept = NULL; rpmsg_queue_destroy(my_rpmsg, my_queue); my_queue = NULL; rpmsg_ns_unbind(my_rpmsg, ns_handle); rpmsg_lite_deinit(my_rpmsg); msg.DATA = 0; ...}

清單 1:此程式碼片段來自於 MCUXpresso 軟體開發套件的範例程式碼,展示了異質多核心處理器中不同處理器間互動的基本設計模式。(程式碼來源:NXP Semiconductors)

開發人員能輕鬆地以此簡單交換為基礎,建立完整的操作,以在多個處理器之間分配工作執行。另一個範例應用程式 sai_low_power_audio 則使用 RPMsg-Lite 作為低階資料鏈路層,實現較高階的簡化型即時訊息傳遞 (SRTM) 應用協定。在此應用程式中,Arm Cortex-A53 處理器使用此 SRTM 協定向 Arm Cortex-M4 處理器請求播放位於共享記憶體中的音訊檔案。取得共享緩衝區的控制權之後,M4 會執行幾項操作,最後再執行一次智慧型直接記憶體存取 (SDMA) 交易,將數據傳送至適當的程式碼,並最終傳送至序列音訊介面 (SAI) 進行音訊輸出。在操作期間,A53 核心可進入低功率模式。雖然其設計比乒乓應用程式更為複雜,但 sai_low_power_audio 範例應用程式向開發人員展示了如何使用異質多核心處理器,不僅可在智慧型產品中發揮最大效能,更可將功耗降至最低。

結論

智慧型產品正逐步將傳統的即時嵌入式處理系統與大量的應用處理能力相結合。然而,開發人員不但要滿足這些處理需求,還要滿足電池和線路供電式系統對低功率產品的持續期望。

NXP 的 i.MX 8M Mini 應用處理器採用先進的半導體製程製造,可提供兼具低功耗與高效能特性的異質多核心處理能力。利用 NXP 的 i.MX 8M Mini 元件,就可更有效回應嵌入式系統設計對於高效能運算的需求,進一步滿足日益精密的智慧型產品需求。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。