瞭解抖動對高速鏈路的影響並將其降至最低

資料提供者:DigiKey 北美編輯群

2023-12-21

時脈振盪器能對系統元件進行配速,藉此提供現代電路的時序脈動。隨著系統速度提高到數百 MHz 以上,這些時脈必須更快並提供非常低的抖動 (通常低於100 fs) 以維持系統效能。儘管溫度和電壓會發生變化,但仍要隨時間維持低抖動規格。

有些抖動是由訊號路徑的雜訊和失真引起,可透過時脈重整和重定時技術達到一定程度的減少。然而,時脈來源也會產生抖動,而這個來源通常是振盪器。多種物理現象皆會造成此問題,包括熱雜訊、工藝瑕疵、電源雜訊、進入時脈振盪器的其他外部雜訊、材料應力和許多其他微妙因素。無論來源如何,設計人員都應盡一切可能將固有的時脈抖動降至最低,因為缺陷是不可逆的。

本文將從不同角度探討抖動問題。接著會介紹 Abracon LLC 的多種時脈振盪器,並展示如何將時脈振盪器的效能與應用匹配,藉此將抖動降至最低。

抖動的基礎知識

時脈抖動是指時脈邊緣與其在時間中理想位置之間的偏差。這個抖動會影響時脈訊號配速之數據訊號傳輸的定時精度和準確性,進而導致接收器解碼/解調電路或其他系統 IC 的訊噪比 (SNR) 下降。這會引起位元錯誤率 (BER) 提高、重新傳送增加,並且降低有效的數據傳輸量。

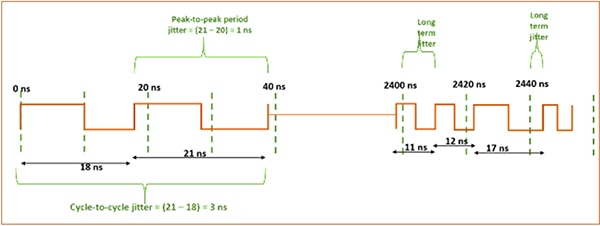

有鑑於此重要性,針對會透過電纜、連接器或電路板,將訊號從發送來源傳送到接收器的系統,都會廣泛分析其中的時脈抖動。根據應用的不同,可以透過多種方式分類,包括逐週期、週期與長期的抖動 (圖 1)。

圖 1:「抖動」一詞涵蓋許多時序變化,包括逐週期抖動、週期抖動和長期抖動。(圖片來源: VLSI Universe)

圖 1:「抖動」一詞涵蓋許多時序變化,包括逐週期抖動、週期抖動和長期抖動。(圖片來源: VLSI Universe)

- 逐週期抖動代表兩個連續週期內的時脈週期變化,且與頻率隨時間的變化無關。

- 週期抖動是指任何時脈週期相對於其平均週期的偏差。也就是理想與實際的時脈週期之間的差異,可以指定為均方根 (RMS) 週期抖動或峰對峰週期抖動。

- 長期抖動是指時脈邊緣與其在較長時間內的理想位置間的偏移。這有點類似於漂移。

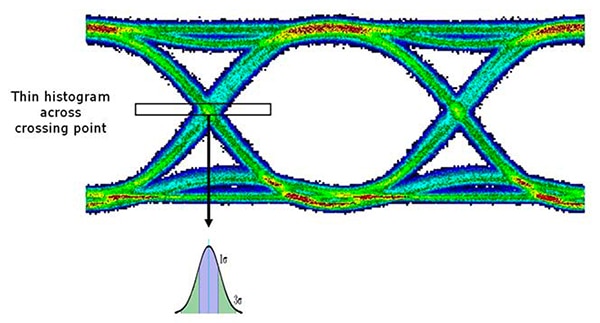

抖動會破壞其他子功能、元件或系統所用的時序,藉此達到低 BER 數據恢復,或對同步系統中的記憶體元件或處理器等元件進行配速。從圖 2 的眼圖中可以看出,位元時序中的交叉點有擴大的情況。

圖 2:在眼圖中,抖動可由數據流中關鍵時序交叉點的擴大看出。(圖片來源: Kevin K. Gifford/Univ.of Colorado)

圖 2:在眼圖中,抖動可由數據流中關鍵時序交叉點的擴大看出。(圖片來源: Kevin K. Gifford/Univ.of Colorado)

針對序列數據鏈路,接收端的電路必須試著重新建立其專屬時脈,以達到最佳的數據流解碼。為此,必須同步並鎖定來源時脈,而這通常會使用鎖相迴路 (PLL)。抖動會影響系統精確執行此操作的能力,進而有損其以低 BER 恢復數據的能力。

請注意,抖動可以在時域和頻域中測量;兩者對同一現象有一樣有效的觀點。相位雜訊是以頻域角度來看振盪器訊號周圍的雜訊頻譜,而抖動則是以時域角度來看振盪器週期的時序準確度。

抖動的測量有多種呈現方式。通常會使用時間單位來表示,例如「10 皮秒 (ps) 的抖動」。均方根 (RMS) 相位抖動是從相位雜訊 (頻域) 測量值所衍生的時域參數。抖動有時也稱為相位抖動,這可能會造成混淆,但仍屬於時域抖動參數。

隨著鏈路的工作頻率及其時脈從幾十 MHz 加速到數百 MHz 甚至更高,時脈源上可允許的抖動會降低到 100 fs 左右或更低。這些頻率適用於光學模組、雲端運算、連網以及高速乙太網路,這些所有功能和應用都需要 100 至 212/215 MHz 的載波頻率,以及高達 400 Gbps 的數據傳輸率。

管理晶體

要打造穩定、一致、準確頻率的時脈訊號,最常見的方法就是使用石英晶體振盪器。相關的振盪器電路可支援晶體。這類電路系列有相當多,各有不同的權衡。晶體自 1930 年代以來,就一直用於中頻 (300 kHz 至 3 MHz) 和高頻 (3 至 30 MHz) RF 頻段的無線電通訊。

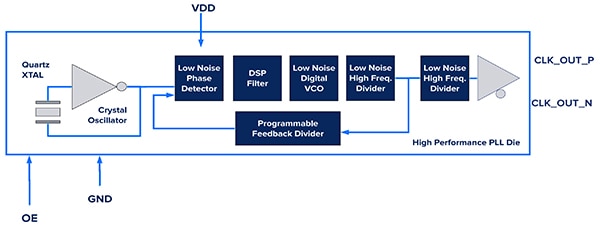

要產生低抖動時脈,有個廣泛使用的方法,就是採用眾多種 PLL 架構之一。例如,Abracon 的 AX5 和 AX7 ClearClock™ 系列裝置分別採用 5 × 3.2 mm 和 5 × 7 mm 封裝,並使用精細的 PLL 技術,可達到優異的低抖動效能 (圖 3)。

圖 3:Abracon AX5 和 AX7 時脈振盪器採用眾多 PLL 架構設計之一,但進行細微的增強,以將抖動降至最低。(圖片來源:Abracon)

圖 3:Abracon AX5 和 AX7 時脈振盪器採用眾多 PLL 架構設計之一,但進行細微的增強,以將抖動降至最低。(圖片來源:Abracon)

除了工作頻率和振盪器設計外,抖動的效能還會受到振盪器核心的石英晶體實體尺寸影響。隨著晶體尺寸減小,要提供優異的 RMS 抖動效能就更具挑戰。

若時脈方案要介於 100 至 200 MHz 頻段,且外型尺寸要比 PLL 架構的 AX5 和 AX7 裝置更小,就需要一種新的振盪器架構。這些更小尺寸的要求通常出現在最新一代的光學收發器和模塊身上。有四種既定方法可設計 100 至 200 MHz 範圍的時脈振盪器:

- 使用帶有反轉凸型石英胚的石英振盪器當作諧振器元件

- 使用帶有第三泛音石英胚的石英振盪器當作諧振器元件

- 使用基於低於 50 MHz 的第三泛音/基波模式石英胚的振盪器迴路,或是低於 50 MHz 的溫度補償式晶體振盪器,並搭配整數或分數模式 PLL IC

- 使用低於 50 MHz 微機電系統 (MEMS) 諧振器架構的振盪器迴路,並搭配有整數或分數模式 PLL IC

選項 1 無法提供最佳的 RMS 抖動效能,也不是最符合成本效益的解決方案。選項 3 會複雜化且具有效能缺陷;選項 4 的 MEMS 諧振器作法並不符合 200 fs 最大 RMS 抖動的首要效能條件。相比之下,選項 2 使用最佳化設計的第三泛音石英胚,且將電極的幾何形狀和切割角度的最佳化都納入考量。這個組合在成本、效能和尺寸方面都最佳。

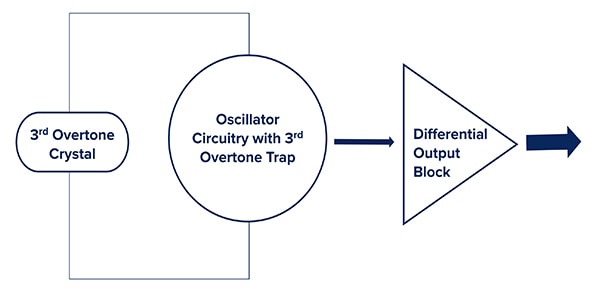

Abracon 就以此作法開發了「第三泛音」ClearClock 解決方案 (圖 4)。這些裝置採用更安靜的架構,可在小至 2.5 × 2.0 x 1.0 mm 的微型封裝中達到優異的超低 RMS 抖動效能和極致的能效。

圖 4:Abracon 的「第三泛音」ClearClock 解決方案使用更安靜的架構來提高整體效能和能效。(圖片來源:Abracon)

圖 4:Abracon 的「第三泛音」ClearClock 解決方案使用更安靜的架構來提高整體效能和能效。(圖片來源:Abracon)

在此方案中,精心設計的第三泛音晶胚,加上對所需載波訊號進行適當的濾波和「捕捉」,就可確保在所需載波頻率下達到出色的 RMS 抖動效能。

此架構並未使用典型的 PLL 作法,因此沒有升頻轉換。因此,不需要標準的 PLL 分數或整數乘法,而且最終的輸出頻率會與第三泛音石英晶體的諧振頻率有一對一的相關性。由於沒有分數或整數乘法,因此可簡化設計,且能以盡可能最小的尺寸達到最小抖動。

現實中的規格和效能

時脈振盪器不僅僅是晶體與類比電路而已。更含有緩衝,可確保振盪器的輸出負載及其短期和長期變化,不會影響裝置的效能。更支援多種差動數位邏輯輸出位準,可達到電路相容性。有了這個相容性,就無需外部邏輯位準轉換 IC。否則這個 IC 會增加成本、佔位空間和抖動。

由於時脈振盪器用於電軌電壓各有不同的眾多應用,因此必須提供多種電源電壓,例如 +1.8 V、+2.5 V 或 +3.3 V,以及介於 2.25 至 3.63 V 的常見自訂值。此外還要提供不同的輸出格式選項,例如低壓正/偽發射極耦合邏輯 (LVPECL) 和低壓差動訊號 (LVDS) 以及其他格式。

以 AK2A 和 AK3A 這兩個晶體時脈振盪器系列為例,就可展示出對材料、設計、架構和測試的深入瞭解和整合如何達成目標。這兩個系列相似,最明顯的差異在於尺寸和最大頻率。

AK2A 系列:此系列晶體振盪器的標稱頻率範圍介於 100 至 200 MHz,提供的工作電壓為 2.5 V、3.3 V 以及 2.25 至 3.63 V,並具有 LVPECL、LVDS 和 HCSL 差動輸出邏輯。

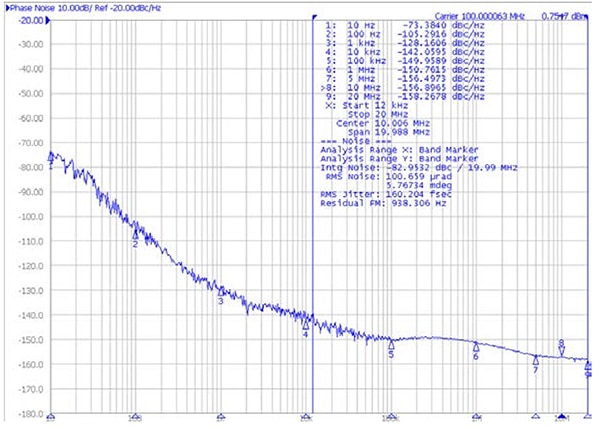

所有系列成員都具有相似的效能,包括低 RMS 抖動。例如,AK2ADDF1-100.000T 就是一款 100.00 MHz、3.3 V 裝置,具有 LVDS 輸出和 160.2 fs 的 RMS 抖動 (圖 5)。其頻率穩定性在整個溫度範圍內比 ±15 ppm 更優秀,並採用 2.5×2.0×1.0 mm 的六引腳表面黏著 (SMD) 封裝。

圖 5:AK2ADDF1-100.000T 是一款具有LVDS 輸出的 3.3 V、100 MHz 裝置,抖動為 160 fs。(圖片來源:Abracon)

圖 5:AK2ADDF1-100.000T 是一款具有LVDS 輸出的 3.3 V、100 MHz 裝置,抖動為 160 fs。(圖片來源:Abracon)

但是,隨著時脈頻率增加,抖動必須降低,才能保持系統級效能。AK2ADDF1-156.2500T 是 156.25 MHz LVDS 振盪器,典型 RMS 抖動會降至 83 fs。

AK3A 系列:AK3A 系列的裝置尺寸略大於 AK2A 系列,尺寸為 3.2 × 2.5 × 1.0 mm (圖 6)。提供的各版本皆指定為 212.5 MHz,略高於 AK2A 系列的 200 MHz 限制。

圖 6:AK3A (右) 晶體振盪器比 AK2A 系列 (左) 略長且更寬;各版本的頻率最高可達 212.5 MHz,而 AK2A 的頻率則為 200 MHz。(圖片來源:Abracon)

圖 6:AK3A (右) 晶體振盪器比 AK2A 系列 (左) 略長且更寬;各版本的頻率最高可達 212.5 MHz,而 AK2A 的頻率則為 200 MHz。(圖片來源:Abracon)

AK3A 裝置的整體規格與對應的 AK2A 系列產品相似。例如,AK3ADDF1-156.2500T3 是一款 156.25 MHz LVDS 振盪器,其典型 RMS 抖動為 81 fs,略優於對應的 AK2A 系列產品。

兩個系列的抖動會因工作頻率、工作電壓、封裝尺寸和輸出選擇而有所不同。

其他現實考量

要讓時脈振盪器一出廠就發揮規格效能是不切實際的。就像所有元件一樣 (尤其是類比和被動元件),這些振盪器也會因為組成材料的老化和內部應力,隨著時間的推移而漂移。

對於高效能時脈振盪器來說,這個現實情況更具挑戰性,因為沒有方便或簡單的方法可以透過新增軟體或智慧電路的方式,針對這個漂移進行修正或補償。但是,仍有一些方法可以減輕漂移的影響。包括最終使用者透過長時間的預燒來加速振盪器老化,或在烘箱控制的外殼中使用溫度穩定型振盪器。前者不僅耗時且對供應鏈構成挑戰,而後者則體積龐大、成本高昂且耗電。

由於瞭解老化是關鍵的參數,Abracon 的 ClearClock 系列可在 10 至 20 年的整個最終產品壽命範圍內提供嚴格、全面的頻率準確度。Abracon 可在此期間內確保頻率穩定性的合規性比 ±50 ppm 更優秀。透過第三泛音晶體的精心挑選和製造,並對其進行調整,就可在 -20°C 至 +70°C 範圍內達到 ±15 ppm 的穩定性,並在 -40°C 至 +85°C 範圍內達到 ±25 ppm。

與往常一樣,工程都是需要權衡的。與前代系列相比 (分別為第一代 AK2 和 AX3),Abracon 的 AK2A 和 AK3A 系列運用新一代 (第二代) 振盪器 ASIC,提供改進的抖動雜訊效能,進而確保超低的 RMS 抖動效能。

達到這個改進的代價是功耗略有增加。最大電流消耗從第一代的 50 mA 增加到第二代的 60 mA,儘管低壓裝置的工作消耗量只有一半。因此,第二代 ClearClock 振盪器提供超低 RMS 抖動,同時仍維持低功耗。

結論

時序振盪器是數據鏈路或時脈功能的核心,其準確度、抖動和穩定性是達到所需系統級效能 (包括高 SNR 和低 BER ) 的關鍵參數。利用創新的材料選擇和架構,就可達到更高的時脈頻率,更可符合產業及各種標準所要求的嚴格效能規格。Abracon 的 AK2A 和 AK3A 系列能以各邊僅有幾 mm 的 SMD 封裝,在 100 至 200 MHz 範圍內達到低於 100 fs 的抖動。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。