使用轉換迴路模組快速打造低抖動、高頻率時脈

資料提供者:DigiKey 北美編輯群

2021-08-04

儀器與測量系統的設計人員需要低抖動、零寄生的訊號來提供必要的訊噪比 (SNR) 誤差向量幅度,以符合逐漸提高的客戶要求。於此同時,他們也面臨龐大壓力,要縮減板覆蓋區,並且降低成本與複雜度。後者對於縮短開發時間相當重要,以便符合逐漸縮短的上市時間間隔。

為了因應諸多應用難題,工程師必須將其儀表與量測時脈解決方案,從客製化的傳統離散式設計,轉換成整合度更高的解決方案。達成此目標有個重要步驟就是使用整合式轉換鎖相迴路 (PLL)。如此即可張讓傳統的壓控振盪器 (VCO) 訊號向上升頻,同時顯著維持固定外接式局部振盪器 (LO) 的抖動與相位雜訊。

本文將探討轉換迴路在達到業界最低整體相位雜訊的目標上所扮演的角色。為了舉例說明,本文將介紹 Analog Devices 的 ADF4401A 轉換迴路系統級封裝 (TL SiP),並且說明如何透過低於 10 fs rms 廣頻整體抖動能力的輸出訊號因應效能需求,並以增強的隔離能力來衰退寄生元件,同時符合設計人員對於整合度、成本、複雜性以及上市時間的要求。

傳統 PLL 與轉換迴路的操作比較

轉換迴路的主要用途是產生可鎖定在輸入參考訊號的輸出訊號,且與傳統 PLL 相比,可大幅降低頻內相位雜訊。

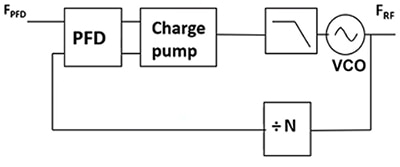

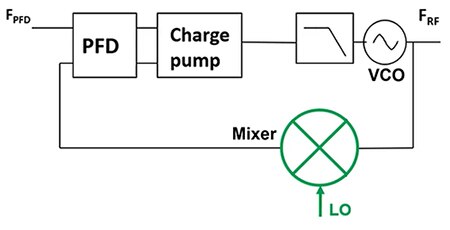

標準 PLL 含有回授系統,其中具有相位頻率偵測器 (PFD)、電荷幫浦、低通濾波器 (LPF)、VCO,以及一個回授分頻器 N (圖 1)。

圖 1:標準 PLL 會鎖定在較低的頻率 (FPFD) 基準,並且產生輸出頻率 (FRF)。(圖片來源:Bonnie Baker)

圖 1:標準 PLL 會鎖定在較低的頻率 (FPFD) 基準,並且產生輸出頻率 (FRF)。(圖片來源:Bonnie Baker)

PFD 會將輸入基準的相位與回授訊號的相位進行比較,然後產生一連串與兩者之間相位誤差成比例的脈衝。電荷幫浦會接收 PFD 脈衝並且將其轉換成電流源或下降脈衝,再藉此向上或向下微調 VCO 的頻率。LPF 會消除脈衝的所有高頻能量,然後轉換成 VCO 可使用的電壓。VCO 的輸出訊號會透過 N 分頻器回授到 PFD 區塊,以便完成迴路。

圖 1 的頻率轉移功能可使用方程式 1 計算:

![]() 方程式 1

方程式 1

FRF 是輸出頻率

N 是回授分頻器比 (可為整數或分數)

FPFD 是 PFD 頻率

圖 1 的頻內底噪可使用方程式 2 計算:

![]() 方程式 2

方程式 2

FOMPLL 是 PLL 的頻內相位底噪效能指數 (FOM)

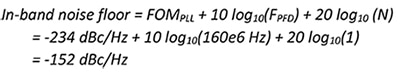

以 -234 dB/Hz 的頻內相位底噪 FOM、160 MHz 的 PFD 頻率 (FPFD) 以及 8 GHz 的輸出頻率 (FRF) 為例說明。

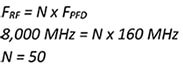

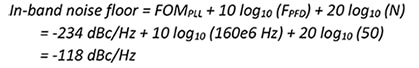

針對此系統,可使用方程式 1 來計算 N 的值:

方程式 2 可用來計算頻內底噪:

在上述計算中,N 分頻器會大幅影響整體的頻內底噪,來到 20 log10 (50),等於 34 dB。更小的 N 值會降低頻內底噪,但也會降低輸出頻率。因此,要如何產生高輸出頻率又保持較低的迴路增益 (N) 呢?

圖 2:從本例的標準 PLL 來看,回授分頻器的 (20 log10(N)) 雜訊與 N = 1 時的較低黃線相比,有 34 dB 的較高頻內雜訊。(圖片來源:Bonnie Baker)

圖 2:從本例的標準 PLL 來看,回授分頻器的 (20 log10(N)) 雜訊與 N = 1 時的較低黃線相比,有 34 dB 的較高頻內雜訊。(圖片來源:Bonnie Baker)

要解決此問題,就要用降轉混頻級來取代 N 分頻器 (圖 3)。

圖 3:轉換迴路使用混頻器將 VCO 頻率降轉成 PFD 頻率,而非使用傳統的回授分頻器。(圖片來源:Bonnie Baker)

圖 3:轉換迴路使用混頻器將 VCO 頻率降轉成 PFD 頻率,而非使用傳統的回授分頻器。(圖片來源:Bonnie Baker)

在圖 3 中,混頻器取代了 N 分頻器,因此迴路增益等於 1 (N = 1)。此操作會大幅削減回授迴路對頻內底噪的影響。若要進行頻內底噪的計算,N 值現在等於 1。透過方程式 2,改裝系統的頻內底噪如下所示:

新的頻內底噪顯示已改善 34 dBc/Hz。

在圖 3 中,混頻器仰賴極低雜訊 LO 運作,稱為偏移 LO。FLO ± FRF 必須等於 FPFD 才可達到鎖定。

在轉換迴路架構下,偏移 LO 的相位雜訊對於達到 RF 輸出最佳效能來說非常重要。有鑑於此,工程師通常會依據壓控表面聲波 (SAW)、振盪器 (VCSO)、梳型產生器,或介質共振腔振盪器 (DRO) 來設計偏移 LO。註:如需偏移 LO 的設計支援,請洽 Analog Devices。

轉換迴路的難題

一般來說,低雜訊轉換迴路的設計會牽涉到多種電路區塊的實作,因此會讓設計複雜,尺寸變大且靈活性受限。除此之外,整個電路必須經過驗證,並且針對目標操作進行特性化。舉例而言,有個重大的設計考量在於對 RF 輸出訊號的 LO 洩漏 (LO 對 RF 隔離)。這對工程師是要克服的重大挑戰。在傳統設計中,工程師通常要經過多次設計迭代,才能達到最佳化效能與適當的隔離。

圖 3 指出 ADF4401A 如何整合主要的電路區塊以提供完全特色化的解決方案,並且消除與轉換迴路設計相關的傳統難處。此可編程解決方案能讓工程師在第一次動手就達到最佳化效能,並可縮短上市時間。

評估 ADF4401A

ADF4401A 的設計可使用頻率產生解決方案搭配 62.5 MHz 至 8 GHz 的 RF 頻率,協助工程師縮短高效能儀器的上市時間。透過降轉混頻器,ADF4401A 可達到超低的頻內雜訊,從 100 Hz 至 100 MHz 的廣頻抖動為 ~9 fs。ADF4401A 內部的設計與佈局技術,可促成 90 dBc 的典型無雜散動態範圍。封裝尺寸為 18 x 18 x 2.018 mm,與傳統離散式設計相比,板空間大幅縮小。

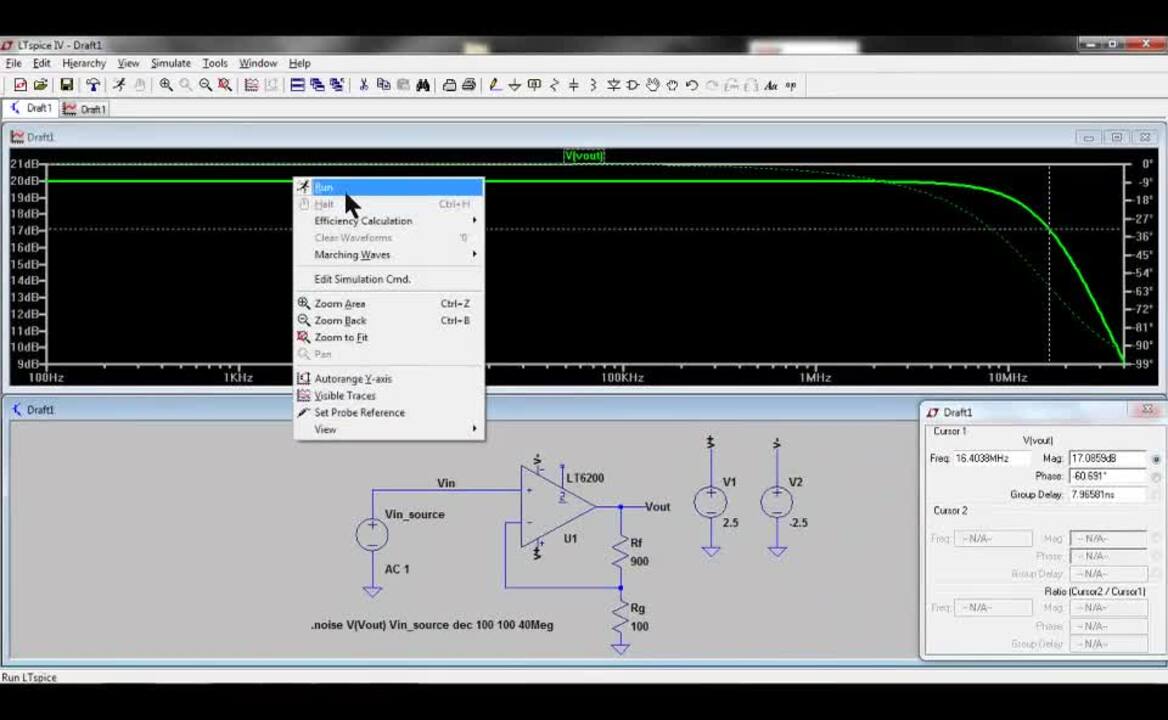

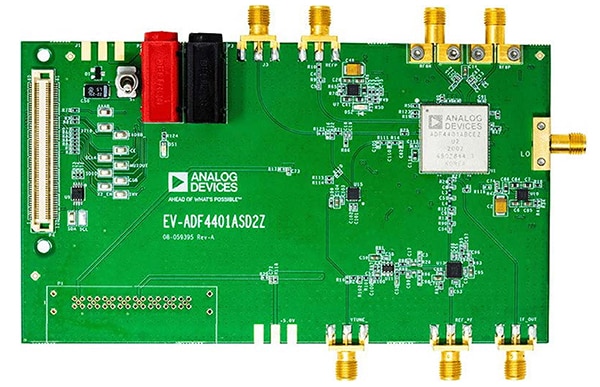

若要評估此裝置的效能,設計人員可使用 EV-ADF4401ASD2Z 評估板 (圖 4)。此板件含有完整的轉換迴路,包括外部 PFD (HMC3716)、主動濾波器 (LT6200),以及一個多工器 (ADG1609)。

圖 4:ADF4401A 轉換迴路模組用的 EV-ADF4401ASD2Z 評估板含有一個外接 PFD、USB 介面以及穩壓器。(圖片來源:Analog Devices)

圖 4:ADF4401A 轉換迴路模組用的 EV-ADF4401ASD2Z 評估板含有一個外接 PFD、USB 介面以及穩壓器。(圖片來源:Analog Devices)

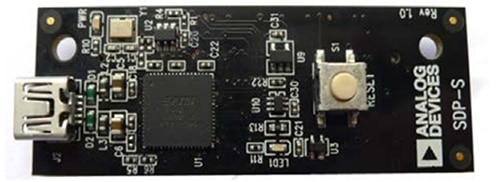

EV-ADF4401ASD2Z 含有 ADF4401A TL SiP (含整合式 VCO)、迴路濾波器 (5 MHz)、PFD、USB 介面,以及穩壓器。此外,EV-ADF4401ASD2Z 需要 EVAL-SDP-CS1Z (SDP-S) 系統展示平台 (SDP) 控制器板 (圖 5)。此板件提供 USB 連接,可從 PC 接至 EV-ADF4401ASD2Z,因此可進行編程。EV-ADF4401ASD2Z 套件並未提供控制器板。

圖 5:需要 EVAL-SDP-CS1Z (或 SDP-S) 控制器板才可提供 USB 連接,從 EV-ADF4401ASD2Z 接至 PC 進行編程。(圖片來源:Analog Devices)

圖 5:需要 EVAL-SDP-CS1Z (或 SDP-S) 控制器板才可提供 USB 連接,從 EV-ADF4401ASD2Z 接至 PC 進行編程。(圖片來源:Analog Devices)

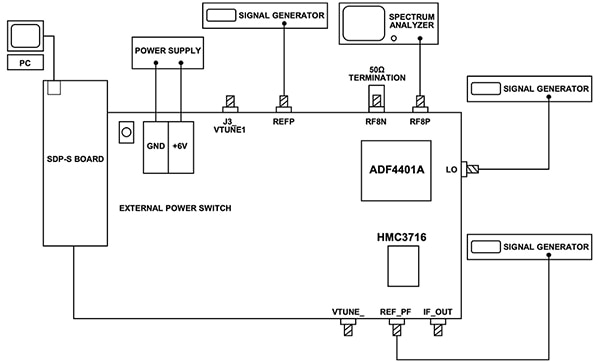

圖 6 呈現 EV-ADF4401ASD2Z 系統的實體連接。相關的 分析 | 控制 | 評估 (ACE) 軟體可控制 TL SiP 功能。電力來自外部施加的 6 V 電源供應器。

圖 6:EV-ADF4401ASD2Z 設置圖顯示,要評估 ADF4401A 所需的設備與連接,包括 SDP-S 控制板、PC、電源供應器、訊號產生器,以及頻譜分析器。(圖片來源:Analog Devices)

圖 6:EV-ADF4401ASD2Z 設置圖顯示,要評估 ADF4401A 所需的設備與連接,包括 SDP-S 控制板、PC、電源供應器、訊號產生器,以及頻譜分析器。(圖片來源:Analog Devices)

建議搭配此評估板一起使用的設備包括 Windows PC、頻譜分析器或訊號源分析器以及三個訊號產生器。

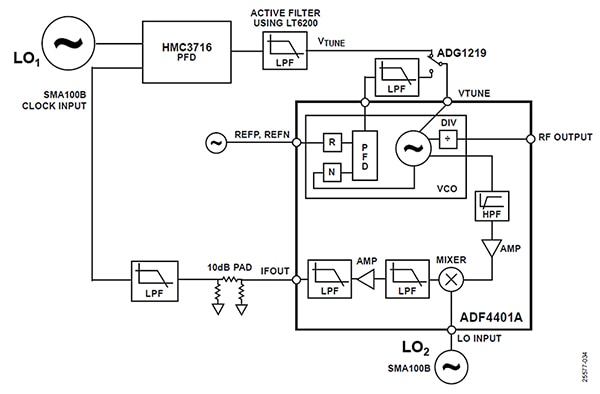

EV-ADF4401ASD2Z 的方塊圖顯示 ADF4401A 模組,以及 Analog Devices 的 HMC3716 PFD、LT6200 運算放大器,以及 ADG1219 SPDT 開關 (圖 7)。

圖 7:EV-ADF4401ASD2Z 評估板方塊圖顯示出可支援 AD4401A 轉換迴路的主要元件。(圖片來源:Analog Devices)

圖 7:EV-ADF4401ASD2Z 評估板方塊圖顯示出可支援 AD4401A 轉換迴路的主要元件。(圖片來源:Analog Devices)

使用可在高頻率操作的 PFD 相當重要,如此即可將分頻器的需求降至最低,以免其導致頻內雜訊的反應降級。Analog Devices 的 HMC3716 具有 1.3 GHz 相位比較頻率能力,因此非常適合用於 ADF4401A 的 IF 範圍。此類電路具有頻率與相位比較的能力,因此無需額外電路,即可將頻率導向預計的輸出頻率。HMC3716 成為外部 PFD 以便完成偏移迴路。HMC3716 具有高頻操作範圍與超高相位底噪,因此可用來設計大頻寬迴路濾波器。

在圖 7 中,LT6200 運算放大器搭配 LPF 配置,會衰減高頻突波,ADG1219 開關則會完成系統的轉換迴路。

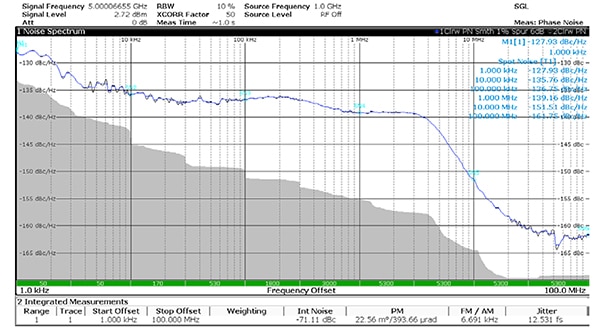

EV-ADF4401ASD2Z 評估設備會產生頻內雜訊圖與抖動量測值,如圖 8 所示。

圖 8:在 5 GHz 時的單一邊帶相位雜訊、外部 HMC3716 的 500 MHz 參考頻率,以及 4.5 GHz 時的外部 LO。(圖片來源:Analog Devices)

圖 8:在 5 GHz 時的單一邊帶相位雜訊、外部 HMC3716 的 500 MHz 參考頻率,以及 4.5 GHz 時的外部 LO。(圖片來源:Analog Devices)

在圖 8 中,LO2 與 HMC3716 輸入屬於 SMA100B RF 與微波訊號生器。評估板的 LO2 頻內雜訊約為 -135 dBc/Hz,這在最高達 300 kHz 的低偏移下尤其明顯。LO2、ADF4401A 模組、HMC3716 PFD 以及迴路濾波器會共同促成約為 -140 dBc/Hz 的頻內雜訊。內部相位雜訊約在 5 MHz 至 50 MHz 之間,設備的相位底噪約為 -160 dBc/Hz。這些項目可達到一共 12.53 fs 的 rms 抖動。

結論

高速儀器系統需要及低抖動的時脈,以確保輸出數據不受損壞。工程師的難處在於找到可打造高速 GHz 時脈系統的適當裝置。ADF4401A 轉換迴路可大幅簡化裝置的挑選作業,以便打造時脈系統,並可提供小巧模組,確保在較高頻率時達到低抖動,同時縮減板空間、降低成本並縮短上市時間。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。