精密薄膜技術

2021-08-24

本文旨在協助電路設計人員和元件工程師加深對薄膜技術的知識,不僅可幫助讀者瞭解薄膜技術的用途,還有此技術在可靠度、尺寸和效能方面具備的顯著優點。

圖 1:Vishay 的薄膜技術。(圖片來源:Vishay)

圖 1:Vishay 的薄膜技術。(圖片來源:Vishay)

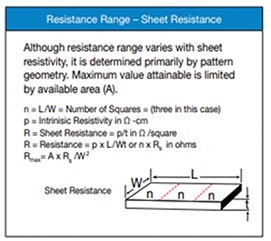

薄膜類型

通常薄膜噴鍍厚度約 500 埃。不同線寬和線間距的一各式遮罩,可用來製造不同歐姆值的電阻。薄膜電阻率也不同,可從 50 Ohm/sq 到 2000 Ohm/sq。每種薄膜都有特定用途。一般來說,薄膜電阻率越低,整體電氣效能越佳。Vishay 是唯一供應並製造所有薄膜類型的公司。

鎳鉻合金 (NiCr) - 最常用的薄膜,擁有最佳的絕對 TCR 電氣規格。常見的薄膜電阻率為 50、100 和 200 Ohm/Sq。

Tamelox - 自行研發的 Vishay 薄膜合金,結合鎳鉻合金和氮化鉭的優點,可提升 TCR 的線性。

氮化鉭 (TaN2) - 正確的沉積和加工後,可產生水分無法滲透的合金。電氣效能不及鎳鉻合金,可用於其電阻會遇到低功耗 (低於 20%)、無自體發熱和高相對濕度 (80%) 的應用中。

矽鉻 (SiCr) - 此材質具有極高的薄膜電阻率 (2000-3000),可在小區域內產生高電阻。絕對 TCR 追蹤、長期穩定性、電壓係數等電氣規格都優於厚膜技術。

鈍化 - 特殊鈍化方法 (SPM) 現在可在嚴苛環境條件下進行強化鈍化控制 (請參考 SPM 技術文件)。

薄膜整合式架構

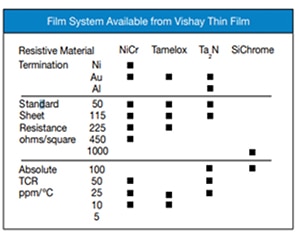

積體電路是由許多元件組合而成,這些元件在共同基板上成形且互連,形成一個功能性網路。積體電阻網路定義類似,係由電阻元件組合而成,且在共同基板上成形且互連。在半導體製程中,這些元件的生產方式為在基板上沉積或與基板發生反應,而圖樣則可透過光刻成像產生,接著部分移除多餘的材料。特定網路中的電阻,由於尺寸小且極靠近,導致在加工過程中所的環境條件幾乎相同。同樣地,晶圓或基板上的每個網路的環境條件也幾乎相同。由於數個晶圓會在相同的設備中同時加工,因此整個批次 (數百或數千個個別單位) 的特性均會一致。整合式架構的附加優點是互連的完整性,會比個別連接的離散元件更可靠。

圖 2:薄膜整合式架構高純度礬土晶圓。(圖片來源:Vishay)

圖 2:薄膜整合式架構高純度礬土晶圓。(圖片來源:Vishay)

薄膜整合式架構的優點

- 緊密相接網路中所有元件,進而確保能在溫度範圍內及整個壽命期間進行密切追蹤

- 尺寸相當小、密度高的多元件網路,能節省印刷電路板區域

- 氣密式結構,適用於現今各式標準形式

- 「零件與零件」以及「批次與批次」具有可重複且一致的特性

- 超低電感值

- 卓越的可靠度 - 更少個別互連

- 無熱電效應

- 安裝成本低於離散元件 - 通常更低

互連可靠度

軍方單位及其他機構的可靠度研究中顯示,在其他條件皆相同,組件的可靠度與「人造互連」數有直接成比例的關係。這也是積體電路比離散式電晶體的組件更可靠的原因,此一原因也影響了整合式電阻的網路和離散式電阻之間的良窳,這種可靠度有時也稱為「固有可靠度」。

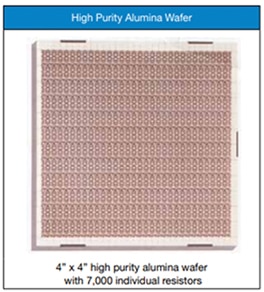

阻抗值範圍

薄膜技術採用光刻精密圖樣製作,可讓設計人員以盡可能最小的區域,提供眾多電阻值。如此便能將元件尺寸最小化,或是在相同空間內增加電阻的數目。在特定區域內達成的總阻抗,主要取決於薄膜材料的薄膜電阻率和圖樣製作。但在實際設計中,由於端接墊、內部導體、特殊修整特性和引腳排列限制條件等所需的空間需求,導致所利用到的最大區域減少。

薄膜電阻材質的正常薄膜阻抗範圍介於 50 至 2000 ohm/sq,因此個別電阻可提供的阻抗範圍介於數歐姆到數百萬歐姆之間。最高的精密度通常在 250 Ω 到 100 kΩ 之間。

圖 3:阻抗值範圍主要由晶圓上的圖樣幾何形狀來決定。(圖片來源:Vishay)

圖 3:阻抗值範圍主要由晶圓上的圖樣幾何形狀來決定。(圖片來源:Vishay)

超低電阻

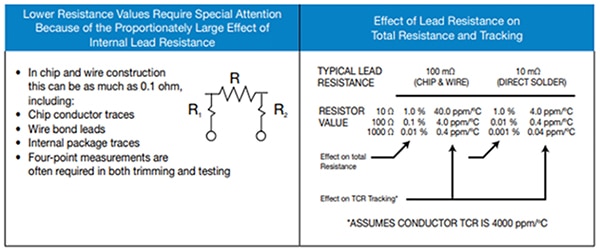

將低阻抗元件納入精密網路時,微小但不可避免的引線電阻,以及晶片上及封裝內的和導電圖樣,都必須納入考量。這些引線效應可透過適當的設計、加工、封裝選擇及組裝降到最低,但無法完全消除。然而,務必要特別留意規格的設定,特別是在阻抗和追蹤方面的實際可行容差,以及容差的測量方式。

圖 4:內部引線阻抗能對總阻抗值造成巨大影響。(圖片來源:Vishay)

圖 4:內部引線阻抗能對總阻抗值造成巨大影響。(圖片來源:Vishay)

阻抗容差

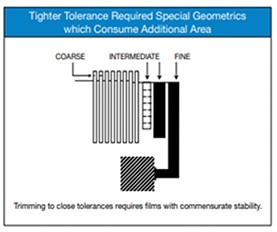

現代雷射系統可將各個電阻調整為數值接近的容差,其絕對值或相對值分別為:0.01% 和 0.005%。此外,負責生產的製造商實際上會「防護」修整頻帶,因此內部規格會比發佈的規格更為嚴格。

所需的容差越接近,電阻的設計便需要更仔細,以便讓分佈緊湊且在容差限制內,並且讓整修速度達到成本效益。要達成此目標的方式之一是提供特殊的修整幾何形狀。這些特點可將電阻的靈敏度降到雷射除去材料部分的數量,以取得接下來的更高準確程度。這些特點利用額外的基板區域,有時還需要在成本和效益之間作出取捨。現代薄膜技術之所以可用於精密網路中,其與眾不同的特色之一便是薄膜的電氣和機械性的穩定度。這點相當重要,因為緊密修整的電阻有時必須在組裝中忍受極大應力,且不能有重大的漂移。這再度強調整合式架構的固有優勢優於多個離散式電阻,因為其中若發生任何變化,都同樣會發生在網路中的所有電阻,從而便能精密地保持修整的比例值。

圖 5:更嚴格的容差要求可能使用到額外區域。(圖片來源:Vishay)

圖 5:更嚴格的容差要求可能使用到額外區域。(圖片來源:Vishay)

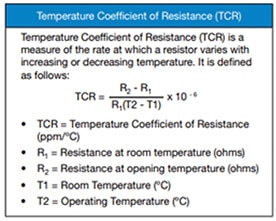

電阻溫度係數 (TCR)

電阻溫度係數是以環境溫度的函數來測量阻抗的變化。其定義是每單位溫度下的阻抗變化,通常是以每攝氏溫度的百萬分之一 (ppm/°C) 表示。這是最常用來特性化或差別化電阻的屬性。以往離散式電阻 (包括以薄膜製成者) 會根據 TCR 值按批次分級。相對較新的方式使用噴鍍沉積來控制薄膜的組成,再加上加工的改進,造就了所謂的「第三代」薄膜產品,其 TCR 都同樣低於 10 ppm/°C (絕對值)。

圖 6:電阻溫度係數是用來衡量電阻隨著溫度上升或下降的變化率。(圖片來源:Vishay)

圖 6:電阻溫度係數是用來衡量電阻隨著溫度上升或下降的變化率。(圖片來源:Vishay)

TCR 通常是藉由實驗來判定,其方式是測量數個溫度下的電阻,並計算在適當溫度間隔 (如 +25°C 至 +125°C) 內的變化比率。如果電阻隨著溫度呈線性變化,則 TCR 是個常數,且無論溫度間隔為何都不會改變。若為非線性 (如同普遍使用的鎳/鉻合金的情況),則 TCR 表示為阻抗與溫度關係曲線上兩點 (如 +25°C 和 +125°C) 連線後所得的斜率。換句話說,這是此間隔期間內的平均 TCR。其間的關係越是呈現非線性,平均數的估算值就越差。

在指明 TCR 時,也需一併清楚指明溫度間隔。

MIL-STD-202 方法 304 所說明的程序,往往都會作為測量 TCR 的參考標準。在此方法中,會針對一系列介於 +25°C 和 -55°C 以及 +25°C 和 +125°C 之間的間隔,計算出平均 TCR。最高的值會被記錄為 TCR。這方法會反映完整的軍規作業範圍,但是,對於具有不同或較狹窄工作溫度間隔的元件來說,可能導致規格過度指定的情形。

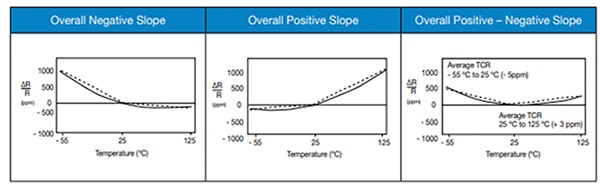

圖 7:產生不同斜率之 TCR 的範例。(圖片來源:Vishay)

圖 7:產生不同斜率之 TCR 的範例。(圖片來源:Vishay)

透過瞭解合金組成的效應,以及小心控制加工的能力,即可能「量身訂製」電阻與溫度的關係曲線,以產生出具有以下特性的 TCR:(1) 在整個範圍內都為負數;(2) 在整個範圍內都是正數;或 (3) 在低端為負,在高端為正,且在大約室溫範圍是相對平整的「零 TCR」區段。此方式有利於在接近室溫下作業、或其他需要溫度補償的設備。

追蹤

多數使用精密薄膜網路的應用,都需要達成並維持相近的相對電阻值。因此,網路內阻抗的相對變化 (稱為「追蹤」) 便非常重要。薄膜網路在追蹤方面極為優異。追蹤有數種不同的面向,能夠瞭解並區分它們非常重要。

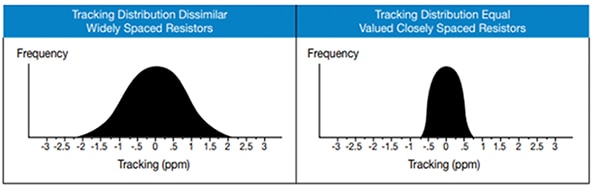

TCR 追蹤 - TCR 追蹤的定義是:一對電阻的 TCR 在特定溫度間隔內的差異。離散式電阻若要達成緊密 TCR 追蹤相當困難,且製造程序要產生數值極為接近的絕對 TCR 限值也是困難重重。相較之下,薄膜網路的整合式架構由於電阻是在幾乎相同的製程條件下同批生產,因此可確保獲得極度緊密的 TCR 追蹤。此外,這些電阻較小且在高熱傳導率的共同基板表面上都放置很接近,因此會在相同或接近的溫度下運作。

儘管如此,仍會發生製程和材料的變化,結果在相同晶圓上鄰近的電阻,會產生微小但可測量的 TCR 差異。不均勻的薄膜沉積、基板缺陷、退火過程中的熱梯度、不均勻的應力都是可能造成影響的製程變數。設計也會有所影響。然而,透過採用最先進的製程控制、測量的設備和技術,在適當的電路和晶片配置和封裝條件下,TCR 追蹤可以控制在每度為千萬分之幾的範圍內。

導致表面上 TCR 追蹤高於「真實」追蹤的一個因素,就是存在一個具有可測量阻抗 (r) 的一般分接頭引線。

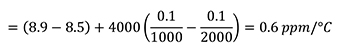

![]()

其中 TCR (r) 是常見引線材料的 TCR,通常是金屬材料。例如:TCR 為 8.9 ppm/°C 的 1 kΩ 電阻連接到 TCR 為 8.5 ppm/°C 的 2 kΩ 電阻,以及 TCR (r) 為 4000 ppm/°C 且阻抗為 0.1 Ω 的共用輸出引線,都將表現出 TCR 追蹤的特性。

如果臨界比是根據電壓分壓而不是阻抗比來指定和測量,那麼一般引線 (在上述情況中為 0.2) 的外部貢獻就會消失。

圖 8:寬廣和緊密間隔電阻的追蹤分佈範例。(圖片來源:Vishay)

圖 8:寬廣和緊密間隔電阻的追蹤分佈範例。(圖片來源:Vishay)

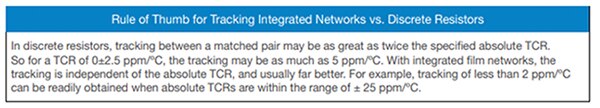

圖 9:追蹤整合式網路與離散電阻的經驗法則。(圖片來源:Vishay)

圖 9:追蹤整合式網路與離散電阻的經驗法則。(圖片來源:Vishay)

電源切換下的阻抗追蹤

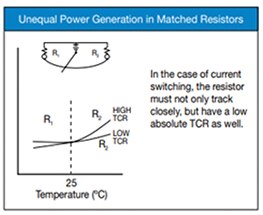

有些電路的運作模式是在一個電阻中切斷和接通電流,這與攜帶恆定電流的參考電阻相符。在這種情況下,即使電阻可能具有相同的 TCR,並且基板可能處於均勻的環境溫度下,阻抗值也會因自體發熱而不同。(嚴格說來,這不是真正的「追蹤」要求,因為想要注意的電阻會受到不同的應力。)這種差異將受制於兩個電阻的絕對 TCR。在這些並非少見的應用中,電阻在工作溫度範圍內應具有盡可能最低的絕對 TCR,並且電阻設計應盡可能緊密,以便盡可能減小電阻之間的溫差。

圖 10:在匹配電阻中產生功率不相等的範例。(圖片來源:Vishay)

圖 10:在匹配電阻中產生功率不相等的範例。(圖片來源:Vishay)

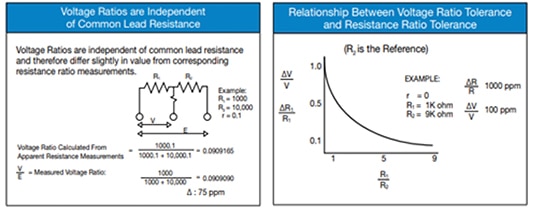

電壓比

電阻經常作為分壓器使用。在這種情況下,且在涉及精確容差下,處理電壓比要比處理阻抗比更合適。在與阻抗比進行比較時,需要瞭解電壓比的三個重要面向,分別是電壓比本身、電壓比的容差、電壓比追蹤。

圖 11:電壓比與一般引線阻抗無關。(圖片來源:Vishay)

圖 11:電壓比與一般引線阻抗無關。(圖片來源:Vishay)

理想情況下,一對電阻兩端間的壓降,是由阻抗值的比例決定:R1/(R1 + R2)。當阻抗值不相等時,電壓比將不同於從表面上的 (測量的) 阻抗值計算所得的電壓比,其差異取決於一般引線的阻抗。這種差異可能相當顯著,尤其是低數值的電阻。

對於與 1 kΩ 電阻串聯的 10 kΩ 電阻,且具有 100 mΩ 阻抗的共同「分接頭」引線,兩個比值將相差 75 ppm:

對於與 100 Ω 電阻串聯的 1 kΩ 電阻,100 mΩ 分接頭阻抗將在個別的比值上產生 800 ppm 以上的差異。

這說明了指定正確操作參數的重要性。

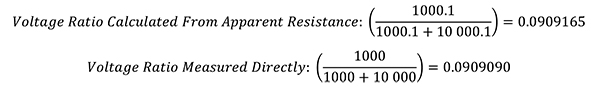

圖 12:電壓比容差和電壓比追蹤方程式。(圖片來源:Vishay)

圖 12:電壓比容差和電壓比追蹤方程式。(圖片來源:Vishay)

然而,當一般引線阻抗 (r) 為可測量時,如前所示,表面上的 TCR 追蹤高於「真實」追蹤,電壓比追蹤則比較低。電壓比追蹤總是小於 (優於) TCR 追蹤。

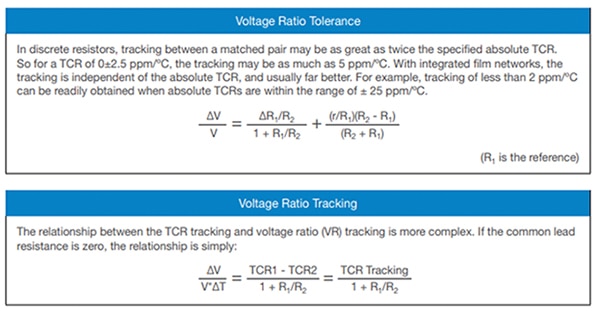

穩定性

前幾節描述的效應是可逆的:這些變化並非永久性,當溫度回到起始點時就會消失。但也會有不可逆的效應。如前所述,大多數精密電阻網路都在比例模式下使用。這類電阻已被修整至嚴格的容差內,且經過精心設計,以便在電阻或電壓比初始嚴格的容差內進行追蹤。但是,除非這些容差能在網路的整個生命週期內保持不變,否則這麼做是毫無意義的。這就需要薄膜有最大的穩定度。值得注意的是,在材料和製程方面的最新發展,已將薄膜的穩定度提升到前所未有的程度,接近到以前只能使用箔片才能獲得的穩定性程度。

大量的鎳/鉻合金長期穩定性測試已明確結論說,電阻隨時間的變化率是基板溫度這單一數值的函數。這是一種說明溫度是唯一變數的數學表示法,而且無論這是由功率載入,還是只因環境引起都可適用。此外,經由實驗確定,根據典型的動力方程式,在較高溫度下測量的穩定性,可以放心地外推到較低溫度和更長的時間。

將一對匹配電阻的永久性變化視為「穩定性追蹤」相當有用。若與 TCR 追蹤 (即密切追蹤與絕對 TCR 無關) 相比,穩定性追蹤在某種程度上取決於絕對穩定性。一對電阻若是越穩定,其絕對值和相互關係的變化就越小。這再度證明整合式結構的優勢相當顯著:網路中的所有電阻在生命週期中往往會發生類似的變化,並且阻抗比的變化遠小於絕對值。

圖 13:穩定性受元件老化影響。(圖片來源:Vishay)

圖 13:穩定性受元件老化影響。(圖片來源:Vishay)

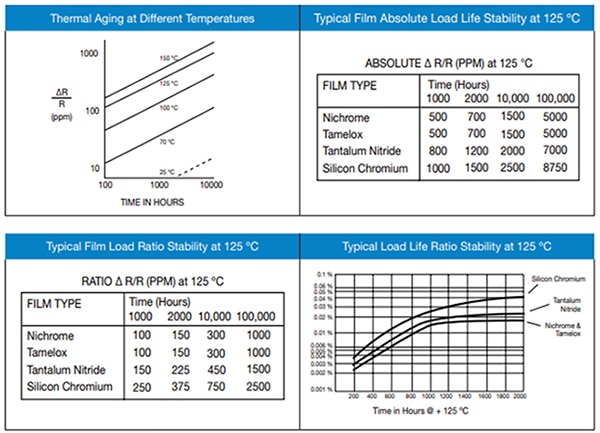

額定功率

由於薄膜精密網路通常不用於高功率應用中,因此確定最大額定功率的方法,不像在一般用途網路中的那樣關鍵。但是,必須設定限值,最好是透過確定溫度上限來完成。

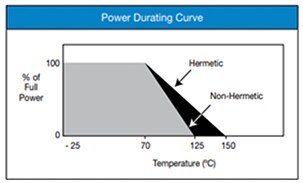

零功率溫度 (有時稱為最高工作溫度) 是零件在規定的時間內 (通常是 1000 小時內),在沒有過度變化 (通常根據初始容差來定義) 下可以工作的最高溫度,此值會以百分比表示。對於需要保持 0.1% 容差的薄膜網路,此零功率溫度為 +150°C。在此溫度下,電阻可能會表現出大約 500 ppm 絕對值的變化,或相對於網路中其他電阻,出現大約 100 ppm 相對值的變化。如果所需的最大初始容差為 0.01%,則更合適的零功率溫度為 +125°C。這些數值等級適用於氣密式零件。如果採用非氣密式封裝,則零件的額定溫度會較低。

圖 14:典型功率降額曲線。(圖片來源:Vishay)

圖 14:典型功率降額曲線。(圖片來源:Vishay)

全功率額定值 - 一般認為,額定功率是零件表面溫度從某個環境溫度以上 (通常為 +70℃) 的溫度,提高至零功率溫度所需的功率。此數值是以瓦特全功率表示。功率降額曲線用來確定在中間溫度下的限值。

必須特別考慮網路中個別電阻的額定值,因為單一電阻的最終表面溫度,會因為網路中其他電阻是否存在功率而存在很大的差異。雖然很難一概而論,但適當的網路設計能提供一致的功率密度來解決這些潛在的變化。

如上所述,雖然在容差更接近的精密網路中,功率等級通常設定得較低,但由於晶片尺寸較小,因此功率密度可能很高。對於非常精確的網路,典型的設計等級為 25 W/in2,但薄膜能夠維持非常高的功率密度等級 (高達 200 W/in2),且不損害其完整性。最後需考慮的是,必須容許封裝熱阻差異很大的事實。

電阻電壓係數和電流雜訊

這兩個特性對於由金屬陶瓷或聚合物等複合材料製成的電阻來說,可能是一個相當嚴重的缺點,但通常可以在薄膜精密網路中被忽略,因為其數值大小是相當小的。這是單晶片薄膜材料的主要優點之一。

電阻電壓係數是每單位電壓變化下的單位阻抗變化,以 ppm/V 表示。這是一種衡量無電阻行為的方式,並且在薄膜中,僅在百萬歐姆範圍內才會達到可識別的等級,其測量值約為 0.1 ppm/V。

電流雜訊是使用 Quantek 公司開發的標準儀器來進行特性化及測量。薄膜的典型值將小於 -35 dB。

熱電效應

如果電阻兩個終端的溫度不同,可能會產生熱電電壓。對於離散電阻來說,這可能是一個嚴重的問題,因為在相對較大尺寸的範圍內可能存在熱梯度。所有在薄膜網路中的電阻都在相同或接近的溫度下,這是由於其尺寸較小和導熱基板的散熱效應所致。薄膜上的熱電效應通常是小於 0.1 µV/°C。

電阻的頻率響應

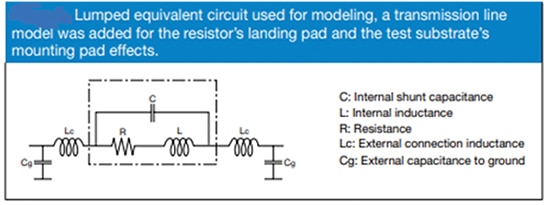

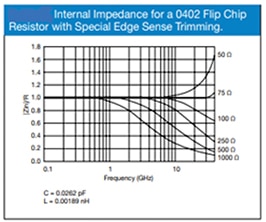

若頻率大於 100 MHz,大多數電阻須視為具有寄生電感和電容的等效電路,請參閱圖 15。典型的阻抗響應如圖 16 所示。阻抗響應取決於電阻的尺寸、修整方法、零件數值和端接樣式。

圖 15:若頻率大於 100 MHz,大多數電阻須視為具有寄生電感和電容的等效電路。(圖片來源:Vishay)

圖 15:若頻率大於 100 MHz,大多數電阻須視為具有寄生電感和電容的等效電路。(圖片來源:Vishay)

圖 16:具有特殊邊緣感應修整的 0402 覆晶電阻的典型內部阻抗響應。(圖片來源:Vishay)

圖 16:具有特殊邊緣感應修整的 0402 覆晶電阻的典型內部阻抗響應。(圖片來源:Vishay)

若要降低寄生阻抗,考慮其尺寸是非常重要的。尺寸越小,零件的效能就越接近理想電阻。修整樣式也很重要。

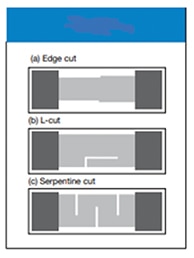

薄膜電阻能以各種不同幾何設計進行修整,請參閱圖 17。藉著在觸點墊片之間的中心維持矩形的設計 (已平衡),而非其他樣式 (如蛇形或 L 形修整),可提高元件的效能。

圖 17:薄膜電阻能以各種不同幾何設計進行修整。(圖片來源:Vishay)

圖 17:薄膜電阻能以各種不同幾何設計進行修整。(圖片來源:Vishay)

有關 Vishay 薄膜電阻的資訊,請參閱以下連結的資料

引線式網路

表面黏著式晶片

通孔

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。