如何在資源受限的應用中使用 FPGA

資料提供者:DigiKey 北美編輯群

2025-05-07

可配置邏輯對資源受限的嵌入式系統來說,需求不斷增加。邊緣 AI、機器視覺和工業自動化等應用皆需靈活的特定應用邏輯,以符合不斷變化的效能要求,同時還得在嚴格的功耗、尺寸和成本限制下運作。現代化的現場可編程閘陣列 (FPGA) 就可因應這些彼此競爭的要求。

本文將探討挑選資源受限型應用的 FPGA 時要考量的關鍵設計條件。接著會以 Altera 的功耗與成本最佳化 FPGA 產品組合當作範例,說明不同的產品系列該如何配合特定情境。最後會重點介紹可用於原型開發和設計概念驗證的開發套件和評估板。

挑選 FPGA 時的考量事項

針對資源受限系統挑選 FPGA 時,要考量眾多設計要求,讓這些要求與正確的解決方案互相配合。有幾個關鍵的 FPGA 特性要考量:

邏輯元件 (LE) 容量:FPGA 的基本建構模塊就是 LE,因此其數量會決定可實作的客製化邏輯量。數量越多就可達到更複雜的設計,但代價是功率、成本和封裝尺寸會增加。

I/O 和記憶體:FPGA 通常用於連接系統內的不同元件,因此 I/O 引腳的數量會是關鍵的考量因素。為了提高 I/O 效能,許多 FPGA 都會在 PCI Express (PCIe)、高速記憶體和數 Gigabit 的收發器等介面中納入硬化的固定式邏輯模塊。

此外,有些 FPGA 還會整合像是類比數位轉換器 (ADC) 和快閃記憶體等特點。這些增強特點可以減少對輔助晶片的需求,進而節省電路板空間並提高電源效率。

處理器整合:無需使用外部處理器,可在 FPGA 中實作「軟」微處理器單元 (MPU)。這種作法可以縮小系統的覆蓋區,但最適合 MPU 工作負載要求較低的應用。

對於需要更快、更高效 MPU 的應用,設計人員可以考慮使用具有硬處理器系統 (HPS) 的 FPGA,其可將 MPU 實作成 FPGA 中的固定邏輯模塊。

硬體加速器:FPGA 通常含有專用的數位訊號處理 (DSP) 模塊,可有效處理運動控制等運算密集型任務。更高階的裝置可能具有 AI 工作負載用的特殊 Tensor 模塊。不同 FPGA 系列間的加速器模塊功能差異很大,也會大幅影響整體系統效能。

封裝和功耗最佳化:有些 FPGA 經過專門設計,可將實體與電氣覆蓋區縮至最小。例如,可能會提供低功耗睡眠模式。

工具:製作客製化邏輯可能會是艱鉅的挑戰,尤其對剛接觸此製程的設計人員而言。像是 Altera 的 Quartus Prime 設計軟體等工具就可簡化此流程。

Quartus Prime 可讓 FPGA 設計更容易取用,能提供開發人員友善的體驗、豐富的預先建構邏輯模塊目錄,並可自動與這些邏輯模塊自動互連。此工具與常見的 AI 和機器學習 (ML) 工作流程整合,能讓開發人員在 FPGA 上部署 Linux 和 Zephyr 等常見的作業系統 (OS)。

諸如此類的功能可以大幅加速 FPGA 設計,因此工具的特點成了挑選裝置時的關鍵考量因素。

適用於進階嵌入式工作負載的高效能運算

為了說明設計要求如何影響 FPGA 的挑選,從需要優異運算密度、頻寬和整合的高階應用開始將有所幫助。範例包括進階邊緣 AI 應用和高效能工業閘道器。

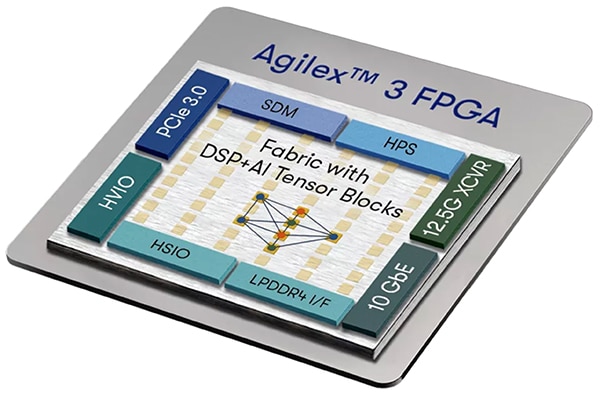

Agilex 3 FPGA (圖 1) 可滿足這些應用的需求,可提供高達 135K 的 LE。此晶片提供純 FPGA 和系統單晶片 (SoC) 兩種款式。此 SoC 裝置整合了雙核心 800 MHz Arm® Cortex-A55®,能讓 FPGA 處理複雜的軟體堆疊,如人機介面 (HMI) 或網路堆疊。

可編程結構具有 AI Tensor 模塊,能提供高達每秒 2.8 次 INT8 Tera 運算 (TOPS)。這些模塊可支援多種運算格式,包括 FP16、FP19、FP32 和 BFLOAT16,且針對 AI 工作負載的高效執行進行最佳化。此外也含也精度可調 DSP 模塊,能針對一般用途訊號處理提供高達 180 每秒十億次浮點運算 (GFLOPS) 效能。

圖 1:Agilex 3 以其高效能 DSP 和 AI Tensor 模塊而著稱。(圖片來源:Altera)

圖 1:Agilex 3 以其高效能 DSP 和 AI Tensor 模塊而著稱。(圖片來源:Altera)

高速連接是 Agilex 3 架構的另一項優勢。收發器可支援高達 12.5 Gb/s 的數據傳輸率,並含有硬化 I/O 模塊,可用於 PCIe 3.0、10 Gb 乙太網路 (GbE) 和 LPDDR4 記憶體介面。具有 IEEE 1588 精確時間同步的支援,可進一步增強對即時工業網路的適用性。

A3CZ135BB18AE7S 裝置可說明此系列的功能。其中含有 135K LE、184 個 DSP 模塊,並提供 2.54 TOPS。

對複雜系統的進階整合

對於工業自動化和中階視覺系統等應用,原始運算能力相對於支援複雜配置 (有大量客製化邏輯與 I/O) 的能力來說,重要性較低。Cyclone V FPGA 非常適合這些場景,可提供高達 300K LE 和眾多高速介面。如同 Agilex 3,這些晶片僅提供純 FPGA 和 SoC 款式。在此例中,SoC 裝置整合了雙核心 ARM Cortex-A9。

這些晶片中的可編程結構含有精度可調 DSP 模塊,可支援三重 9 × 9 和雙重 18 × 18 定點乘法,以及 27 × 27 定點或浮點乘法。這些模塊可用於進階訊號處理和 AI。

豐富的 I/O 組合可支援多種電壓位準和介面類型。硬化的邏輯模塊可促成進階的高速連接,包括 PCIe 2.0、DDR3控制器和運作速度高達 6.144 Gb/s 的收發器。

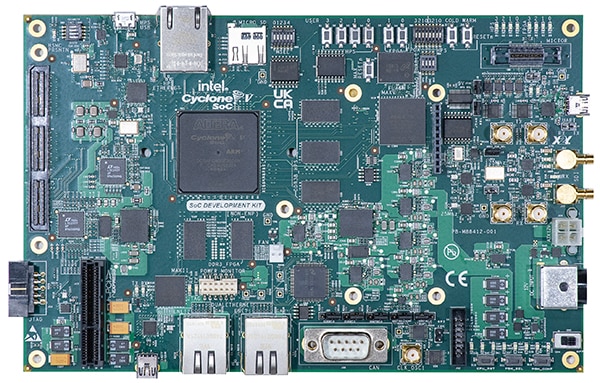

開發人員可以使用 DK-DEV-5CSXC6N-B 開發套件來評估 Cyclone V SoC 系列 (圖 2)。此套件可針對複雜、高吞吐量的系統進行快速原型開發。

圖 2:DK-DEV-5CSXC6N-B Cyclone V 開發套件可支援高效能的原型開發。(圖片來源:Altera)

圖 2:DK-DEV-5CSXC6N-B Cyclone V 開發套件可支援高效能的原型開發。(圖片來源:Altera)

此套件含有幾個值得注意的特點:

- 雙乙太網路埠、一個 PCIe x4 連接器、一個高速夾層卡 (HSMC) 且各方向皆有 16 個 LVDS 通道

- USB 2.0 OTG、CAN、UART 和兩行文字的 LCD 介面

- FPGA 和 HPS 端各有 1 GB DDR3 SDRAM、128 MB 四通道 SPI 快閃記憶體和 4 GB microSD 卡

此板具有 5CSXFC5D6F31C8N 裝置,其中含有一個速度為 600 MHz 的雙核心 Arm Cortex-A9 處理器,搭載 85K LE、87 個 DSP 模塊和 288 個 I/O 引腳,採用 31 mm × 31 mm 896-FBGA 封裝。

採用緊湊封裝的高能效可配置邏輯

許多應用在空間和功耗層面上面臨嚴格限制。範例包括感測器介面、電源定序和週邊控制。在這些情況下,MAX 10 系列等 FPGA 就可提供有效的解決方案。MAX 10 裝置可提供 2K 至 50K LE 的配置,封裝可小至 3 mm × 3 mm。

主要特點包括多達兩個整合式 12 位元 ADC、一個 DDR3 記憶體介面,以及支援 18×18 和雙重 9×9 定點模式的乘法器模塊。晶片上快閃記憶體可支援支援雙映像儲存區,能讓 FPGA 在沒有外部儲存裝置的情況下進行自我配置。

節能功能是 MAX 10 系列最獨特的屬性之一。內建睡眠模式可將動態功耗降低最多 95%。得益於晶片上快閃記憶體,此裝置還可完全關斷,然後在 10 毫秒 (ms) 內恢復運作。

單一電源選項可進一步簡化電力傳輸。因此 MAX 10 裝置特別適合用在監控工作,因為電源域可能要比系統其餘區塊更快上線。

若開發人員對 MAX 10 感興趣,可以使用 EK-10M08E144 MAX 10 FPGA 評估板來評估此系列產品 (圖 3)。此板件可透過 Arduino UNO R3 連接器和測試點來存取外部訊號,且在佈局上可支援 ADC 效能和整體電源行為的測量。

圖 3:EK-10M08E144 MAX 10 FPGA 評估板可輕鬆存取關鍵 I/O。(圖片來源:Altera)

圖 3:EK-10M08E144 MAX 10 FPGA 評估板可輕鬆存取關鍵 I/O。(圖片來源:Altera)

此板件採用 10M08SAE144C8G 裝置,其中含有 8K LE 和一個 ADC,並採用 144 引腳 LQFP 封裝。除了內建硬體資源外,此 FPGA 還支援 RISC-V 架構的 Nios V 軟處理器,因此設計人員無需外部微控制器單元 (MCU) 即可實作輕量級控制功能。

中階應用的平衡效能

某些應用需要的邏輯與 I/O 容量比入門級 FPGA 能提供的更多。範例包括感測器融合、運動控制和晶片對晶片橋接。Cyclone 10 LP FPGA 可在裝置上提供高達 120K 的 LE 和 525 個 I/O 引腳,藉此因應這些要求,更經過最佳化,可在成本敏感型應用中達到平衡的功耗和頻寬。

如同 MAX 10 一樣,此系列含有適用於濾波、控制迴路和基本 AI 推論等工作負載的 DSP 模塊。但與 MAX 10不同的是,Cyclone 10 LP 裝置納入真正的 LVDS 收發器和晶片上端子 (OCT),可支援高速數位介面。

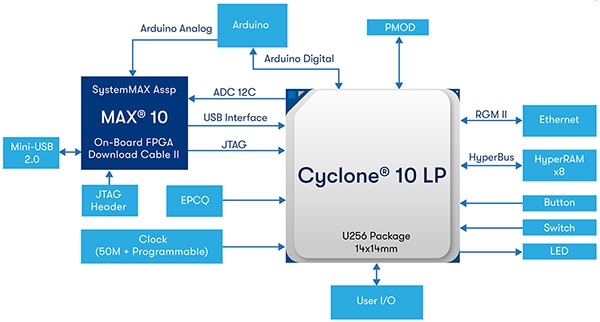

若開發人員對 Cyclone 10 LP 感興趣,可以使用 EK-10CL025U256 Cyclone 10 評估套件來評估此系列 (圖 4)。此板件提供 Arduino UNO R3 和 Digilent Pmod 連接器,可輕易進行擴充。其他特點包括 GbE、USB 2.0、128 Mb SDRAM 和 64 Mb 快閃記憶體。

圖 4:EK-10CL025U256 Cyclone 10 評估套件可支援輕易進行週邊擴充。(圖片來源:Altera)

圖 4:EK-10CL025U256 Cyclone 10 評估套件可支援輕易進行週邊擴充。(圖片來源:Altera)

此板採用 10CL025YU256C8G 裝置,其中含有 25K LE、66 個 DSP 模塊和 150 個 I/O 引腳,並採用 14 mm × 14 mm 封裝。如同 MAX 10 一樣,Cyclone 10 LP 系列也支援 Nios V 軟處理器。

結論

如今,設計人員在嵌入式系統中實作客製化邏輯時,可享有比以往更大的靈活性。高效能應用將可從具有整合式 AI 加速器的 FPGA 受益。低功率設計可獲得具有睡眠模式之裝置帶來的優勢。I/O 密集型系統可以利用具有大量引腳數和高速介面的晶片。重要的是,這些功能都可以透過容易使用的套件,在資源受限且限制嚴格的嵌入式系統中實現。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。