如何使用適用於安全與連線硬式即時系統的 FPGA SoC

資料提供者:DigiKey 北美編輯群

2023-02-16

對於設計人員而言,現場可編程閘陣列 (FPGA)、支援 Linux 的 RISC-V 微控制器單元 (MCU) 子系統、進階記憶體架構以及高效能通訊介面為重要工具。對於安全連線系統、安全關鍵系統,以及諸如人工智慧 (AI) 和機器學習 (ML) 等各種硬式即時確定性系統的設計人員而言尤其如此。

不過,將這些各式各樣的元件整合至安全、連線且具確定性的系統,可能會是既困難又耗時的作業,這是因為要針對各種系統元件佈置高速互連。設計人員必須納入記憶體管理單元、記憶體保護單元、安全啟動功能,以及用於高速連線的 Gigabit 級收發器。設計工作需要動態與靜態的電源管理,以及湧入電流控制。某些設計需要在超過 0°C 至 +100°C 接面溫度 (TJ) 的延伸商業級溫度範圍下運作,而工業環境中的系統必須在 -40°C 至 +100°C TJ 的溫度範圍下運作。

為因應這些層出不窮的挑戰,設計人員可選擇 FPGA 系統單晶片 (SoC) 元件,其整合低功耗、熱效率和國防級安全性,適用於智慧、連線和確定性系統。

本文會探討此類 FPGA SoC 的架構,以及其如何支援有效設計連線與確定性系統。接著簡要說明 EEMBC CoreMark-Pro 處理能力與功耗基準測試的比較結果,以及檢視代表性 FPGA SoC 的基準測試效能。本文著眼於探討如何將安全性納入這些 FPGA SoCs,並詳述 Microchip Technology 的經典 FPGA SoC 以及加速設計流程的開發平台。最後再簡要列出可用於實作各種通訊介面,以及全球導航衛星系統 (GNSS) 定位功能的 MikroElektronika 擴充板。

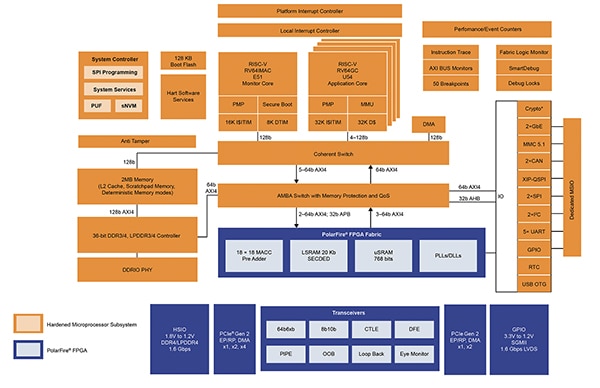

SoC 是採用 FPGA 結構所打造

此 SoC 的「晶片」為 FPGA 結構,其包含的系統元件從 FPGA 乃至以硬式 FPGA 邏輯建構而成的 RISC-V MCU 子系統。MCU 子系統包含四核心 RISC-V MCU 叢集、一個 RISC-V 監測核心、一個系統控制器,以及一個確定性等級 2 (L2) 的記憶體子系統。這些 SoC 中的 FPGA 包含最多 460 K 個邏輯元件、每秒最高 12.7 Gbit (Gbps) 收發器,以及其他輸入/輸出 (I/O) 區塊,包括一般用途 I/O (GPIO) 與快捷周邊組件互連介面 (PCIe) 2。整體架構專為可靠性所設計,包含所有記憶體的單一錯誤修正與雙錯誤偵測 (SECDED)、差分能量分析 (DPA)、實體記憶體保護,以及 128 Kbit 快閃開機記憶體 (圖 1)。

圖 1:此 FPGA SoC 中包括 RISC-V 子系統在內的所有元件,均實作於 FPGA 結構。(圖片來源:Microchip Technology)

圖 1:此 FPGA SoC 中包括 RISC-V 子系統在內的所有元件,均實作於 FPGA 結構。(圖片來源:Microchip Technology)

Microchip 提供其採用第三方工具與設計資源的 Mi-V (發音為「my five」) 生態系統,支援 RISC-V 系統實作。其專為加速 RISC-V 指令集架構 (ISA) 在硬式 RISC-V 核心與 RISC-V 軟核心中的採用。Mi-V 生態系統元件可存取以下項目:

- 智慧財產 (IP) 授權

- 硬體

- 作業系統與中介軟體

- 除錯器、編譯器和設計服務

FPGA SoC 中的硬式 RISC-V MCU 包含數種除錯功能,例如被動執行時間可設定進階延伸介面 (AXI) 與指令追蹤。AXI 可讓設計人員監測目前從各種記憶體寫入或讀取的資料,並瞭解寫入或讀取資料的時間。

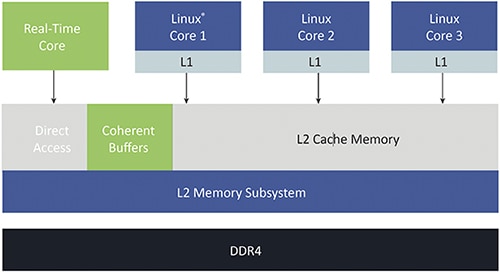

RISC-V MCU 子系統採用五階段單一分發循序管線,不會遭到 Spectre 或 Meltdown 攻擊而飽受失序架構困擾。所有五個 MCU 皆與記憶體子系統同調,支援混用確定性非對稱多處理 (AMP) 模式即時系統與 Linux。RISC-V 子系統包含的功能 (圖 2):

- 執行 Linux 與硬式即時作業

- 將 L1 與 L2 設定為確定性記憶體

- DDR4 記憶體子系統

- 停用/啟用分支預測器

- 循序管線作業

圖 2:包含數種處理器與記憶體元件的 RISC-V 子系統。(圖片來源:Microchip Technology)

圖 2:包含數種處理器與記憶體元件的 RISC-V 子系統。(圖片來源:Microchip Technology)

提供更豐富的處理功能並減少能源消耗

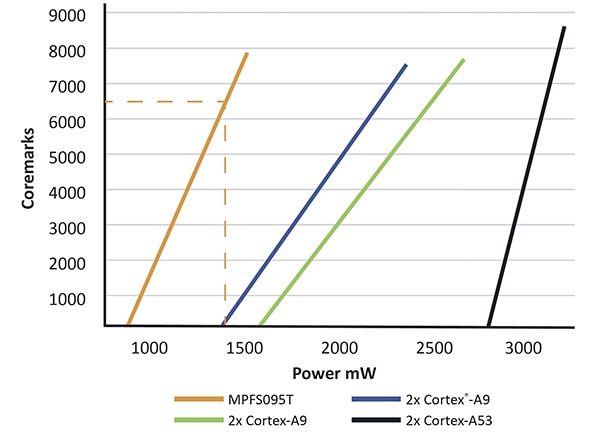

這些 FPGA SoC 除了本身的系統運作優勢 (包括支援硬式、即時處理) 外,還具備優異的能效表現。EEMBC CoreMark-PRO 基準測試是一項用於比較嵌入式系統 MCU 效率與效能的業界標準。其專為硬體效能基準測試以及取代 Dhrystone 基準測試所設計。

CoreMark-PRO 工作負載包含各種效能特性、指令級同步作業,以及基於四個浮點工作負載與五個常用整數工作負載的記憶體運用。浮點工作負載包含衍生自 LINPACK 的線性代數常式、快速傅立葉轉換、適用於模式評估的神經網路演算法,以及加強版的 Livermore 迴路基準測試。JPEG 壓縮、XML 解析器、ZIP 壓縮以及 256 位元安全雜湊演算法 (SHA-256) 構成了整數工作負載的基礎。

這類 SoC FPGA 的 MPFSO95T 型號 (例如 MPFS095TL-FCSG536E) 在 1.3 W 下效能可高達 6,500 Coremark (圖 3)。

圖 3:MPFS095T FPGA SoC (橘色線路) 在 1.3 W 下效能可高達 6500 Coremark。(圖片來源:Microchip Technology)

圖 3:MPFS095T FPGA SoC (橘色線路) 在 1.3 W 下效能可高達 6500 Coremark。(圖片來源:Microchip Technology)

安全性考量

這些 FPGA SoC 的安全關鍵與硬式即時應用除了具備優異的能效與強大處理功能外,還需要具備強大的安全性。這些 FPGA SoC 的基本安全性功能包括差分能量分析 (DPA) 防護位元流程式設計、真實亂數產生器 (TRNG),以及物理反複製技術 (PUF)。此外還包括標準與使用者定義的安全啟動、提供機器權限狀態相關記憶體存取限制的實體記憶體保護 (包括機器、監督者或使用者模式),以及 Meltdown 與 Spectre 攻擊耐受能力。

安全性的起點在於安全的供應鏈管理,包括在晶圓測試與封裝期間使用硬體安全性模組 (HSM)。每個 FPGA SoC 皆內嵌使用經數位簽署的 768 位元組 x.509 FPGA 憑證,為供應鏈提供多一重的保障。

這些 FPGA SoC 包含眾多的晶片上篡改偵測器,確保安全可靠的運作。若偵測到篡改行為,則會發出篡改旗標讓系統得以採取必要回應。一些可用的篡改偵測器包括:

- 電壓監測器

- 溫度感測器

- 時脈突波與時脈頻率偵測器

- JTAG 主動偵測器

- 網狀主動偵測器

採用 256 位元先進加密標準 (AES-256) 對稱區塊密碼關聯功率攻擊 (CPA) 安全措施進一步確保安全性,整合加密摘要功能確保資料完整性,針對 FPGA 結構與所有晶片上記憶體的金鑰儲存與歸零功能整合 PUF。

FPGA SoC 範例

Microchip Technology 將這些功能與技術,整合至具有多種速度等級、溫度額定值以及各種封裝尺寸的 PolarFire FPGA SoC,滿足設計人員對於各種 25 K 至 460 K 邏輯元件解決方案的需求。提供四種溫度等級 (額定值皆為 TJ)、0°C 至 +100°C 延伸商業級溫度範圍、-40°C 至 +100°C 工業級溫度範圍、-40°C 至 +125°C 車用級溫度範圍,以及 -55°C 至 +125°C 軍事級溫度範圍。

設計人員可選擇標準速度等級元件,或是速度快上 15% 的 -1 速度等級元件。這些 FPGA SoC 可在 1.0 V 下以最低功耗運作,或是以 1.05 V 運作提供更高效能。支援各種封裝尺寸,包括 11 x 11 mm、16 x 16 mm 和 19 x 19 mm。

若應用需要延伸商業級溫度作業、標準速度作業,以及在 19 x 19 mm 封裝尺寸內包含 254 K 邏輯元件,設計人員可使用 MPFS250T-FCVG484EES。針對需要 23 K 邏輯元件的簡易解決方案,設計人員可選擇 MPFS025T-FCVG484E,其同樣具備延伸商業級溫度作業、標準速度等級與 19 x 19 mm 封裝尺寸。配備 254 K 邏輯元件的 MPFS250T-1FCSG536T2 專為高效能車用系統所設計,其工作溫度範圍為 -40 至 125°C,時脈速度快上 15% 的 -1 速度等級,並採用 0.5 mm 間距和 536 焊球的 16 x 16 mm 精巧封裝尺寸 (圖 4)。

圖 4:MPFS250T-1FCSG536T2 車用溫度採用 0.5 mm 間距和 536 焊球的 16 x 16 mm 封裝尺寸。(圖片來源:Microchip Technology)

圖 4:MPFS250T-1FCSG536T2 車用溫度採用 0.5 mm 間距和 536 焊球的 16 x 16 mm 封裝尺寸。(圖片來源:Microchip Technology)

FPGA SoC 開發平台

為了加速 PolarFire FPGA SoC 系統設計工作,Microchip 推出的 MPFS-ICICLE-KIT-ES PolarFire SoC Icicle 套件可探索支援 Linux 的五核心 RISC-V 微處理器子系統,具備低功耗、即時執行的特性。此套件包含評估設計所需的免費 Libero Silver 授權,並支援使用單一語言的程式設計與除錯功能。

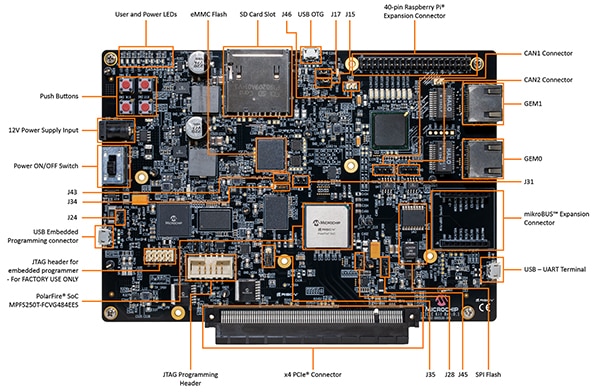

這些 FPGA SoCs 支援 VectorBlox 加速器軟體開發套件 (SDK),其支援低功耗、小型尺寸的 AI/ML 應用。重點在於簡化設計流程,讓設計人員無須先行具備 FPGA 設計經驗。VectorBlox 加速器 SDK 可讓開發人員使用 C/C++ 執行節能神經網路的程式設計工作。Icicle 套件擁有提供完備開發環境的眾多功能,包括可監測各種電源域、PCIe 根連接埠和板載記憶體 (包括 LPDDR4、QSPI 和 eMMC Flash) 以執行 Linux 和 Raspberry Pi 的多軌功率感測器系統,以及適用於眾多有線與無線連接選項的 mikroBUS 擴充連接埠,此外還有諸如 GNSS 定位功能等延伸功能 (圖 5)。

圖 5:此完備的 FPGA SoC 開發環境包括 Raspberry Pi 連接器 (右上方) 與 mikroBUS (右下方) 擴充板。(圖片來源:Microchip Technology)

圖 5:此完備的 FPGA SoC 開發環境包括 Raspberry Pi 連接器 (右上方) 與 mikroBUS (右下方) 擴充板。(圖片來源:Microchip Technology)

擴充板

mikroBUS 擴充板的幾個範例包括:

MIKROE-986:採用序列周邊裝置介面 (SPI) 增加 CAN 匯流排連接能力。

MIKROE-1582:介接 MCU 與 RS-232 匯流排。

MIKROE-989:連接 RS422/485 通訊匯流排。

MIKROE-3144:支援 LTE Cat M1 與 NB1 技術,為 3GPP IoT 元件提供可靠簡易的連接能力。

MIKROE-2670:支援可同時接收 GPS 和 Galileo 星系以及北斗或 GLONASS 的 GNSS 功能,在都市峽谷訊號較弱或訊號受干擾環境時可展現優異的定位準確度。

結論

設計人員可選擇 FPGA SoC 來開發連線、安全關鍵與硬式即時確定性系統。FPGA SoC 提供各式各樣的系統元件,包括 FPGA 結構、配備高效能記憶體、高速通訊介面和眾多安全性功能的 RISC-V MCU 子系統。為協助設計人員開始使用,提供的開發板與環境已納入所有必要元件,包括可用來實作各種通訊與定位功能的擴充板。

推薦閱讀

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。