如何利用自舉方法解決類比高電壓輸送難題

資料提供者:DigiKey 北美編輯群

2019-10-01

對於自動測試設備或精密控制系統而言,要提供它們經常需要的數百伏類比電壓,這無疑是一項絕無僅有的挑戰。傳統的運算放大器無法提供這麼高的輸出電壓擺盪,而離散放大器的替代方案則需要經過高度調校,並會佔用較多的電路板面積。

不過,還有另一個選擇:使用高電壓軌對軌輸出運算放大器和一對可承受高崩潰電壓的 FET,然後進行自舉升壓。

本文將探討現有的高類比電壓問題及常見的解決方法。接著將介紹如何使用 Analog Devices 的高電壓精密放大器,搭載 Microchip Technology 和 Infineon Technologies 的高電壓 MOSFET 進行自舉升壓。

這些元件將用於建立精密的高效能解決方案,在成倍增加放大器標稱訊號範圍的同時,仍能以最小的電路板佔用面積提供更高的效能。

高類比電壓設計選項

有些應用要求的輸出電壓擺盪,高於典型高電壓單晶片運算放大器所能產生的擺盪。使用離散電晶體的放大器設計,是獲得寬電壓擺盪的一種方法。這種設計方法能靈活地針對特定應用客製化放大器。但是,離散電晶體式設計需要更多的零件,也需要設計人員花費更多的時間和心力。另外,在離散設計中,出於元件配對和溫度梯度的原因,也很難達到精度要求。

取代離散高電壓放大器的另一種方法,是高電壓運算放大器模組。這些模組可明顯減輕設計人員的負擔。高電壓模組通常是一種混合模組,可兼顧高電壓和高功率運作。與離散設計相比,這些模組的優勢在於具備出廠指定效能。雖然這些規格能減少設計人員的特徵化活動,但這類混合模組的成本很高。在大多數情況下,高電壓單晶片運算放大器可以滿足設計的大多數效能要求。

但是,如果上述方案不可行,則透過自舉單晶片運算放大器的電源供應器,將其擴展到規格範圍之外,便可將可用運算放大器的選項清單,從幾個解決方案增加至數百種選擇。雖然自舉策略需要更多的心力,但與高電壓模組相比,此解決方案可顯著降低成本。這主要歸因於市場上有各種各樣具備出廠指定效能的單晶片運算放大器。請注意,自舉不會影響放大器的 DC 規格,例如電壓偏移、輸入電壓擺盪,以及輸出電壓擺盪等。

電源供應器自舉技術

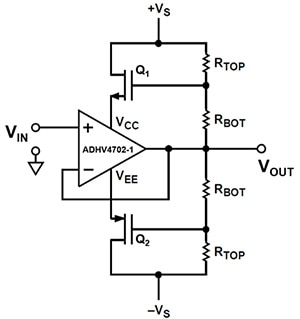

自舉配置可相對於元件的輸出電壓來控制其供應電壓。自舉電路有一對離散電晶體和一個電阻式偏壓網路 (圖 1)。

圖 1:簡易型高電壓隨耦器自舉線路圖,具有固定的 +VS 和 -VS 系統供應電壓。VCC 和 VEE 元件的供應電壓隨輸出電壓 VOUT 而變化。(圖片來源:Bonnie Baker,Analog Devices 提供材料來源)

圖 1:簡易型高電壓隨耦器自舉線路圖,具有固定的 +VS 和 -VS 系統供應電壓。VCC 和 VEE 元件的供應電壓隨輸出電壓 VOUT 而變化。(圖片來源:Bonnie Baker,Analog Devices 提供材料來源)

許多高電壓放大器消除了對自舉電源的需求。例如,圖中所示的 Analog Devices 10 MHz ADHV4702-1BCPZ 是一款足以應付大多數高電壓應用的 ±110 電源供應器。但是,如果系統需要更高的電壓,則自舉方法可輕鬆地成倍增加此電路的工作範圍。

為了執行自舉,Infineon Technologies 的 IRFP4868PBF N 通道 MOSFET 可用作 Q1。此元件具備 300 V 崩潰電壓及最大 70 A 的 ID;Q2 則是 Microchip Technology 的 TP2435N8-G P 通道 MOSFET,此元件具備 350 V 的崩潰電壓。

在圖 1 中,ADHV4702-1 精密放大器的供應電壓範圍為 ±12 V 至 ±110 V。當供應電源為 ±110 V 時,典型輸出電壓範圍為 ±108.5 V。當 ±VS 等於 ±300 V 時,此自舉電路形成放大器效應,輸出擺盪可達 ±120 V 或更高。

此自舉概念又稱為飛軌 (flying rails),會不斷調整放大器的供應電壓,使其相對於放大器的輸出電壓 VOUT 對稱。這樣,輸出即會保持在供應範圍內。在隨耦器自舉型電路中,電阻分壓器 (RBOT 和 RTOP) 會將 VCC 和 VEE 間的差異穩定維持在 ±90 V,同時放大器的輸出範圍為 ±200 V。Spice 模擬說明了這種浮動供應現象 (圖 2)。

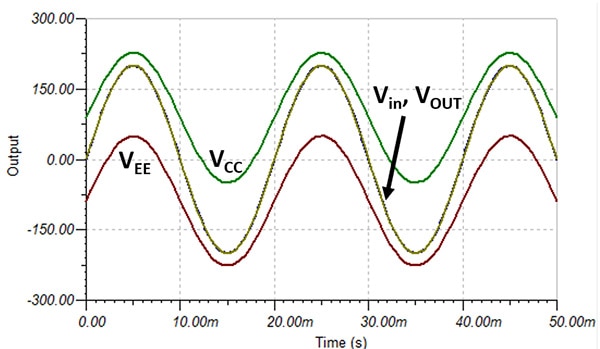

圖 2:Spice 模擬顯示浮動供應現象,其中,放大器電源供應差異值 (VCC 和 VEE 間的差異) 會維持在 ±90 V 左右,同時放大器的輸出範圍為 ±200 V。(圖片來源:Bonnie Baker)

圖 2:Spice 模擬顯示浮動供應現象,其中,放大器電源供應差異值 (VCC 和 VEE 間的差異) 會維持在 ±90 V 左右,同時放大器的輸出範圍為 ±200 V。(圖片來源:Bonnie Baker)

在圖 2 中,VOUT 等於 VIN,RTOP 等於 45 kΩ,而 RBOT 等於 20 kΩ。RTOP 是最靠近外部電源供應 (+VS 和 -VS) 的電阻,而 RBOT 則是最靠近運算放大器輸出 (VOUT) 的電阻。請注意,在圖 2 中,VCC 和 VEE 電壓分別接近 +VS (300 V) 和 -VS (-300 V)。當輸出訊號 (VOUT) 迫使 VCC 和 VEE 等於或大於 VS 或 -VS 時,即會發生電路失真。

自舉可為任何運算放大器提供高訊號能力。但是,放大器的迴轉率會影響此高電壓配置的動態效能。在圖 1 中,運算放大器的迴轉率限制了 VCC 和 VEE 對動態訊號的回應能力。自舉放大器最適合電源供應緩慢變化的低頻和 DC 應用。

自舉設計實作

在設計運算放大器電源供應器的自舉電路時,請遵循以下三個步驟:

- 評估和權衡放大器與 MOSFET 之間的功率耗散

- 確定最大的放大器輸出擺盪並指定放大器供應電壓

- 考量電阻的功率要求

在圖 1 中,功率耗散在運算放大器和 MOSFET 汲源極之間分配。放大器和 FET 的電壓供應處於指定的工作範圍內。用較低的電壓為放大器供電固然是個很吸引人的做法,但這樣做可能會給 MOSFET 帶來壓力。總功率耗散會在放大器和 MOSFET 之間進行分配。

運算放大器最大輸出擺盪範圍 (±VOUT-MAX) 和運算放大器電源供應 (VEE,VCC) 之間的關係,決定了電阻分壓器網路,如方程式 1 所示。

![]() 方程式 1a

方程式 1a

如果運算放大器的標稱供應電壓等於 ±100 V,且最大輸出擺盪範圍等於 ±150 V,則分壓比等於:

![]() 方程式 1b

方程式 1b

此項計算提供一種簡便方法來確定此應用的電阻值。但是,在選擇電阻時,請切記由於涉及到高電壓,這些電阻可能需要耗散可觀的功率。請選擇可將散熱限制在各自額定規格以內的電阻值。

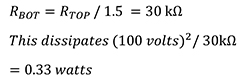

例如,RTOP 達到 150 V,RBOT 達到 100 V。使用額定值為 ½ W 的電阻,透過方程式 2 計算出功率耗散 (V2/R) 限值。

![]() 方程式 2a

方程式 2a

![]() 方程式 2b

方程式 2b

使用 45 kΩ 電阻作為功率耗散限制因子,RBOT 值產生 2.5:1 的分壓比,其靜態功率耗散限值計算如下:

FET 選擇

選擇 MOSFET 時,主要的考量因素就是崩潰電壓。此電壓必須能承受最嚴苛的偏壓條件。當一個 MOSFET 達到 VDS 上限,而另一個 MOSFET 達到 VDS 下限時,輸出即會飽和,進而產生崩潰電壓。例如,最高的絕對 VDS 約為 300 V,即 VOUT-MAX (500 V) 減去放大器的總供應電壓 (VCC – VEE = 200 V)。因此,MOSFET 必須至少能夠承受 300 V。此外,功率耗散必須依 VDS 和工作電流的最嚴苛條件計算。設計人員必須確保指定 MOSFET 在此功率位準下工作。

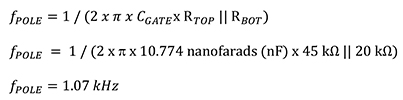

MOSFET 的閘極電容透過偏壓電阻產生低通濾波器,因此,崩潰電壓較高的 MOSFET 往往具有較高的閘極電容。在此電路中,偏壓電阻通常是數十 kΩ 到數百 kΩ。在這些高電阻值下,無需太多的閘極電容就能減慢電路速度。

規格書中的 MOSFET 閘極電容值 (CGATE) 及 RTOP 和 RBOT 的並聯,可決定低通濾波器的極點頻率,如方程式 3 所示:

方程式 3

方程式 3

注意事項

偏壓網路的頻率響應必須比輸入和輸出訊號快十倍。如果偏壓網路減慢了電路速度,則放大器的輸出可能會超出其供應。輸入還可能會因放大器電軌外部的瞬間偏移而受損,而輸出則可能會因瞬間飽和或迴轉限制而失真。這些狀況可能會造成負回饋損失,以及不可預測的暫態行為,同時還可能因相位反轉而發生閂鎖。

效能

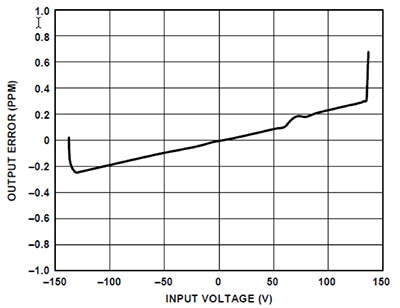

電源供應器自舉電路中的放大器,可配置為提供更高的非反相增益。與其他任何運算放大器增益級一樣,此自舉運算放大器配置的工作方式並無二致。您必須使用非反相配置。由於採用 DC 線性測量,結果由放大器的特徵所主導 (圖 3)。放大器被配置為增益為 20,電源供應範圍為 ±140 V。

圖 3:本圖顯示在增益為 20 且供應電壓為 ±140 V 的情況下,增益誤差與輸入電壓的關係。(圖片來源:Analog Devices)

圖 3:本圖顯示在增益為 20 且供應電壓為 ±140 V 的情況下,增益誤差與輸入電壓的關係。(圖片來源:Analog Devices)

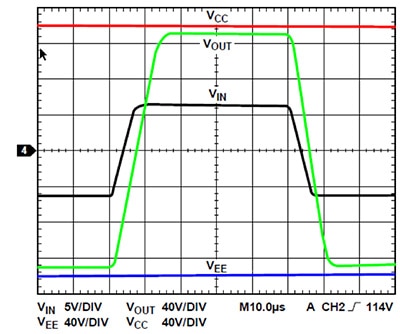

此運算放大器的輸出具備有限的迴轉率,其電源供應取決於輸出。在運算放大器的輸入端,階梯函數可能會超出運算放大器的供應範圍 (圖 4)。

圖 4:增益為 20 且電源供應範圍為 ±140 V 時的迴轉率。在運算放大器的輸入端,階梯函數可能會超出運算放大器的供應範圍,造成閂鎖狀況。在輸入節點上放置低通濾波器可避免此問題。(圖片來源:Analog Devices)

圖 4:增益為 20 且電源供應範圍為 ±140 V 時的迴轉率。在運算放大器的輸入端,階梯函數可能會超出運算放大器的供應範圍,造成閂鎖狀況。在輸入節點上放置低通濾波器可避免此問題。(圖片來源:Analog Devices)

在圖 4 中,ADHV4702-1 的指定迴轉率為 74 V/ms。為避免發生閂鎖狀況,設計人員需要在訊號輸入節點 (VIN) 上使用低通濾波器。此迴轉限制電路可讓暫態低於或等於運算放大器的迴轉率,可使用方程式 4 計算如下:

![]() 方程式 4

方程式 4

其中,VSTEP 為訊號源的最大階梯大小,SR 為運算放大器的迴轉率。

結論

以低成本及最小電路板佔用面積來驅動高類比電壓的最佳方法,是使用高電壓軌對軌輸出運算放大器和一對可承受高崩潰電壓的電晶體,然後進行自舉升壓。Analog Devices 的 ADHV4702-1 高電壓精密放大器搭載 Infineon 和 Microchip 的高電壓 MOSFET,即可打造出這種精密的高效能解決方案,在成倍增加放大器標稱訊號範圍的同時,仍能提供更高的效能。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。