如何在數位 MEMS 感測器中預防頻疊

2023-09-15

在過去十年多來,在設計以微機電系統 (MEMS) 為基礎的系統時,都偏好使用使用數位 MEMS 感測器,而非類比款式。這個趨勢是基於感測器產品的可用性、功能組合、整合度與成本。在挑選數位 MEMS 感測器時,工程師要進行多項設計決策,例如感測器範圍、雜訊、封裝和電流消耗等。對於加速計等慣性 MEMS 感測器來說,設計人員還要考量感測器的頻寬特性,以免將不想要的訊號頻疊到感測器的訊號鏈中。

本文將探討感測器系統中頻疊的基本原理,以及如何在消除頻疊誤差的幾種方法中取捨。

背景知識

MEMS 加速計1 已經是在多種應用中進行振動感測時的首選解決方案,例如條件式監測 (CBM)、預測性維護 (PDM)、抗噪、生物辨識回饋和許多其他應用。與之前以壓電感測器和類比感測器為基礎建構的解決方案相比,數位加速計具有低功耗、低成本和小封裝尺寸等關鍵優勢。數位 MEMS 加速計的延展性能讓系統設計人員在系統中使用多個加速計,並可在實際發生振動的地點,遠端部署感測器。如此一來,系統就可偵測局部性的慣性運動,發揮頂尖效能,藉此達到即時分析並立即行動。

圖 1:數位加速計的典型應用。(圖片來源:STMicroelectronics)

圖 1:數位加速計的典型應用。(圖片來源:STMicroelectronics)

由於數位加速計在本質上經過完全整合,設計人員必須考量感測器的頻寬和頻率響應。在振動應用中更是如此,因為設計人員必須避免輸入頻率頻疊到感測器輸出。

奈奎斯特定理

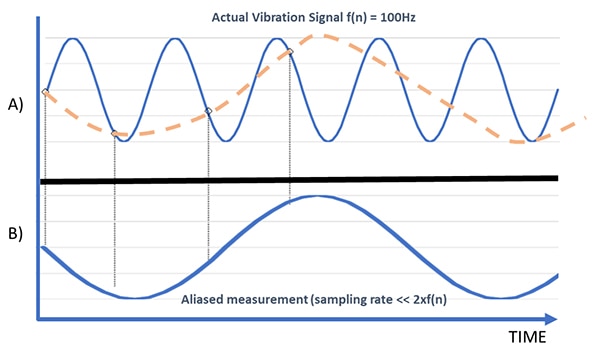

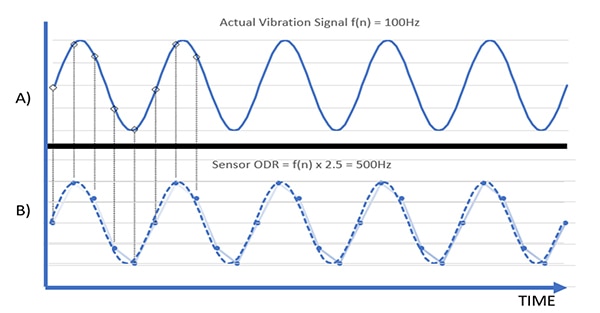

在加速計架構系統中,當感測器取樣速度過慢,無法準確測量輸入訊號時,就會出現頻疊現象。在振動偵測等 MEMS 感測器應用中,由於實際振動訊號中可能不會呈現頻疊訊號,因此頻疊可能會導致災難性故障。

頻疊範例如圖 2 所示。取樣率低於振動頻率的 2 倍,會在結果中引進頻疊波形。頻疊訊號並未呈現在實際振動中,這是因為輸入振動的取樣不足而產生假影。頻疊訊號來自於在振動上坡和下坡時所取得的 ADC 樣本,該樣本會經過內插,以呈現與實際振動不同的波形。

圖 2:取樣率低而導致的頻疊結果。(圖片來源:STMicroelectronics)

圖 2:取樣率低而導致的頻疊結果。(圖片來源:STMicroelectronics)

數位訊號處理有個公認的取樣率規則,稱為奈奎斯特定理,如方程式 1 所示。此規則規定,可以透過系統中最高頻率 (F) 至少兩倍的取樣頻率 f(samping) 來避免頻疊。

Eq.(1)

Eq.(1)

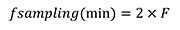

例如,100 Hz 的振動需要至少在 >200 Hz 的條件下取樣,以便偵測振動訊號而不會產生頻疊。如圖 3 所示,用比最小頻率快上許多的速率取樣時,就可正確擷取實際的振動訊號。超取樣是一種數位濾波方法,但要注意的是,有些不想要的訊號仍有可能外流到訊號鏈中。

圖 3:使用超取樣避免感測器輸出出現頻疊。(圖片來源:STMicroelectronics)

圖 3:使用超取樣避免感測器輸出出現頻疊。(圖片來源:STMicroelectronics)

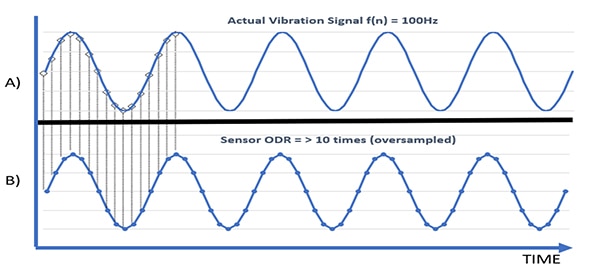

使用超取樣方法來減少頻疊有個缺點,就是取樣率高,功耗會明顯提高。典型感測器的取樣率或輸出數據率(ODR) 與功耗直接相關,如圖 4 所示。在取樣率較高的情況下,電流消耗會大幅增加。

圖 4:加速計的電流消耗。(圖片來源:STMicroelectronics)

圖 4:加速計的電流消耗。(圖片來源:STMicroelectronics)

如圖 5 所示,可將取樣率降低至接近奈奎斯特頻率,就可降低功耗。在此,取樣率已降低至 500 Hz,約為目標頻率的 2.5 倍。在 500 Hz 下,實際振動的波形仍可透過內插重新建構,比起在目標頻率 10 倍下取樣,電流消耗量有所降低。

圖 5:將取樣率降低至振動頻率的 2.5 倍。(圖片來源:STMicroelectronics)

圖 5:將取樣率降低至振動頻率的 2.5 倍。(圖片來源:STMicroelectronics)

這比上一個範例有所改進,但仍有一個風險,就是輸入上的某些意外高頻內容,可能會頻疊到感測器訊號鏈中。

取樣率說明

在使用加速計時,最常見的問題之一就是如何挑選適合特定應用的取樣率。取樣率的選擇通常是在效能和電池續航力之間權衡。高取樣率會導致資料檔案龐大而難以操控、阻礙通訊並降低能效。另一方面,取樣率過低可能會讓系統頻疊,如之前的範例所示。

幸好,已經有準則可協助挑選最低的取樣率。在功耗不受限制的應用中,取樣率可以設定為事件頻率的許多倍。但即使取樣率較高,由於振動資料和雜訊的類比本質,數位濾波也有可能出現頻疊。

抗頻疊濾波器 (AAF)

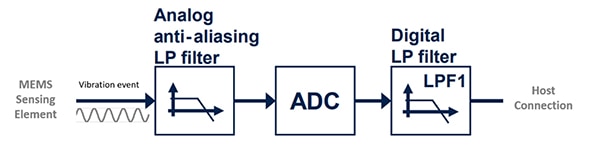

除了增加功耗外,使用數位超取樣還有其他缺點。振動並非總是完美的正弦波,但通常有高頻成分,如諧波和雜訊。為了減少這些影響,可以在訊號取樣之前,利用低通濾波器來去除任何無關的高頻。這種低通濾波器也稱為抗頻疊濾波器,某些款式的 MEMS 加速計有嵌入此元件。

圖 6:類比抗頻疊 (低通) 濾波器。(圖片來源:STMicroelectronics)

圖 6:類比抗頻疊 (低通) 濾波器。(圖片來源:STMicroelectronics)

抗頻疊濾波器的工作原理基本上與低通濾波器相同。AAF 會先行去除高頻內容 ,然後再由 ADC 取樣。AAF 必須位於 ADC 之前,以便此作法生效。如果 AAF 放在 ADC 之後,就會成為數位濾波器,則會有前面所述的數位濾波器和超取樣缺點。

含嵌入式 AAF 的加速計系列

LIS2DU12 屬於三軸數位加速計系列成員,在類比前端具有嵌入式抗頻疊濾波器。LIS2DU 提供三個款式,除了基本設計外,各具有獨特的功能組合。三款裝置皆採用 STMicroelectronics 的 2 mm x 2 mm 12 引線 MEMS 加速計封裝。每個裝置都採用相同的超低功耗架構,而且抗頻疊濾波器讓電流消耗量位居市場上最低水準。以下重點介紹此系列的比較。

LIS2DU12:超低功率加速計,搭載抗頻疊和運動偵測功能

LIS2DUX12:超低功率加速計,搭載抗頻疊和嵌入式機器學習核心 (MLC)。

LIS2DUXS12:超低功率加速計,搭載 Qvar、MLC 和抗頻疊功能

在 LIS2DU 系列中,低通濾波器會在 ADC 之前的訊號鏈中實例化,以在數位轉換之前消除雜訊。

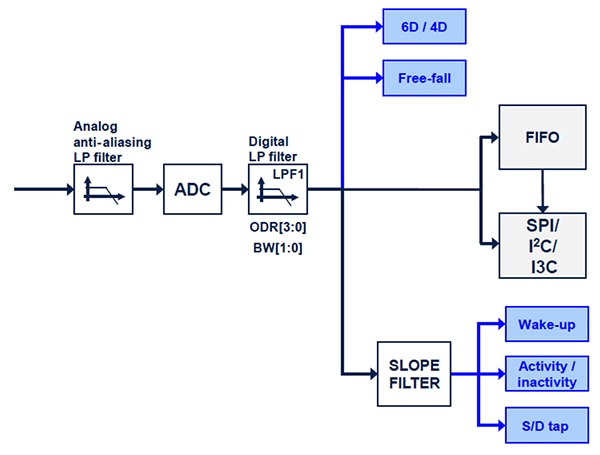

除了添加關鍵的抗頻疊濾波器之外,LIS2DU12 還包含多項進階數位功能。這些功能可實施一些常用的功能,如自由落下、傾斜、點擊偵測、方向和喚醒等,用意是減輕主要微控制器的負載。LIS2DUX12 還包含一個嵌入式機器學習核心 (MLC),可執行更高階的功能,並針對特定應用進行設計開發。

圖7:LIS2DUX12 加速計濾波鏈。(圖片來源:STMicroelectronics)

圖7:LIS2DUX12 加速計濾波鏈。(圖片來源:STMicroelectronics)

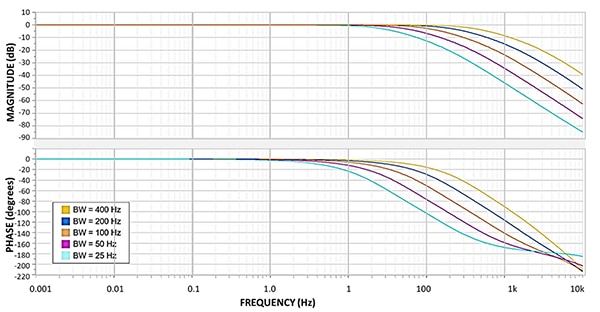

LIS2DU12 類比抗頻疊濾波器的頻率響應如圖 8 所示。以下每條曲線的 25 Hz 至 400 Hz 頻率值是指濾波鏈的頻寬值。

圖 8:LIS2DU12 類比抗頻疊 (低通) 濾波器。(圖片來源:STMicroelectronics)

圖 8:LIS2DU12 類比抗頻疊 (低通) 濾波器。(圖片來源:STMicroelectronics)

最終結果是,LIS2DU12 系列加速計可在大幅降低的電流下運作,同時達到與上一代加速計相同的精密度。除了三個款式中皆有添加的抗頻疊濾波器之外,LIS2DUX12 和 LIS2DUXS12 皆是 STMicroelectronics 率先納入嵌入式 MLC 的消費型 MEMS 裝置。

結論

頻疊是引發系統故障的重大錯誤起因之一。為了減輕頻疊的影響,設計人員首先必須瞭解系統,並預測感測鏈中所有元件的頻率內容。奈奎斯特定理針對受測的最高頻率有規定最低的取樣率。

超取樣可以減少頻疊的影響,但代價是功耗會較高。在許多應用中,預防頻疊的最佳方法就是在 ADC 將樣本轉換成數位域之前,使用抗頻疊濾波器去除不要的頻率。

考量幾個準則後,設計人員就可針對指定應用,挑選適當的取樣和濾波技術。

參考

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。