如何將切換式電源供應器中的寄生效應降至最低

資料提供者:DigiKey 北美編輯群

2024-01-31

切換式電源供應器因其效率和靈活性而廣受歡迎。將之擴展到新的應用領域時,會有新的挑戰。最值得注意的是,其高頻切換可能會對系統的其餘部分產生電磁干擾 (EMI)。此外,導致 EMI 的相同因素也會降低效率,削弱切換式電源供應器的主要優勢。

設計人員為了避免這些問題,在配置「熱迴路」(電源供應器電路中進行快速切換的部分) 時必須更佳謹慎。須將等效串聯電阻 (ESR) 和等效串聯電感 (ESL) 引起的熱迴路寄生損耗降至最低。可藉由選擇高度整合的電源供應器組件和仔細的印刷電路板佈局達成。

本文介紹熱迴路和寄生損耗的來源;包括耦合電容、功率場效電晶體 (FET) 和印刷電路板過孔。接著以 Analog Devices 高度整合式電源轉換器為例,並介紹各種印刷電路板佈局及其對寄生參數的影響。最後提出降低 ESR 和 ESL 的實用技巧。

切換式電源供應器熱迴路基礎知識

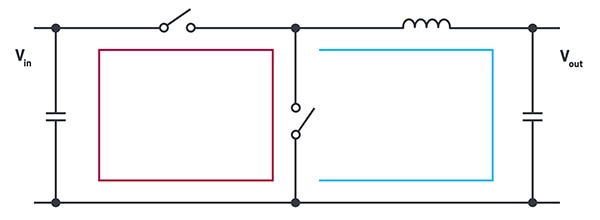

任何涉及快速切換電流的電源供應器設計,例如升壓、升降壓、返馳式轉換器,都會有在高頻切換的電流產生的熱迴路。這個概念由簡化的降壓轉換器來說明 (圖 1)。左邊的迴路 (紅色) 包含所有切換元件;電路產生的高頻電流涵蓋其中,形成熱迴路。

圖 1:簡化的降壓轉換器說明熱迴路的原理,以紅色標明。(圖片來源:Analog Devices)

圖 1:簡化的降壓轉換器說明熱迴路的原理,以紅色標明。(圖片來源:Analog Devices)

「熱」來自於電路在該區域的大量能量轉換和切換活動,通常伴隨著熱生成。這些熱迴路若正確佈局和設計,可將 EMI 降至最低,確保電源供應器能高效率運作。

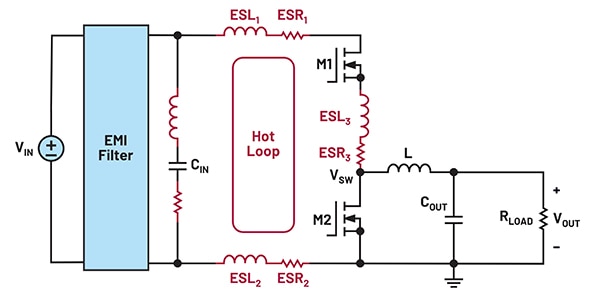

圖 2 是更真實的電路,展示 DC-DC 同步降壓轉換器。此熱迴路的實體組件 (黑色) 為輸入電容 (CIN) 和切換 MOSFET M1 和 M2。

圖 2:現實世界的熱迴路不可避免地包含寄生參數,以紅色顯示。(圖片來源:Analog Devices)

圖 2:現實世界的熱迴路不可避免地包含寄生參數,以紅色顯示。(圖片來源:Analog Devices)

熱迴路中的寄生參數標示為紅色。ESL 通常在納亨 (nH) 範圍內,而 ESR 在毫歐 (mΩ) 範圍內。高頻切換會導致 ESL 內產生振鈴,進而造成 EMI。ESL 中儲存的能量隨後由 ESR 耗散,導致功率損耗。

整合組件將寄生參數降至最低

這些寄生阻抗 (ESR、ESL) 出現在組件內部,並沿著熱迴路印刷電路板走線。為了最大程度減少這些參數,設計人員必須仔細選擇組件並最佳化印刷電路板佈局。

使用整合組件可達到這兩個目標。如此可消除連接離散組件所需的印刷電路板走線,同時減少熱迴路的總區域。兩者都有助於降低寄生阻抗。

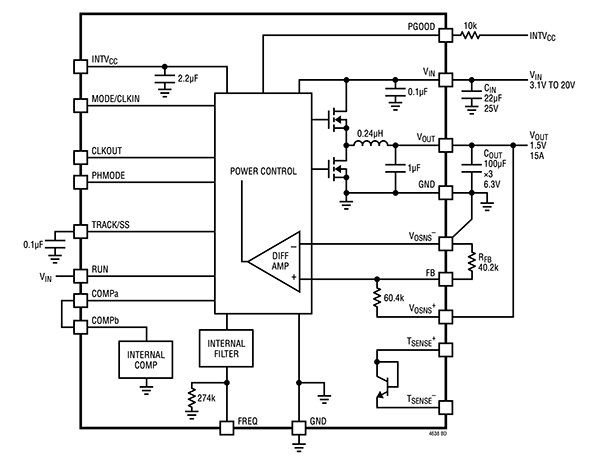

高度整合組件的其中一例為 Analog Devices 的 LTM4638 降壓 µModule 穩壓器。如圖 3 所示,這款 15 A 切換式穩壓器將切換控制器、功率 FET、電感器和支援組件整合在一個 6.25 × 6.25 × 5.02 mm 的小型封裝中。

圖 3:LTM4638 µModule 穩壓器整合降壓轉換器所需的許多組件。(圖片來源:Analog Devices)

圖 3:LTM4638 µModule 穩壓器整合降壓轉換器所需的許多組件。(圖片來源:Analog Devices)

LTM4638 還納入其他幾項可減少寄生損耗的功能,包括:

- 快速暫態響應:可讓穩壓器快速調整輸出電壓,響應負載或輸入的變化。透過快速轉換到次優工作狀態,將寄生損耗及其持續時間和影響降至最低。

- 不連續模式操作:允許電感電流在下一個切換週期開始之前降至零。此模式通常在輕負載條件下使用,透過在部分週期內斷電來減少電感器中的切換和磁芯損耗。

- 輸出電壓追蹤:可讓轉換器輸出追蹤參考輸入電壓。此功能精確控制輸出電壓的斜坡上升和斜坡下降,降低過衝或下衝的可能性,避免寄生損耗加遽。

以元件佈局最小化寄生參數

使用 LTM4638 建構同步降壓轉換器需要分別添加大容量輸入和輸出電容 CIN 和 COUT。這些電容的位置會對寄生參數造成重大影響。

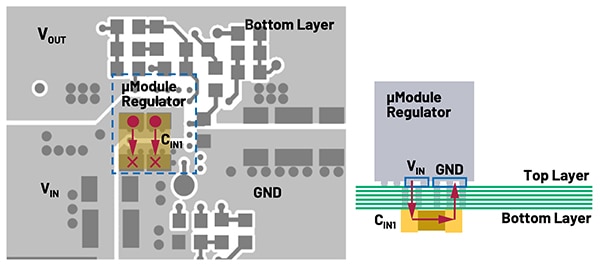

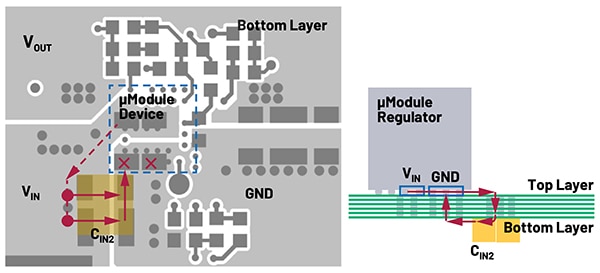

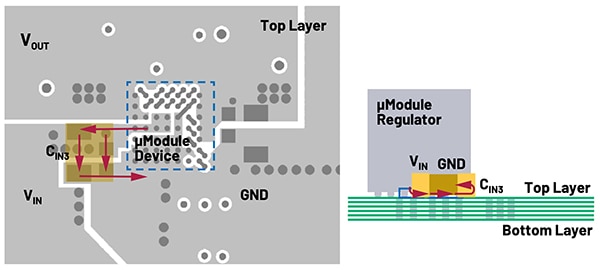

Analog Devices 使用適用於 LTM4638 的 DC2665A-B 評估板進行實驗,說明 CIN 定位造成的影響。 已由 DC2665B-B 取代該板,但適用相同的原則。圖 4 到 6 說明 CIN 的三種不同佈局和對應的熱迴路。垂直熱迴路 1 (圖 4) 和 2 (圖 5) 將 CIN 放置在底層,分別位於穩壓器正下方或側面。水平熱迴路 (圖 6) 將電容放置在頂層。

圖 4:垂直熱迴路 1 底視圖和側視圖。CIN 位於穩壓器正下方,透過過孔連接。(圖片來源:Analog Devices)

圖 4:垂直熱迴路 1 底視圖和側視圖。CIN 位於穩壓器正下方,透過過孔連接。(圖片來源:Analog Devices)

圖 5:垂直迴路 2 底視圖與側視圖。C IN 位於穩壓器下方但在旁邊,需要印刷電路板走線和過孔。(圖片來源:Analog Devices)

圖 5:垂直迴路 2 底視圖與側視圖。C IN 位於穩壓器下方但在旁邊,需要印刷電路板走線和過孔。(圖片來源:Analog Devices)

圖 6:水平熱迴路俯視圖和側視圖。C IN 位於頂層,經由走線連接至穩壓器。(圖片來源:Analog Devices)

圖 6:水平熱迴路俯視圖和側視圖。C IN 位於頂層,經由走線連接至穩壓器。(圖片來源:Analog Devices)

垂直熱迴路 1 具有最短路徑並避免使用印刷電路板走線。因此,預期具有最低的寄生參數。使用 FastHenry 在 600 kHz 和 200 MHz 下分析每個熱迴路,顯示情況確實如此 (圖 7)。

|

圖 7:如預期,最短路徑的寄生阻抗最低。(圖片來源:Analog Devices,經作者修改)

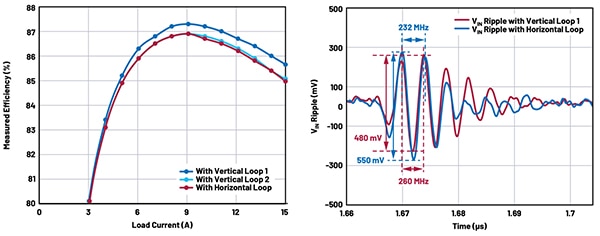

儘管無法直接測量這些寄生參數,但可預測和測試其影響。具體而言,較低的 ESR 應該會帶來較高的效率,而較低的 ESL 應會帶來較低的漣波。實驗驗證證實這些預測:垂直熱迴路 1 在這兩個指標上都表現出更佳效能 (圖 8)。

圖 8:實驗結果證實垂直熱迴路 1 可達到更佳效率和漣波。(圖片來源:Analog Devices)

圖 8:實驗結果證實垂直熱迴路 1 可達到更佳效率和漣波。(圖片來源:Analog Devices)

最小化離散組件的寄生參數

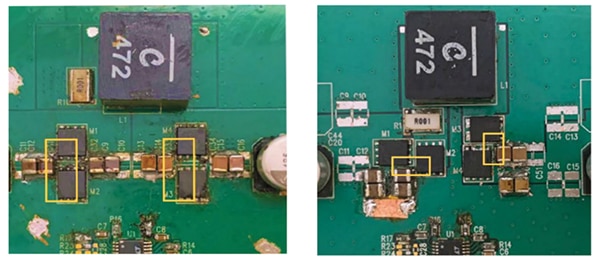

儘管整合組件具有許多優點,但某些切換式電源供應器還是需要離散組件。例如,高功率應用可能超出整合式元件的能力。在這種情況下,離散功率 FET 的置放位置和封裝尺寸會明顯影響熱迴路 ESR 和 ESL。藉由測試以下兩個評估板,可以看出這些影響。這兩個評估板都具有高效能、四個切換式同步升降壓控制器,如圖 9 所示:

- DC2825A 評估板基於 LT8390 升降壓穩壓器。其 MOSFET 並聯放置,即以相同方向放置。

- DC2626A 評估板基於 LT8392 升降壓穩壓器。其兩對 MOSFET,以 90° 角放置。

圖 9:DC2825A (左) 將其 MOSFET 並聯放置,而 DC2626A (右) 以 90° 角放置。(圖片來源:Analog Devices)

圖 9:DC2825A (左) 將其 MOSFET 並聯放置,而 DC2626A (右) 以 90° 角放置。(圖片來源:Analog Devices)

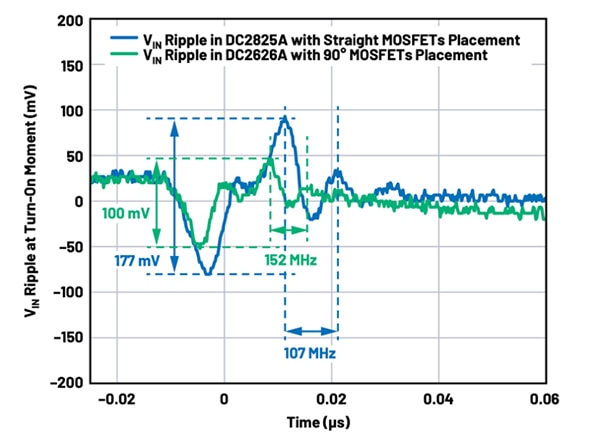

對這兩個板件進行測試,使用相同的 MOSFET 和電容在 10 A 和 300 kHz 的 36 至 12 V 降壓操作。結果顯示,90° 放置具有較低的電壓漣波和較高的諧振頻率,顯示由於熱迴路徑較短,印刷電路板 ESL 較小 (圖 10)。

圖 10:DC2626A 採用 90° MOSFET 佈局,具有較低的漣波和更高的諧振頻率。(圖片來源:Analog Devices)

圖 10:DC2626A 採用 90° MOSFET 佈局,具有較低的漣波和更高的諧振頻率。(圖片來源:Analog Devices)

佈局的其他注意事項

熱迴路中 FormVVia 頂部的配置也會影響迴路 ESR 和 ESL。一般來說,添加更多過孔會降低印刷電路板的寄生阻抗。然而,減少量並不與通孔數量成線性比例。靠近端子焊盤的通孔可大幅降低 ESR 和 ESL。因此,多個過孔應放置在靠近關鍵組件 (CIN 和 µModule 或 MOSFET) 將熱迴路阻抗降至最低。

還有許多其他方法可以提升電氣和熱效能。若要最佳化熱迴路,最佳實踐方式包括:

- 使用大印刷電路板銅區域作為高電流路徑,包括 VIN、VOUT 和接地,以最大程度減少印刷電路板傳導損耗和熱應力。

- 在設備下方放置專用電源接地層。

- 使用多個過孔在頂部和其他電源層之間互連,大規模減少傳導損耗並減少模組熱應力。

- 請勿將過孔直接放置在焊盤上,除非已覆蓋或電鍍。

- 連接到訊號引腳的組件使用單獨的訊號接地銅區域,將訊號接地連接到設備下方的主接地引腳。

- 在訊號引腳上引出測試點進行監控。

- 保持時脈訊號和頻率輸入走線之間分離,盡量減少串音產生雜訊的可能性。

結論

熱迴路中的寄生參數嚴重影響切換式電源供應器的效能。必須將這些參數降至最低,以達到高效率和低 EMI。

達成這些目標的最簡單方法之一是使用整合式穩壓器模組。然而,切換式電源公益慶通常需要使用電容等大容量元件,因此瞭解熱迴路佈局的影響非常重要。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。