如何評估並使用零延遲時脈緩衝器,保護同步數位系統的時序

資料提供者:DigiKey 北美編輯群

2019-07-18

隨著數位系統效能持續提升,設計人員需要更仔細地注意時脈產生電路及時脈分配電路的設計,才能避免時脈分配的計時差異或不確定性。這類問題會降低系統效能、減少時序餘裕,或導致功能性錯誤。為避免時序偏斜方面的問題,設計人員可以使用零延遲時脈緩衝器。

典型的同步數位系統會使用公用時脈確保作業依序進行。該時脈必須分配給所有的順序元件,才能讓系統以所需的速率運作。在分配過程中,通常會使用閉迴路控制來減少時序偏斜。零延遲時脈緩衝器使用鎖相迴路 (PLL) 來保證緩衝時脈輸出與參考時脈輸入保持一致,從而確保近乎完美的時脈計時。

本文將介紹零延遲時脈緩衝器,並使用 Cypress Semiconductor、Integrated Device Technology Inc. (IDT) 及 ON Semiconductor 多家公司的範例解決方案來解釋其工作原理,詳細說明如何控制時脈偏斜。此外,本文還將探討測試方法,以確保這些元件穩定可靠。

時脈偏斜

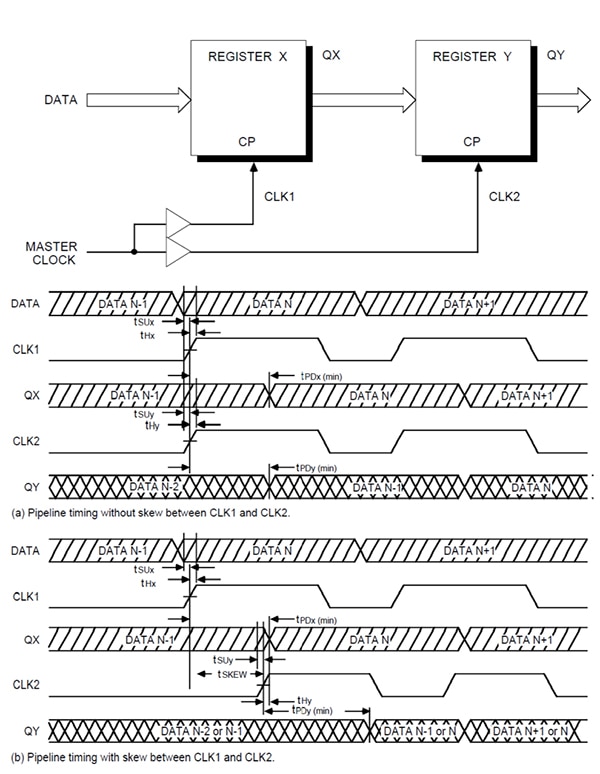

在同步數位系統中,時脈可能會在不同的時間到達電路的不同部份,從而導致時脈偏斜。時脈偏斜會減少時序餘裕,導致系統故障 (圖 1)。

圖 1:時脈時間偏斜如何影響管線式暫存器的簡單範例。偏斜的時脈會違反設置和/或保持要求,導致輸出狀態不確定。(圖片來源:IDT)

圖 1:時脈時間偏斜如何影響管線式暫存器的簡單範例。偏斜的時脈會違反設置和/或保持要求,導致輸出狀態不確定。(圖片來源:IDT)

設想一個包含兩個暫存器的簡易同步系統。資料通過暫存器進行管線傳送,暫存器 X 的輸出 QX 為暫存器 Y 的輸入;而時脈則是經由獨立緩衝器饋送至暫存器並以 CLK1 和 CLK2 標示。如圖 (a) 所示,如果時脈之間沒有偏斜,在符合暫存器設置 (tSUx) 及保持 (tHx) 時間要求時,資料狀態 N 會在暫存器傳播延遲後的第一個時脈緣處,按照時序進入暫存器 X 的輸出 QX。在 CLK2 相同的時脈緣處,暫存器會讀取 QX 的先前狀態 N-1,並在暫存器傳播延遲後將其顯示為輸出 QY。

如圖 (b) 所示,如果 CLK1 和 CLK2 存在時脈偏斜,則發生 CLK2 時,QX 的狀態可能處在轉換中。暫存器 Y 的輸入可能無法滿足暫存器設置或保持時間要求,且輸出可能變得不確定,從而導致錯誤。

為了確保最小的時脈偏斜,設計人員會評估印刷電路板走線的長度,選擇具有類似傳播延遲的緩衝器及其他時脈元件,並平衡多個時脈來源上的負載。雖然這些技巧有所幫助,但通常需要使用零延遲時脈緩衝器,才能良好地控制時脈偏斜。

控制時脈偏斜

造成時脈偏斜的原因可能有許多種。最常見的原因是時脈訊號在具有不同長度互連線的印刷電路板上路由。其他偏斜原因包括:時脈在各種傳播延遲不同的主動元件間傳遞、時脈緩衝器具有不同的負載,或緩衝器存在溫度差異。儘管有些影響可以控制,但設計人員往往使用主動元件透過 PLL 將時脈重新同步到參考時脈。

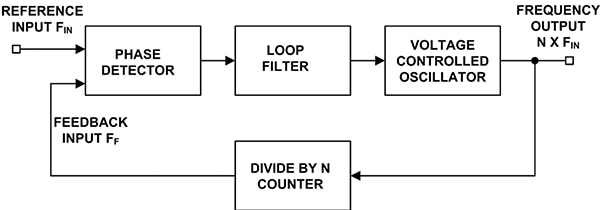

PLL 電路用於控制頻率與相位。PLL 可配置成頻率倍增器、解調器、追蹤產生器或時脈復原電路。這些應用都需要不同的特性,但全都使用同一個基本電路概念,如圖 2 所示。

圖 2:配置為頻率倍增器的 PLL 方塊圖。這其實是一個控制壓控振盪器 (VCO) 相位的回授控制系統。(圖片來源:DigiKey)

圖 2:配置為頻率倍增器的 PLL 方塊圖。這其實是一個控制壓控振盪器 (VCO) 相位的回授控制系統。(圖片來源:DigiKey)

圖 2 顯示一個配置為頻率倍增器的基本 PLL 方塊圖。此電路的運作方式是所有 PLL 的典型運作方式。這其實是一個控制 VCO 相位的回授控制系統。輸入訊號將作為一個輸入施加至相位偵測器。另一個輸入則來自 N 分頻計數器輸出的回授訊號。在正常情況下,兩個訊號的頻率幾乎相同。

相位偵測器的輸出是電壓,大小與兩個輸入的相位差成比例。該訊號將施加至迴路濾波器。迴路濾波器會決定 PLL 的動態特性。過濾後的訊號會控制 VCO。請注意,VCO 輸出的頻率是提供給頻率參考輸入 (FIN) 之輸入的 N 倍。此輸出訊號會透過 N 分頻計數器傳回相位偵測器。

通常,迴路濾波器的設計旨在符合 PLL 應用所要求的特性。如果 PLL 要擷取並追蹤訊號,迴路濾波器的頻寬會大於固定輸入頻率時的預期頻寬。PLL 接受並鎖定的頻率範圍稱為擷取範圍。一旦 PLL 鎖定並追蹤訊號,PLL 將遵循的頻率範圍稱為追蹤範圍。一般來說,追蹤範圍會大於擷取範圍。此外,PLL 迴路濾波器還會確定,訊號頻率可以變化且仍能保持鎖定的速度,即最大迴轉率。迴路濾波器頻寬越窄,相位誤差也就越小。代價則是回應速度變慢,擷取範圍縮小。在時脈應用中使用的 PLL 主要以固定頻率工作。

零延遲時脈緩衝器

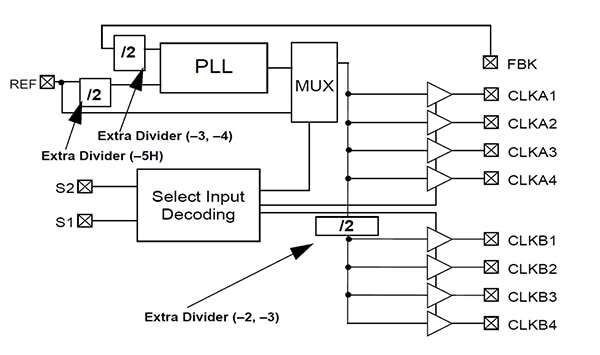

零延遲時脈緩衝器是一款能緩衝時脈訊號的元件,可從一個參考時脈輸入中產生多個時脈輸出。多個緩衝的時脈輸出,相對於參考時脈輸入,僅有很小的延遲或沒有延遲,並且輸出之間的偏斜很小。圖 3 顯示 Cypress Semiconductor 的 CY2308SXC-3T 零延遲緩衝器的簡化方塊圖。

圖 3:CY2308SXC-3T 八輸出零延遲緩衝器使用 PLL 將所有輸出都同步為近乎是零的時間偏斜。(圖片來源:Cypress Semiconductor)

圖 3:CY2308SXC-3T 八輸出零延遲緩衝器使用 PLL 將所有輸出都同步為近乎是零的時間偏斜。(圖片來源:Cypress Semiconductor)

零延遲緩衝器配備積分 PLL,可接受參考輸入 (REF) 以及回授輸入 (FBK),作為其相位偵測器的輸入。回授輸入由使用者選擇的輸出之一驅動。PLL 的內部相位偵測器會調整 VCO 的輸出相位,確保兩個輸入沒有相位差或頻率差。其中一個緩衝的時脈輸出及其負載,將選為回授訊號,經由相位偵測器回授至 PLL。無論該輸出的負載如何變化,PLL 都會動態補償這些輸出負載變化,確保在任何輸出負載下,輸入與驅動回授的輸出之間的延遲都為零。

CY2308 系列有兩組四路輸出,工作頻率為 10 至 133 MHz。輸入到輸出的時間偏斜小於 250 ps,且輸出之間的時脈偏斜小於 200 ps。更改用於回授輸入的輸出端負載電容,即可調整輸入到輸出的時間偏斜。

此產品系列提供多種二分頻器配置。所選元件是「-3」版,此版本有兩個這樣的分頻器,如方塊圖所示。此配置可讓使用者取得兩倍或四倍於參考時脈輸入頻率的輸出。

最常用的零延遲緩衝器會配置五個輸出,並有多家製造商的產品可供選擇。Cypress Semiconductor 的 CY2305SXI-1HT、IDT 的 2305-1DCGI8 以及 ON Semiconductor 的 NB2305AI1HDR2G 都是非常類似的元件。這些元件全都具有五個緩衝時脈輸出、一個 CLKOUT 埠,以及四組時脈輸出。與 CY2308 不同,這些元件的 PLL 回授點固定於單一的 CLKOUT 訊號上。

零延遲緩衝器動態

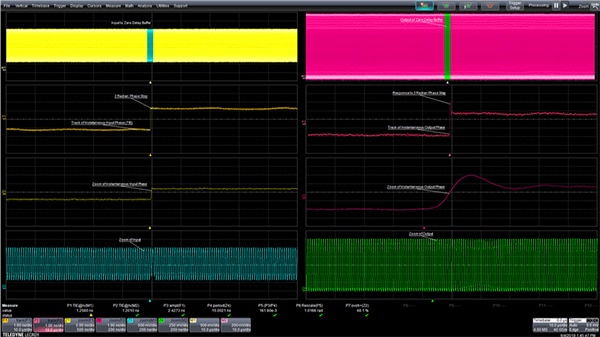

零延遲緩衝器的 PLL 其實是一個回授控制系統。其動態由 PLL 迴路濾波器控制。與所有的控制系統一樣,評估回授迴路響應暫態輸入的動態相當重要。一種方法便是施以步進變化的輸入,以此評估步階響應 (圖 4)。

圖 4:在 66.67 MHz 下使用 1 rad 的相位步進,評估 CY2305 零延遲緩衝器的步階響應。左上角的網格是輸入訊號,右上角的網格是輸出。(圖片來源:DigiKey)

圖 4:在 66.67 MHz 下使用 1 rad 的相位步進,評估 CY2305 零延遲緩衝器的步階響應。左上角的網格是輸入訊號,右上角的網格是輸出。(圖片來源:DigiKey)

輸入訊號為 66.67 MHz 正弦波,且在擷取訊號窗口中心有一個 1 rad 的步進。該波形由任意波形產生器 (AWG) 產生。CY2305 零延遲緩衝器的輸入和輸出均使用示波器擷取,其時基設置為每格 10 µs。

圖 4 左上角的網格為輸入訊號,右上角的網格為輸出。時間間隔誤差 (TIE) 是測得的時脈緣與其理想位置的時間差,並針對每個波形而測量。該誤差其實是以固定時脈速率 (本例為 66.67 MHz) 為參考之訊號的瞬時相位。每個輸入和輸出時脈週期的 TIE 值可繪製成一個波形,稱為 TIE 跡線。輸入的跡線是從左方向下算起的第二個網格。此處,相位的步進很明顯,振幅為 2.4 ns。此值表示在 66.67 MHz 時脈頻率下發生 1 rad 的移相。

從右邊向下算起的第二條跡線是輸出的 TIE 跡線。該輸出跡線顯示出現一些過衝並穩定到一個新的平均值,以匹配輸入變化。從上方算起的第三條跡線顯示左側輸入和右側輸出的橫向擴大縮放跡線。輸入步進的詳細資訊顯示出明確的轉換。

輸出縮放顯示出現一些過衝,然後在大約 500 ns 的週期內迅速穩定到新的平均值。對於如此大的相位步進而言,該步階響應的表現相當出色。此響應快速地穩定下來,且沒有證據顯示會出現不穩定的振盪響應。

兩條底部跡線顯示輸入 (左) 和輸出 (右) 的橫向擴大檢視圖。這個大的相位步進在輸入中清晰可見,但慢的輸出響應在此時間刻度則不是很清晰。

結論

高效能數位系統設計人員依然需要仔細注意時脈產生電路及時脈分配電路的設計,才能避免時脈分配的計時差異或不確定性。這類問題會降低系統效能、減少時序餘裕,或導致功能性錯誤。

如上所述,零延遲緩衝器是一款出色的工具,可主動控制對多個時脈訊號的傳送以及與主時脈訊號的同步。即使感測的輸出有明顯的負載變化,也能提供卓越的追蹤。但如前所示,設計人員需要仔細評估零延遲緩衝器的回授迴路動態,才能確保其滿足應用的要求。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。