FPGA 基礎知識 – 第 4 篇:Xilinx 的 FPGA 入門

資料提供者:DigiKey 北美編輯群

2020-04-01

編者說明:最佳的處理解決方案通常由 RISC、CISC、圖形處理器與 FPGA 等組合方案提供;也可由 FPGA 本身或以處理器硬核為部分結構的 FPGA 提供。然而,有許多設計人員對 FPGA 的功能、發展歷程、使用方式不太熟悉。本系列文章包含多個部分,第 1 篇詳細介紹了 FPGA;第 2 篇聚焦於 Lattice Semiconductor 提供的 FPGA 產品;第 3 篇著重介紹了 Microchip Technology (出自子公司 Microsemi Corporation) 的 FPGA 元件系列及設計工具。本文是第 4 篇,探討了 Xilinx 的元件與工具。第 5 篇則會討論 Altera 的產品。

正如第 1 篇所討論,現場可編程閘極陣列 (FPGA) 具有許多特性,因此無論是獨立使用,還是在異質架構中使用,都是寶貴的運算資產;然而許多設計人員不熟悉 FPGA,也不知道如何將這些元件整合到自己的設計中。

為了克服這個障礙,我們需要深入探討主流廠商的 FPGA 架構以及相關工具;本文將從 Xilinx 的產品系列展開討論。

高階 FPGA 選項概覽

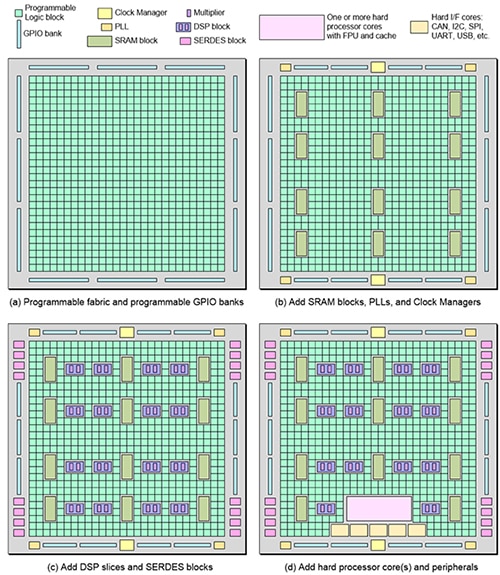

市面上有許多不同類型的 FPGA,每一種都具有不同的能力與功能組合。無論是何種 FPGA,其核心都是可編程結構。此結構以可編程邏輯區塊陣列呈現,又稱為邏輯元件 (LE) (圖 1a)。FPGA 結構進一步擴展後可包括 SRAM 區塊 (稱為區塊 RAM (BRAM))、鎖相迴路 (PLL) 及時脈管理器等元件 (圖 1b)。此外,也可加入數位訊號處理 (DSP) 區塊 (稱為 DSP 分割) 和高速串列器/解串列器 (SERDES) 區塊 (圖 1c)。

圖 1:最簡單的 FPGA 僅包含可編程結構和可配置一般用途 IO (GPIO) (a);但不同的架構會使用一些元件來擴大這一基礎結構,如 SRAM 區塊、PLL 和時脈管理器 (b);DSP 區塊和 SERDES 介面 (c);以及處理器硬核和周邊裝置 (d)。(圖片來源:Max Maxfield)

圖 1:最簡單的 FPGA 僅包含可編程結構和可配置一般用途 IO (GPIO) (a);但不同的架構會使用一些元件來擴大這一基礎結構,如 SRAM 區塊、PLL 和時脈管理器 (b);DSP 區塊和 SERDES 介面 (c);以及處理器硬核和周邊裝置 (d)。(圖片來源:Max Maxfield)

CAN、I2C、SPI、UART 和 USB 等周邊裝置介面功能,可以實作為可編程結構中的軟核心,但許多 FPGA 都將其作為硬核心包含在矽中。同樣,微處理器也可實作為可編程結構中的軟核心,或是矽中的硬核心 (圖 1d)。具備硬處理器核心的 FPGA,稱為系統單晶片 (SoC) FPGA。不同的 FPGA 會提供不同的功能、特點、能力及容量組合,可適用於不同的市場與應用。

FPGA 廠商為數不少,其中包括 Altera (已被 Intel 收購)、Atmel (已被 Microchip Technology 收購)、Efinix、Lattice Semiconductor、Microsemi (也已被 Microchip Technology 收購) 以及 Xilinx。

這些廠商全都提供多種系列的 FPGA;有些提供 SoC FPGA,有些提供鎖定人工智慧 (AI) 和機器學習 (ML) 應用的元件,有些則提供可耐受輻射且針對太空等高輻射環境設計的元件。由於可選的系列實在太多,每個都提供不同的資源,因此針對手邊的任務挑選最佳元件並不容易。

Xilinx 的 FPGA、SoC、MPSoC、RFSoC 和 ACAP 產品介紹

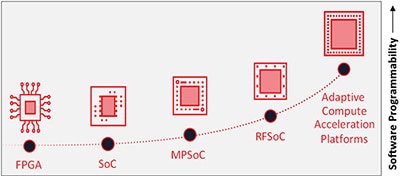

Xilinx 提供許多款可編程元件產品,從最普通到極高的效能與功能都有。範圍包括傳統的 FPGA、SoC (具備單一硬核心處理器的 FPGA 可編程結構)、MPSoC (具備多重硬核心處理器的 FPGA 可編程結構)、RFSoC (具備 RF 能力的 MPSoC),再到 ACAP (適應性運算加速平台) (圖 2)。

圖 2:Xilinx 架構產品組合隨著時間不斷演變,原本只是內含可編程結構的簡易 FPGA,後來變成可編程結構經過擴展的 SoC 元件 (增加硬核心處理器)、具有多個處理器的 MPSoC、具備 RF 能力的 RFSoC,再到鎖定於 AI 等應用的最新一代 ACAP。(圖片來源:Max Maxfield)

圖 2:Xilinx 架構產品組合隨著時間不斷演變,原本只是內含可編程結構的簡易 FPGA,後來變成可編程結構經過擴展的 SoC 元件 (增加硬核心處理器)、具有多個處理器的 MPSoC、具備 RF 能力的 RFSoC,再到鎖定於 AI 等應用的最新一代 ACAP。(圖片來源:Max Maxfield)

Xilinx 產品組合非常廣泛,可用於非常多的市場區隔,並提供各種各樣的部署方法,因此對不熟悉 FPGA 的人來說,可能很難瞭解全貌。

Xilinx 應對的市場包括但不限於資料中心 (運算、網路、儲存);通訊 (有線、無線);航太與國防;工業、科學與醫療 (ISM);測試、測量與模擬 (TME);以及汽車、廣播和消費性市場。

在部署方法方面,當中包含 Xilinx 所謂的硬體可調適元件,包括晶片、評估板和開發套件;可部署終端系統,包括系統模組和 PCIe 加速卡;以及 FPGA 即服務 (FAAS),包括藉由一流雲端提供業者來評估與善用 Xilinx 技術,這些業者包括 Amazon Web Services (AWS)、Alibaba.com 和 Nimbix.net。

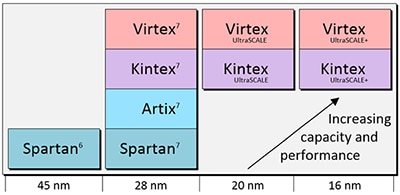

Xilinx 的 FPGA 產品分類方法之一,是依照製程技術節點來分類 (圖 3)。

圖 3:Xilinx 的 FPGA 產品提供完整的多節點產品組合,可滿足許多應用的要求。(圖片來源:Max Maxfield)

圖 3:Xilinx 的 FPGA 產品提供完整的多節點產品組合,可滿足許多應用的要求。(圖片來源:Max Maxfield)

根據目標應用而定,設計人員可能會選擇在較前期的技術節點,實作低成本、小型覆蓋區的 FPGA,或是針對先進的網路應用等,選擇在最新的技術節點,實作高容量、高頻寬、高效能的元件。

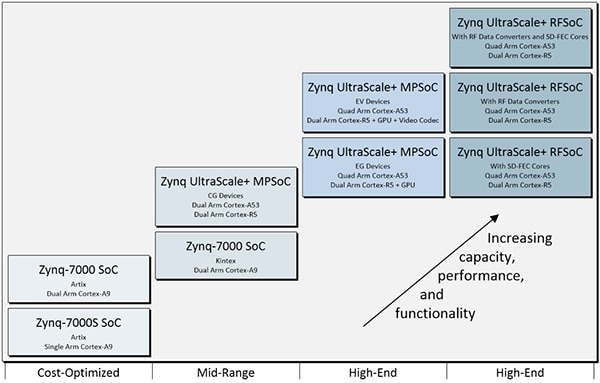

對於需要一或多個硬處理器核心 (和其他硬化功能,如 GPU、編解碼器,以及軟決策前向錯誤修正 (SD-FEC) 核心) 的設計,Xilinx 則提供一個稱為 Zynq 的元件系列。圖 4 顯示 Zynq 的 SoC、MPSoC 和 RFSoC 產品摘要。這套解決方案為設計人員提供多種能力,協助針對功率、效能、成本及上市時間進行最佳化。

圖 4:Xilinx 的 SoC、MPSoC 及 RFSoC 產品整合了處理器的軟體可編程性,以及 FPGA 的硬體可編程性,從而為設計人員提供高系統效能、彈性與可擴充性。(圖片來源:Max Maxfield)

圖 4:Xilinx 的 SoC、MPSoC 及 RFSoC 產品整合了處理器的軟體可編程性,以及 FPGA 的硬體可編程性,從而為設計人員提供高系統效能、彈性與可擴充性。(圖片來源:Max Maxfield)

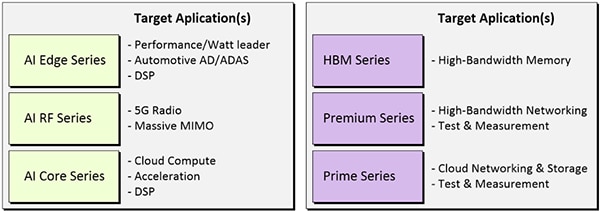

Xilinx 的最新產品是 Versal 適應性運算加速平台 (ACAP) 元件,全部實作於 7 nm 製程技術節點。ACAP 是高度整合的多核心運算平台,可適應不斷演進的各種演算法。這些平台能在硬體和軟體層級進行動態客製化,以符合廣泛的應用與工作負載。ACAP 是根據可編程網路晶片 (NoC) 進行建構,硬體設計人員與軟體開發人員皆能輕鬆對其進行編程。

Versal 元件的新特點包括:智慧引擎,即用於 ML 和 DSP 工作負載的大規模向量處理器陣列;高頻寬、低延遲、低功耗的可編程 NoC,可移動 TB 規模資料;以及整合式外殼,可利用預先打造的核心基礎架構和系統連接性,來提升效能、利用率與生產力。

圖 5 顯示了 Versal ACAP 產品組合概覽。

圖 5:Xilinx 的 Versal ACAP 是高度整合的多核心運算平台,可適應不斷演進的各種演算法。ACAP 能在硬體和軟體層級進行動態客製化,以符合廣泛的應用與工作負載。(圖片來源:Max Maxfield)

圖 5:Xilinx 的 Versal ACAP 是高度整合的多核心運算平台,可適應不斷演進的各種演算法。ACAP 能在硬體和軟體層級進行動態客製化,以符合廣泛的應用與工作負載。(圖片來源:Max Maxfield)

如同之後設計工具部分所探討,有關 Versal 元件的一個關鍵差異點是採用新的軟體堆疊。此堆疊的目標使用者是資料科學家與軟體工程師,以及傳統硬體設計工程師。

Xilinx 元件目前選擇非常多,代表性元件包括 Artix-7 FPGA、Kintex UltraScale FPGA、Kintex UltraScale+ FPGA、Trenz Electronic GmbH 的 Zynq-7000 SoC 模組,以及 Zynq UltraScale+ MPSoC。

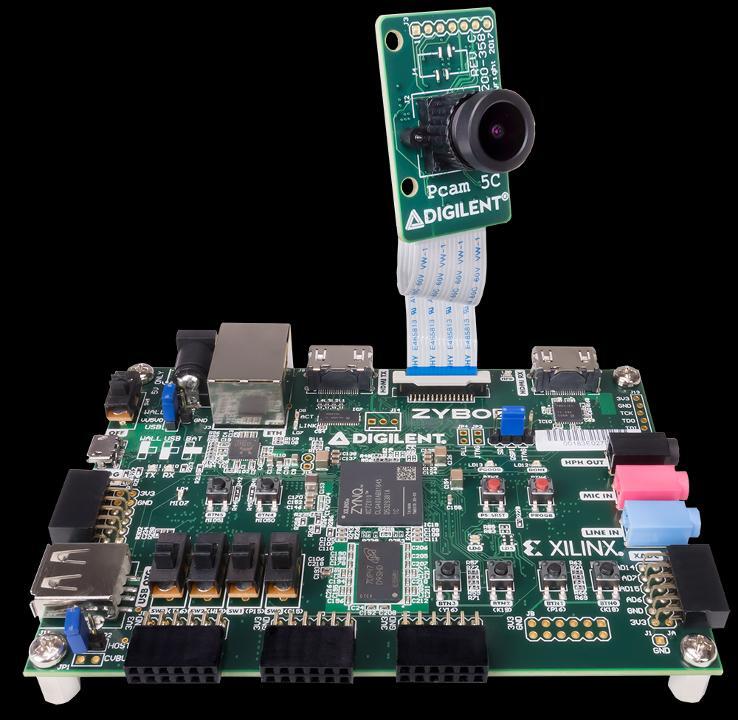

評估板及開發板的選擇同樣也很多,代表性產品包括 Digilent 的 Artix-7 FPGA 評估板、Analog Devices 的 Kintex UltraScale FPGA 評估板、Xilinx 的 Kintex UltraScale+ FPGA 評估板、Digilent 的 Zynq-7000 SoC FPGA 評估板,以及 Xilinx 的 Zynq UltraScale+ MPSoC FPGA 評估板。

利用 Xilinx FPGA、SoC 和 ACAP 進行設計與開發

與競爭對手相比,Xilinx 獨特之處在於設計工具與流程的廣度和深度。

此 FPGA 系列文章的第 1 篇提過,以往這些元件的設計方式是,讓工程師使用 Verilog 或 VHDL 等硬體描述語言 (HDL),在名為暫存器轉移層級 (RTL) 的抽象層級擷取設計意圖。這些 RTL 描述可能會先進行模擬,以驗證其是否按預期執行,然後會傳遞至合成工具,由其產生用來編程 FPGA 的配置檔。

抽象的下一步是擷取設計意圖,主要是利用 C/C++ 等編程語言,或透過 SystemC 等特別實作方式;後者是一組 C++ 類別與巨集,可提供事件驅動式模擬介面。這些能促進同步程序的模擬,每個程序皆透過清楚的 C++ 語法進行描述。這種描述可當作一般的程式來執行,藉此進行分析和剖析,之後會傳遞至高階合成 (HLS) 引擎,由此引擎輸出 RTL,RTL 則饋送至一般的合成引擎。

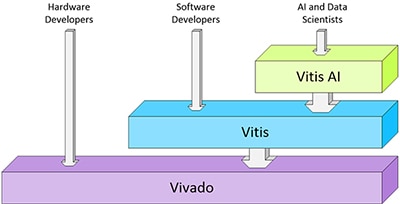

這些功能全部包含在 HLx 版 Vivado 設計套件中,此工具的輸出是配置位元流,隨後將載入到目標 FPGA、SoC、MPSoC、RFSoC 或 ACAP 元件中。除了可讓硬體開發人員徹底善用 C 語言型設計,以及經過最佳化的設計重用性,Vivado 還提供 IP 子系統重用性和整合自動化,並能加速設計收斂 (圖 6)。

圖 6:Xilinx 的 Vivado 與 Vitis 設計工具堆疊的深度檢視圖,反映出使用者能如何在最適當的抽象層級使用這些工具。硬體設計人員使用 Vivado,軟體開發人員使用 Vitis,而 AI 和資料科學家使用 Vitis AI。(圖片來源:Max Maxfield)

圖 6:Xilinx 的 Vivado 與 Vitis 設計工具堆疊的深度檢視圖,反映出使用者能如何在最適當的抽象層級使用這些工具。硬體設計人員使用 Vivado,軟體開發人員使用 Vitis,而 AI 和資料科學家使用 Vitis AI。(圖片來源:Max Maxfield)

下個抽象層級獲得 Vitis 統一軟體平台的支援,此平台使軟體開發人員能完美打造出加速型應用。從概念上說,Vitis 頂端上是 Vitis AI,此平台讓 AI 和資料科學家能在 TensorFlow 抽象層級作業。Vitis AI 是在 Xilinx 硬體平台上進行 AI 推論的開發平台,同時包括邊緣設備和 Alveo PCIe 卡。Vitis AI 包含經過最佳化的 IP、工具、資料庫、模型與範例設計,目的是徹底利用 Xilinx 的 FPGA 和 ACAP 元件之 AI 加速潛力。

Vitis AI 會饋送到 Vitis,Vitis 本身會饋送到 Vivado。圖 6 的關鍵重點是,使用者只會「看到」他們需要「看到」的部分。也就是說,硬體開發人員只會「看到」Vivado,軟體開發人員只會「看到」Vitis,而 AI 和資料科學家只會「看到」Vitis AI。如此一來,使用者就能在最適當的抽象層級使用這些工具。

若為軟體開發人員提供 Vitis 等工具套件,將他們與底層的硬體隔離開來,那麼便能讓更多的開發人員取得 FPGA。同樣地,若為 AI 和資料科學家提供 Vitis AI 等工具套件,讓他們關注於自己的抽象層級並與底層軟體隔離開來,也能讓一群新的開發人員取得 FPGA。

在提供這些能力層面,Xilinx 扮演著整個產業的先鋒推手,將 FPGA 工具提升到更高的設計抽象層級,進而讓開發人員能更輕易地運用這些元件的能力,並整合到接下來的設計中。

結論

最佳的處理設計解決方案通常由處理器與 FPGA 的組合提供;也可由 FPGA 本身或以處理器硬核心為部分結構的 FPGA 提供。FPGA 技術近年來迅速發展,能在靈活性、處理速度和功率方面滿足設計的許多要求,因而可用於許多應用,包括智慧型介面、機械視覺及人工智慧等。

如本文所述,Xilinx 提供多款可編程元件,從最普通到極高的效能與功能都有。這些產品的範圍包括傳統的 FPGA、SoC (具備單一硬核心處理器的 FPGA 可編程結構)、MPSoC (具備多重硬核心處理器的 FPGA 可編程結構)、RFSoC (具備 RF 能力的 MPSoC),再到 ACAP (適應性運算加速平台)。

為了協助設計人員使用這些元件來創造設計,Xilinx 提供了一套相應的工具,來解決硬體開發人員 (Vivado)、軟體開發人員 (Vitis) 及 AI 和資料科學家 (Vitis AI) 的需求。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。