為何以及如何使用將 Efinix FPGA 實現人工智慧/機器學習成像 — 第 1 篇:快速入門

資料提供者:DigiKey 歐洲編輯群

2023-04-20

編者說明:全新的 FPGA 架構方法帶來更精細的控制和更大的靈活性,可滿足機器學習 (ML) 和人工智慧 (AI) 的需求。此系列文章分為兩篇,第 1 篇介紹 Efinix 的一款此類架構,以及如何利用開發板著手使用此產品。第 2 篇則探討如何將開發板介接到攝影機等外部裝置及周邊裝置。

FPGA 在許多應用中都扮演著重要的角色,如工業控制與安全、機器人、航太與汽車應用等。由於其可編程邏輯核心極具靈活性,且具備廣泛的介接功能,已有越來越多 FPGA 應用於機器學習推理領域的影像處理。FPGA 非常適合用來實作具有多個高速攝影機介面的解決方案。此外,FPGA 還可實作專用的邏輯處理管線,故而可消除以 CPU 或 GPU 為基礎的解決方案的相關瓶頸。

但是,對於許多開發人員而言,其應用需要有更多的機器學習/人工智慧功能,以及更精細的控制或路由與邏輯,而這不是傳統組合邏輯區塊 (CLB) 型 FPGA 架構所能提供的。全新的 FPGA 架構方法可以解決這些問題。例如,Efinix 的 Quantum 架構採用可互換邏輯和路由 (XLR) 區塊。

本文討論 Efinix FPGA 架構的主要特點和屬性,重點介紹此架構的人工智慧/機器學習能力並探討實際的實作。然後,本文討論一款開發板,以及開發人員可使用哪些相關工具來快速開始下一個人工智慧/機器學習成像設計。

Efinix FPGA 元件

Efinix 目前提供兩個元件系列。Trion 系列最早推出,其邏輯密度介於 4000 到 12 萬個邏輯單元 (LE),以 SMIC 40LL 製程製造。最新系列是 Titanium 系列,邏輯密度介於 35,000 到 100 萬個邏輯單元,以非常熱門的 TSMC 16 nm 節點製造。

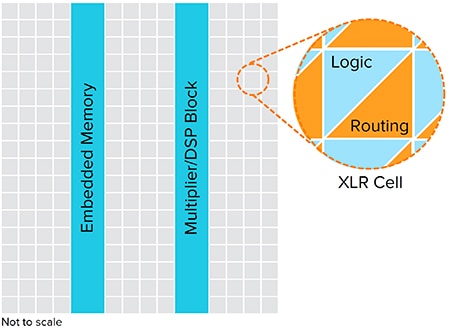

這兩個系列都是以 Quantum 架構為基礎,這在 FPGA 領域獨一無二。標準 FPGA 架構以 CLB 為基礎,至少包含查找表 (LUT) 與正反器。CLB 會實作邏輯方程式,之後再透過路由進行互連。Efinix Quantum 架構則採用 XLR 區塊,擺脫單獨的邏輯和路由區塊。

XLR 區塊之所以獨特,是因為它可以被配置為一個含有 LUT、暫存器和加法器的邏輯元件,或配置為一個路由矩陣。這種方法提供更精細的架構,可實現靈活的路由,讓具有複雜邏輯或路由的實作達到所需的效能。

圖 1:XLR 區塊之所以獨特,是因為可以被配置為一個含有 LUT、暫存器和加法器的邏輯元件,或配置為一個路由矩陣。(圖片來源:Efinix)

圖 1:XLR 區塊之所以獨特,是因為可以被配置為一個含有 LUT、暫存器和加法器的邏輯元件,或配置為一個路由矩陣。(圖片來源:Efinix)

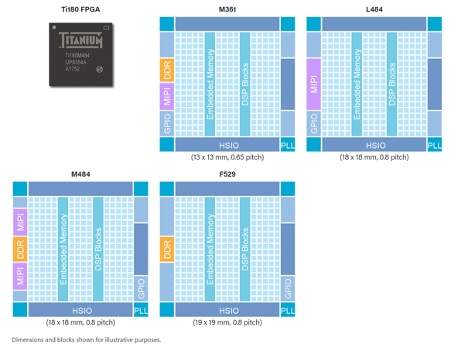

最新的 Titanium 元件系列則為開發人員提供最先進的功能 (圖 2)。搭配 XLR 核心,此系列元件可提供傳輸速率達 16 Gbps 或 25.8 Gbps 的 Multi-Gigabit 序列鏈路,實際視所選的元件而定。這些 Multi-Gigabit 鏈路,對進行晶片內外的高速資料傳輸非常重要。

圖 2:Titanium FPGA Ti180 具有多個選項,實際視匯流排寬度、I/O 與記憶體需求而定。(圖片來源:Efinix)

圖 2:Titanium FPGA Ti180 具有多個選項,實際視匯流排寬度、I/O 與記憶體需求而定。(圖片來源:Efinix)

Titanium 元件還提供廣泛的輸入/輸出 (I/O) 介接功能,這些功能可歸類為一般用途 I/O (GPIO)、並可支援單端 I/O 標準,如 3.3 V、2.5 V 和 1.8 V 下的低電壓 CMOS (LVCMOS)。

對於高速與差動介接,Titanium 元件提供高速 I/O (HSIO),可支援單端 I/O 標準,例如 1.2V、1.5V 下的 LVCMOS 以及 SSTL 和 HSTL。HSIO 支援的差動 I/O 標準,則包括低電壓差動訊號 (LVDS)、差動 SSTL 和 HSTL。

此外,現代 FPGA 還需要緊密耦合的高頻寬記憶體來儲存用於影像處理應用的影像訊框以及用於訊號處理的樣本資料,當然還包括為 FPGA 中實作的處理器,執行作業系統與軟體。Titanium 系列元件可介接動態數據傳輸率 4 (DDR4) 及低功率 DDR4(x) (LPDDR4(x))。根據所選的具體 Titanium 元件,支援的匯流排寬度為 x32 (J) 或 x16 (M),某些元件不支援 LPDDR4 (L)。

Titanium FPGA 以 SRAM 為基礎,並需要配置記憶體,而元件配置由主/從序列周邊互連 (SPI) 或 JTAG 來執行。為了確保此配置方法的安全性,Titanium FPGA 使用 AES GCM 來加密位元流,並使用 AES GCM 和 RSA-4096 進行位元流身份驗證。採取此等高安全措施是非常必要的,原因就在於 FPGA 部署於邊緣處,而惡意攻擊者可在邊緣存取和操縱其行為。

開發板簡介

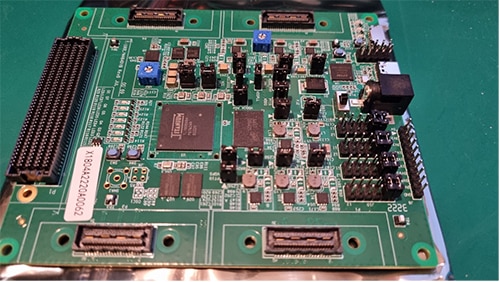

開發板是 FPGA 評估流程的關鍵要素,可用於探索元件和原型應用的功能,有助於降低整體風險。Ti180 M484 是首款可用於評估 Titanium FPGA 以及開展原型開發應用的開發板 (圖 3)。此板件配有一個 FPGA 夾層卡 (FMC) 連接器和四個 Samtec QSE 連接器。

圖 3:除了 Titanium FPGA,Ti180 M484 開發套件還配有一個 FMC 連接器和四個 Samtec QSE 連接器。(圖片來源:Adam Taylor)

圖 3:除了 Titanium FPGA,Ti180 M484 開發套件還配有一個 FMC 連接器和四個 Samtec QSE 連接器。(圖片來源:Adam Taylor)

此開發板裝配的 Ti180 FPGA,提供 17.2 萬個 XLR 單元、32 個全域時脈、640 個數位訊號處理 (DSP) 元件和 13 Mbit 嵌入式 RAM。DSP 元件可用於實現固定點 18 x 19 乘法運算和 48 位元乘法運算。此 DSP 還可針對在雙重或四重配置中執行的單指令多重數據 (SIMD) 運算,進行最佳化。此外,DSP 元件也可配置為執行浮點運算。

和大多數開發板一樣,Ti180 開發板也提供簡易的 LED 和按鈕。但是,它真正的強大之處在於介接功能。Ti180 開發板配有一個低引腳數的 FMC 連接器,可連接多種周邊裝置。由於這是一項廣泛使用的標準,市面上有許多 FMC 卡都可介接高速類比數位轉換器 (ADC)、數位類比轉換器 (DAC)、網路,以及記憶體/儲存解決方案。

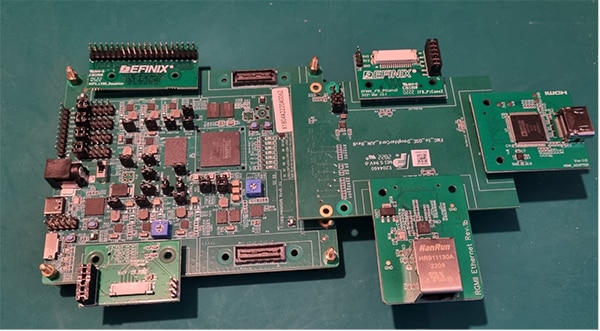

除了 FMC 連接之外,此板件還配有四個 Samtec QSE 連接器,可供開發人員增添擴充卡。這些 QSE 連接器可用於提供 MIPI 輸入和輸出,其中一個 QSE 連接器提供一個 MIPI 輸入或輸出。

圖 4:如圖所示,Ti180 M484 開發套件具有多個擴充選項 (以 QSE 和 FMC 連接器為基礎)。(圖片來源:Adam Taylor)

圖 4:如圖所示,Ti180 M484 開發套件具有多個擴充選項 (以 QSE 和 FMC 連接器為基礎)。(圖片來源:Adam Taylor)

Ti180 開發板還提供 256 Mbit 的 LPDDR4,可支援影像或訊號處理應用所需的高效能記憶體。此外,此開發板亦提供一系列時脈選項 (25、33.33、50、74.25 MHz),可配合元件鎖相迴路 (PLL) 來產生不同的內部頻率。

在開發過程中能否即時在板件上重新編程和除錯非常重要,而這就需要仰賴 JTAG 連接,此板件可透過 USB-C 介面提供此連接。此外,此板件還提供非揮發性記憶體,即兩個 256 Mbit NOR 快閃記憶體元件,可用於展示配置解決方案。

此開發板由盒內隨附的 12 V 通用電源配接器供電,並附有 FMC 到 QSE 分接板,以及用於 HDMI、乙太網路、MIPI 與 LVDS 的 QSE 型擴充卡。為了展示 Ti180 影像處理功能,開發板還提供了一個雙 RPI 子卡和兩個 IMX477 攝影機卡。

軟體環境

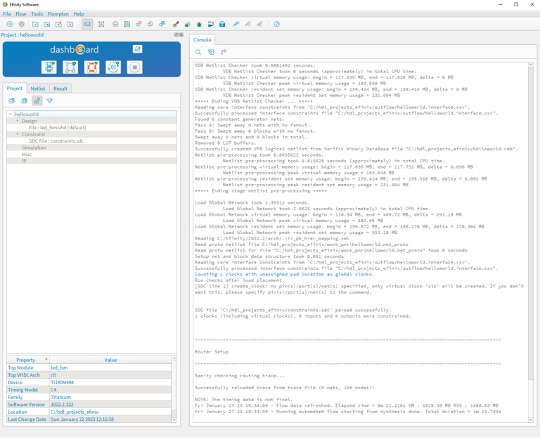

在實作以 Ti180 開發板為目標的設計時,要使用 Efinix 軟體 Efinity。此軟體可透過合成、佈設與路由,產生位元串流。此外,還可為開發人員提供智慧財產 (IP) 區塊、計時分析以及晶片上除錯功能。

請注意,需要使用開發板才能存取 Efinity 軟體。但與其他廠商不同的是,此工具沒有其他需要額外授權的版本。

Efinity 會針對所選的元件建立新的專案。RTL 檔案之後會添加至專案中,並針對計時和 I/O 設計來建立約束條件。在 Efinity 中,開發人員還可利用 HSIO、GPIO 和專用 I/O 來實作 I/O 設計。

圖 5:Efinity 會針對所選的元件建立新的專案。(圖片來源:Adam Taylor)

圖 5:Efinity 會針對所選的元件建立新的專案。(圖片來源:Adam Taylor)

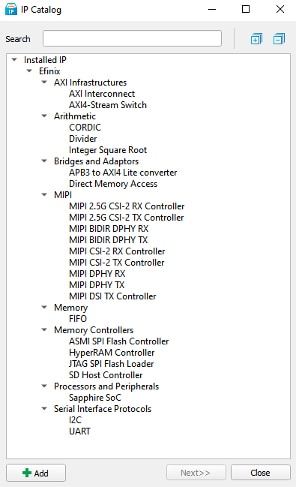

FPGA 設計的一個關鍵要素是充分利用 IP,特別是對於 AXI 互連、記憶體控制器和軟核心處理器等複雜的 IP。Efinity 為開發人員提供一系列可用於加速設計流程的 IP 區塊。

圖 6:Efinity 為開發人員提供了可用於加速設計流程的 IP 產品目錄。(圖片來源:Adam Taylor)

圖 6:Efinity 為開發人員提供了可用於加速設計流程的 IP 產品目錄。(圖片來源:Adam Taylor)

雖然 FPGA 在實作平行處理結構上表現優異,但許多 FPGA 設計中都含有軟核心處理器。這些處理器能夠實作序列處理,例如網路通訊。為了能在 Efinix 元件中部署軟核心處理器,Efinity 提供了 Sapphire 系統單晶片 (SoC) 配置工具。Sapphire 允許開發人員定義一個多處理器系統,以跨多個處理器達到快取和快取一致性,並執行嵌入式 Linux 作業系統。在 Sapphire 中,開發人員可以選擇一到四個軟核心處理器。

所實作的軟核心處理器是 VexRiscV 軟 CPU,此 CPU 以 RISC-V 指令集架構為基礎。VexRiscV 處理器是一款 32 位元的處理器,具有管線化擴充元件,並提供可設定的特性集,非常適合用作 Efinix 元件中的軟核心處理器。可選配置包括乘法器、原子指令、浮點擴充和壓縮指令。依 SoC 系統的配置而定,效能範圍將介於 0.86 和 1.05 DMIPS/MHz 之間。

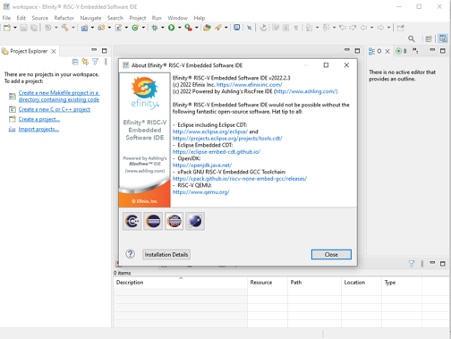

在 Efinix 元件中設計和實作硬體環境後,即可使用 Ashling RiscFree IDE 來開發應用軟體。Ashling RiscFree 是一款以 Eclipse 為基礎的 IDE,可用於建立和編譯應用軟體,並對目標進行除錯,以在部署之前微調應用。

圖 7:Ashling RiscFree 是一款以 Eclipse 為基礎的 IDE,可用於建立和編譯應用軟體,並對目標進行除錯。(圖片來源:Adam Taylor)

圖 7:Ashling RiscFree 是一款以 Eclipse 為基礎的 IDE,可用於建立和編譯應用軟體,並對目標進行除錯。(圖片來源:Adam Taylor)

如果開發的是嵌入式 Linux 解決方案,則會提供所有必要的引導工具,包括 First Stage Boot Loader、OpenSBI,和採用 Buildroot 的 Linux。或者,如果需要即時解決方案,開發人員可以使用 FreeRTOS。

人工智慧實作

Efinix 的人工智慧實作以 RISC-V 軟核心運算為基礎。它利用 RISC-V 處理器的客制化指令功能來加速 TensorFlow Lite 解決方案。此外,使用 RISC-V 處理器還可讓使用者建立客制化指令,將其用作人工智慧推理後的預處理或後處理的一部分,進而建立出更具響應性和確定性的解決方案。

要開始進行人工智慧實作,第一步是探索 Efinix 模型庫,這是一個已針對其終端技術進行最佳化的人工智慧/機器學習模型庫。使用 Efinix 元件的開發人員可以存取此模型庫,並使用 Jupyter Notebook 或 Google Colab 來訓練網路。網路經過訓練後,便可使用 TensorFlow Lite 轉換器將其從浮點模型轉換為量子化模型。

轉換為 TensorFlow Lite 格式後,即可使用 Efinix 的 tinyML 加速器,在 RISC-V 解決方案上建立可部署的解決方案。tinyML 產生器允許開發人員客製化加速器實作並產生專案檔。以這種方式部署時,速度可加快 4 倍至 200 倍,實際視所選的架構和客製化程度而定。

結論

Efinix 元件採用獨特的 XLR 架構,可為開發人員提供靈活性。此工具鏈不僅能夠實作 RTL 設計,還能實作部署軟核心 RISC-V 處理器的複雜 SoC 解決方案。人工智慧/機器學習解決方案可建立在軟核心 SoC 之上,用於部署機器學習推理。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。