控制電源啟動和關閉的通電順序

資料提供者:DigiKey 北美編輯群

2018-11-14

微處理器、FPGA、DSP、類比數位轉換器 (ADC) 以及系統單晶片 (SoC) 元件,一般都會用多個電壓軌來運作。為了避免發生鎖定、匯流排爭用和高湧入電流的情況,設計人員必須以特定的順序來啟動和關閉這些電軌。此流程稱為通電順序控制或電源定序,且目前有多種解決方案可有效進行此作業。

有些需進行電壓定序的複雜元件,其核心和類比區塊的電壓軌可能必須比數位 I/O 電軌更早通電。雖然有些設計可能必須採用不同的順序,但無論如何都需要適當的通電與斷電順序,以免發生問題。

目前已推出許多能讓元件有效升電和斷電的電源定序器、監視器與監測器,這些產品也採用一些技術來監控電壓及電流位準以計算功率位準,藉此保護複雜的積體電路和子組件。

本文將詳細說明電源定序,並探討電源定序的規格和技術,並說明如何應用電源定序器,達到指定的電軌時序與定序要求。

為什麼要擔心電源定序的問題?

FPGA 和類似的複雜 IC 在內部分成許多個電源域。這些 IC 大部分都需要以特定的順序來啟動或關閉元件。例如,FPGA 一般會分別供電給核心邏輯、I/O 和輔助電路。

核心通常包含 FPGA 的處理器以及邏輯基礎。這個電源域具有低電壓、高電流的電源配置特性。由於電壓極低,在準確度方面的要求非常高,而且基於數位負載的動態本質,因此必須達到極佳的暫態效能。I/O 代表 FPGA 的各種輸入與輸出。電壓需求則取決於介面的類型。一般來說,I/O 的電壓位準會比核心的電壓位準高。電流需求則依 I/O 的類型、數量及速度而異。

輔助電路包含 FPGA 中的噪敏類比電路,例如鎖相迴路 (PLL) 以及其他類比電路元素。雖然電流需求相當低,但漣波電壓是一大問題,必須盡可能降低。類比區塊的漣波可能會在 PLL 中造成過度抖動和相位雜訊,並在放大器中產生雜散響應。

以錯誤的順序啟動每個電源域的電源供應器,可能會產生問題並讓 FPGA 受損。試想一下,I/O 區塊是以收發三態匯流排上的資料作為基礎。I/O 控制由核心來處理。如果 I/O 域比核心更早啟動,I/O 針腳最終會處於不確定的狀態。如果外部匯流排元件啟動,可能會產生匯流排爭用的情形,導致 I/O 驅動器中出現高電流。因此,核心應該比 I/O 域更早啟動。請務必參考供應商的 FPGA 規格,瞭解建議的通電與斷電順序,以及電軌之間的最大差動電壓。

同樣地,功率運算放大器等元件有兩個電源域,即類比域和數位域。數位域會供電給放大器的診斷狀態旗標,以顯示出過溫和過電流狀態。數位域也支援放大器的開關功能性。元件規格要求數位域必須比類比電源更早啟動,以便這些狀態旗標能在類比域啟動之前正常運作,以避免元件受到可能的損壞。

電源定序法

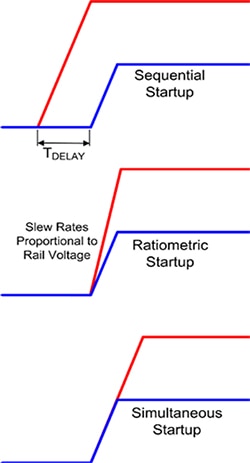

多電軌定序有三種常見的類型 (圖 1)。最常見的是循序法,也就是先啟動一個電軌,然後延遲一段時間,之後再啟動第二個電軌。設定延遲的目的是讓第一個電軌先達到穩壓狀態,然後再啟動第二個電軌。

圖 1:電源供應器的三種定序技術。無論使用哪一種技術,電壓都必須單調上升,否則元件不會正確初始化,因為電壓在啟動期間會意外壓降。(圖片來源:DigiKey)

第二種定序技術是比例式法。在此技術下,電軌會同時啟動,並同時達到各自的額定電壓。而電軌的上升時間必須與電軌的電壓呈比例,以便同時達到穩壓狀態。

有些元件可能不容許在尚未達到穩壓前就發生瞬間壓差的情況。這會導致元件在這段期間,從某一個電源供應器汲取較高的電流。

第三種作法是同時啟動法,可將瞬間壓差降到最低。此技術可縮小這些應力的規模和時間長度。同時啟動法通常就是將電源同時啟動,讓電壓軌以相同的速率一同上升,並讓較高的電軌 (通常是 I/O 電壓軌) 在較低電壓軌或核心電壓軌達到最後的數值後繼續上升。

無論使用哪一種技術,電壓都必須單調上升,否則元件不會正確初始化,因為電壓在啟動期間會意外壓降。

此外,還可以利用軟啟動來限制啟動期間的湧入電流。這種做法會限制啟動期間的電流,讓電軌的電容量能在啟動的過程中逐步充電。

電源供應器的斷電作業,一般會指定以啟動順序的相反順序來進行。

要選擇使用何種啟動或關閉技術,需視元件的規格而定。

電源供應器定序範例

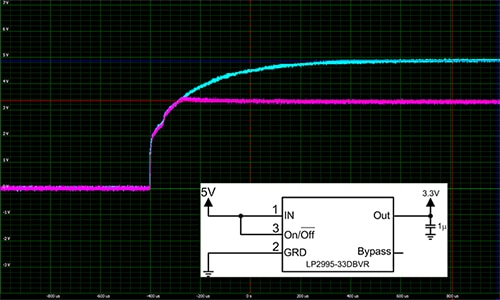

同時啟動法的設置方式相對簡單。最高電壓輸出端接至較低電壓穩壓器的輸入端 (圖 2)。

圖 2:穩壓器採用菊鏈連接可讓 5 V 與 3.3 V 電源同時啟動。(圖片來源:DigiKey)

本範例中,5 V 電源具有較高的電壓。此電源也饋送至 3.3 V 穩壓器中。從圖中可看出 5 V 和 3.3 V 輸出同時上升,而且最小壓差最高達到 3.3 V 電源的穩壓點。

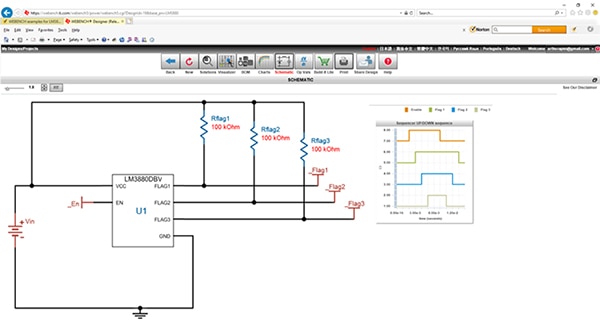

循序技術最好是利用 Texas Instruments 的 LM3880 這類定序器積體電路來實作。LM3880 是簡易型電源供應器定序器,能透過啟用輸入來控制多個獨立穩壓器或電源供應器。

啟用之後,LM3880 會依序釋出三個輸出旗標,而且旗標之間各有時間延遲。這能讓連接的電源供應器啟動。在關閉過程中,輸出旗標則會採用反向順序。圖 3 使用 Texas Instruments 的 WEBENCH Power Designer 軟體,呈現一個採用 LM3880 的設計範例。這個免費的軟體工具可協助工程師設計電源相關電路,同時提供線路圖、物料清單和模擬結果。圖中顯示線路圖與圖表、啟用輸入,以及三個旗標輸出。

LM3880 的延遲時間和通電順序雖然固定不變,但可在工廠使用內建的 EPROM 進行自訂。Texas Instruments 的 LM3881 定序器也能利用電容來編程延遲時間。

圖 3:此為 Texas Instruments 的 WEBENCH Power Designer 顯示畫面,當中顯示 LM3880 的設計線路圖,以及啟用輸入和輸出旗標 (用於控制外部穩壓器或電源供應器) 圖表。(圖片來源:DigiKey)

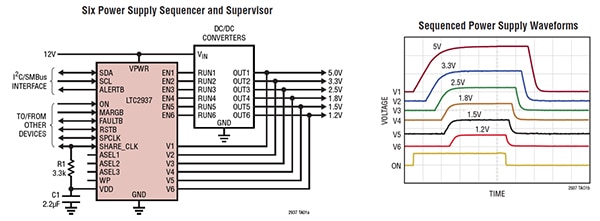

Analog Devices 提供一款精密度更高一些的電源控制元件,即 LTC2937 定序器/電壓監測器。LTC2937 和 LM3880 一樣,能控制多達六部電源供應器或穩壓器的順序和時間延遲 (圖 4)。

圖 4:LTC2937 能控制多達六部電源供應器的順序,同時監控電軌的電壓。而且只需一條電線即可同步處理多個元件,控制多達 300 部電源供應器。(圖片來源:Analog Devices)

除了對多達六個電軌定序以外,此產品也會監控這些電軌的電壓,以偵測過壓、欠壓、壓降和電源啟動停滯的問題。發生故障時,還能經由編程來關閉或重新啟動電源供應器。錯誤狀況會記錄在內部 EEPROM 中。LTC2937 能透過 I2C 或 SMBus 來編程與控制。編程作業可由 Analog Devices 的 LTpowerPlay GUI 軟體支援。EEPROM 可在不使用軟體的情況下自主運作。若系統需要使用超過六個電軌,可將多個 LTC2937 相互鏈接,即可控制多達 300 個電源供應器。

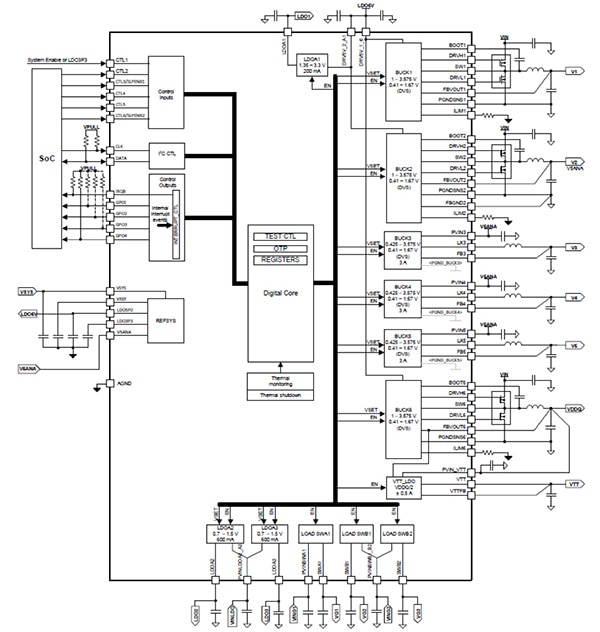

對於較複雜的多核心處理器、FPGA 及其他 SOC 元件,Texas Instruments 提供 TPS650860 可配置型多電軌電源管理單元。此單一 IC 的輸入電壓介於 5.6 V 至 21 V,含有三個降壓控制器、三個降壓轉換器、一個流入或流出低壓降 (LDO) 線性穩壓器、三個低電壓輸入 LDO、穩壓器,以及三個負載開關 (圖 5)。

圖 5:Texas Instruments 的 TPS650860 功能方塊圖,顯示 13 個穩壓輸出,其定序完全受到控制。(圖片來源:Texas Instruments)

此元件有 13 個穩壓輸出,可滿足 FPGA 或其他負載元件的需求。

降壓轉換器內建功率級,降壓控制器則需要外部功率級。這兩款轉換器和控制器都具備整合式電壓感測輸入,可監控電源輸出,並可受到控制以達到定序。負載開關含有迴轉率控制功能,可針對與這三種定序類型 (循序法、成比例法與同時啟動法) 開關的相關電軌進行編程。

TPS650860 透過 I2C 介面來控制,可利用嵌入式控制器或相關的 SoC 管理器輕鬆進行控制。這款電源管理 IC 提供一流的控制彈性。

結論

電源啟動或關閉的順序有好幾種控制方式,有的非常簡單,有的則非常複雜。這些方式的精準度、控制的電軌數、控制功能的範圍以及成本各不相同。

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。