Combine Arduino with Open-Source RISC-V Architecture for Low-Cost, High-Performance Embedded Design

資料提供者:DigiKey 北美編輯群

2018-04-04

Embedded systems developers are always looking for ways to further cut development time, especially for proofs of concept and fast prototyping. Development kits (dev kits) have become the shortcut of choice, but designers need to be able to balance form factor and a widely supported ecosystem with performance requirements.

The Arduino Uno dev board is a good example of this need to find balance. Its form factor has become extremely popular in this arena thanks to its low cost and the availability of literally hundreds of Arduino shields that provide plug-in expansion of the Arduino’s I/O capabilities. However, some developers may want more performance for certain embedded applications than an 8-bit microcontroller can provide.

For them, the solution may lie in the HiFive1 dev kit from Crowd Supply. This article introduces the low-cost HiFive1 dev kit, discusses how its features enable the rapid prototyping of high performance embedded systems, and describes the development tools available to help designers get started.

What is HiFive1?

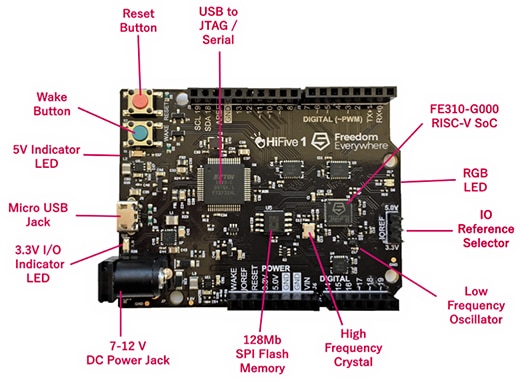

The HiFive1 dev kit is based on a microcontroller that incorporates a 32-bit RISC-V (pronounced "risk-five") processor core (Figure 1). The board accepts Arduino-style shields, greatly expanding its utility for rapid prototyping of embedded designs.

Figure 1: The HiFive1 Arduino-compatible dev board uses a microcontroller based on a 32-bit RISC-V processor core. (Image source: SiFive)

At the heart of the HiFive1 is the RISC-V processor core. This takes the open source concept behind Arduino boards, and extends it all the way to the processor itself. The RISC-V is an open instruction set architecture (ISA) based solidly on two foundations: reduced instruction set computing (RISC) concepts that have been around since the 1980s, and open source principles. Because it’s open source, the RISC-V ISA can be freely used for any purpose. Anyone can design, manufacture, and sell RISC-V-based chips and software without paying royalties.

The RISC-V-based microcontroller on the HiFive1 board can be programmed to support eXecute In Place (XIP) modes to reduce SPI command overhead during instruction cache refills. The microcontroller’s quad SPI (QSPI) port supports 32 byte burst reads to accelerate instruction cache refills from the QSPI flash memory to boost performance using the memory’s XIP mode.

The microcontroller can run at clock rates faster than 320 MHz, but on the HiFive1 board this should be limited to no faster than 133 MHz, keeping the microcontroller’s SPI serial clock operating within the limits of the board’s 128 Mbit QSPI flash memory.

Arduino-style headers — with caveats

The HiFive1 dev kit replicates the Arduino’s unique I/O header layout. It will accept many of the hundreds of available Arduino shields — with a couple of caveats.

First, the microcontroller does not have analog input pins. Only digital I/O, interrupt, and pulse width modulation (PWM) pin assignments are possible on the HiFive1 dev kit’s Arduino style headers. The physical header positions used for the A0 through A5 analog pins on the Arduino Uno board are labeled as digital I/O pins D14 through D19 on the HiFive1 board. If it’s necessary to add analog functions, it’s possible to use one of the many available analog-to-digital converter (ADC), digital-to-analog converter (DAC), or combo ADC/DAC Arduino shields.

Also note:

- Designers can assign as many as nine PWM generators to the Arduino-style header pins on the HiFive1 dev kit.

- All 19 of the HiFive1 dev kit’s Arduino-style header I/O pins can serve as interrupt inputs.

On-board voltage translators give the flexibility to set all the HiFive1 dev kit’s digital I/O pins for either 3.3 volt or 5 volt logic levels based on a jumper setting. The one jumper setting (marked IOREF on the board in Figure 1) defines the logic levels for all of the I/O pins on the HiFive1 dev kit’s Arduino-style header.

That leads to the second caveat: Only the following two Adafruit Arduino shields have been tested with the HiFive1 to date, though Adafruit’s support libraries for these two shields are already ported to the HiFive1 library:

- Adafruit’s Resistive Touchscreen & LED Display

- Adafruit’s BLE SPI Friend

That said, any shield that communicates with SPI, UART, or digital I/O should be easy to use with the HiFive1, though the supporting library may need minor tweaks. It’s still pretty early days for HiFive1 peripheral shield support libraries: expect the number of supported shields to grow.

Good hardware needs good software support

Software development tools for the HiFive1 dev kit are available on GitHub. The tools include a C compiler and assembler for the RISC-V processor architecture, a GDB host-resident debugger for the RISC-V processor, and a RISC-V version of OpenOCD (an on-chip debugger).

Once it’s written, compiled, and assembled, the developer uploads the program to the HiFive1 dev kit through its USB debugging interface. The HiFive1 stores the program in its on-board SPI flash memory chip. The on-board flash chip has a 16 Mbyte capacity, making it considerably larger than the code storage available on an 8-bit Arduino Uno board. This address space expansion is just one of the many advantages of a 32-bit processor architecture like RISC-V. The microcontroller’s on-chip 16 Kbyte SRAM is also relatively large.

The chip at the heart of the board

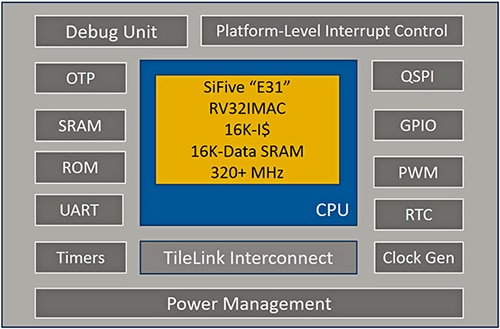

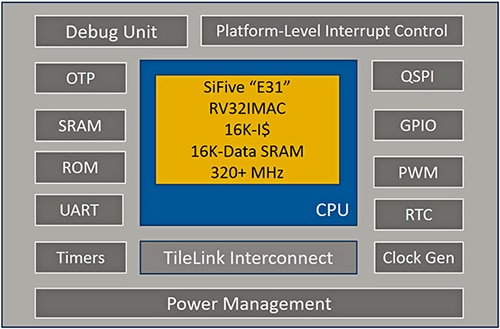

The microcontroller at the heart of the HiFive1 dev kit bears a closer look (Figure 2).

Figure 2: A simplified block diagram of the open-source RISC-V-based microcontroller. (Image source: SiFive)

The center of the microcontroller is the CPU core, which is based on the open source, 32-bit RISC-V ISA. In RISC-V speak, the core is an RV32IMAC processor, which simply means that it uses the base 32-bit RISC-V integer instruction set (RV32I) with integer hardware multiplication and division (M); atomic, real-time instructions (A); and additional support for the 16-bit compact (C) instruction set. There are 64 and 128-bit versions of the RISC-V ISA as well. The core also includes 16 Kbytes of instruction cache (noted as “I$” in the diagram) and 16 Kbytes of scratchpad SRAM. Several standard peripherals including timers, PWM signal generators, a real-time clock, a UART, QSPI serial interfaces, and an on-chip hardware debug module surround the processor core.

Who or what is behind the RISC-V architecture, and why?

The HiFive1 dev kit and microcontroller are actually hardware demo vehicles for the open-source RISC-V processor architecture, begging the question: Did the world really need another processor architecture?

The RISC-V project started at the University of California in Berkeley and eventually grew beyond the university walls and grabbed the imagination of many more volunteers and people working in the electronics industry. The end result of the project was an open-source RISC processor ISA (instruction set architecture) that is just as good as any other 32-bit RISC ISA. The difference is that the RISC-V ISA can be used freely by anyone for any purpose.

It takes an ecosystem

As with the HiFive1 board, embedded system developers need more than just a processor or microcontroller chip. For RISC-V, embedded developers need development support in the form of tools, example code, libraries, and software stacks. This support comes from the ecosystem that grows up around successful processor architectures and from users. The RISC-V processor architecture is relatively new and so is its ecosystem, but it’s growing. In addition to the development tools from SiFive discussed above, other development tools available within the RISC-V ecosystem currently include:

- The open-source GNU MCU Eclipse, a family of Eclipse plug-ins and tools for multi-platform embedded development based on GNU toolchains.

- Segger’s Embedded Studio for RISC-V, a cross-platform IDE for embedded C/C++ software development and the company’s J-Link debug probe.

Conclusion

The inexpensive Arduino Uno dev board form factor is small, lightweight, and gives access to hundreds of I/O and peripheral shields. The HiFive1 dev kit leverages those existing shields and mates them to a 32-bit RISC-V-based microcontroller by closely replicating the compact Arduino Uno board’s form factor and unique header configuration.

The HiFive1 dev kit has on-board 16 Mbyte flash memory for greater code storage capability. Though it is a new architecture, there is a budding open-source RISC-V ecosystem offering an expanding suite of software development tools, including a compiler, assembler, debugger, and an Arduino IDE library.

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。