類比基礎知識:取樣保持電路如何運作?如何確保 ADC 準確度?

資料提供者:DigiKey 北美編輯群

2020-04-22

從錄音到物聯網 (IoT)、工業物聯網 (IIoT) 以及如今的人工智慧物聯網 (AIoT),將「現實」世界中的類比訊號轉換成可在上游處理的數位訊號,這是電子系統的基本功能。不過,要有效且有效率地進行這項作業,需要瞭解背後的原理與步驟,而這些通常被人們所忽視。

例如,假如對某個類比數位轉換器 (ADC) 的輸入,施加典型的類比訊號,此訊號不斷改變振幅,而且在轉換開始和結束時並不會保持相同,那麼在進行轉換前,究竟如何對訊號進行「保持」並接著「取樣」?這樣的振幅變動或偏斜可能會導致嚴重的誤差,尤其對高解析度的 ADC 更是如此,因為此元件轉換訊號所需的時間較長。瞭解並消除此誤差來源,是設計人員所面對的挑戰。

本文將說明如何透過讓 ADC 使用取樣保持 (S&H) 或追蹤保持 (T&H) 電路,來避免振幅偏斜。取樣保持 (或追蹤保持) 元件會對輸入進行真實取樣,並在輸入抗交疊低通濾波器和 ADC 之間運作。本文將討論取樣保持 IC 的特性與選擇標準,並檢視內建取樣保持元件的 ADC。針對不同的應用,我們將列舉來自 Texas Instruments、Maxim Integrated 及 Analog Devices 的幾個不同特性的範例元件進行說明。

取樣保持在 ADC 中扮演的角色

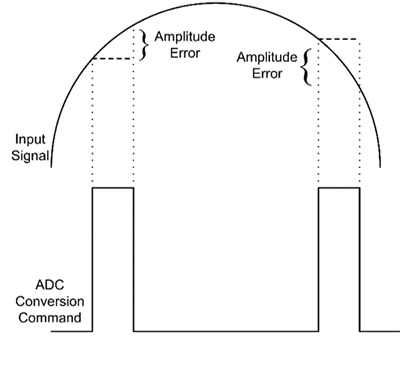

當 ADC 的輸入端施加非 DC 訊號時,該訊號會不斷改變振幅。不過,類比數位轉換過程時間間隔有限,因此在這段時間內,ADC 輸入的振幅會有所改變 (圖 1)。這種振幅偏斜可能會導致發生嚴重的誤差。

圖 1:輸入訊號變化的 ADC,會因為數位化期間的訊號振幅變動 (底部),而容易發生振幅誤差 (頂部)。(圖片來源:DigiKey)

圖 1:輸入訊號變化的 ADC,會因為數位化期間的訊號振幅變動 (底部),而容易發生振幅誤差 (頂部)。(圖片來源:DigiKey)

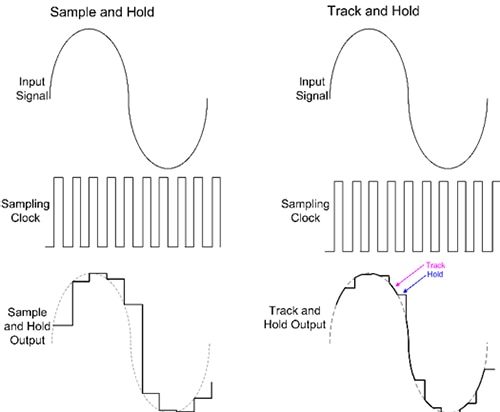

要避免 ADC 發生振幅偏斜,需要對訊號進行取樣,並在轉換過程中保持固定的振幅。而這可透過 ADC 的取樣保持或追蹤保持電路來完成 (圖 2)。

圖 2:取樣保持 (左) 和追蹤保持 (右) 電路的主要差異在於追蹤期的持續時間:取樣保持的持續時間短,而追蹤保持的持續時間長。(圖片來源:DigiKey)

圖 2:取樣保持 (左) 和追蹤保持 (右) 電路的主要差異在於追蹤期的持續時間:取樣保持的持續時間短,而追蹤保持的持續時間長。(圖片來源:DigiKey)

這兩種類型的電路都會對輸入訊號進行取樣,並在整個轉換期間,讓取樣的電壓保持恆定。追蹤保持電路輸出 (右) 會一直追蹤輸入訊號,直至收到指示進行取樣為止;接著會在 ADC 轉換期間保持取樣值。取樣保持的取樣孔徑較短,其輸出為一系列的取樣位準 (左)。追蹤保持和取樣保持之間的主要差異在於追蹤間隔的持續時間:取樣保持的持續時間非常短,追蹤保持則明顯較長。這兩種電路都仰賴快速開關,來隔絕連接到訊號輸入端的儲能電容。下文「使用取樣」保持一詞,同時代表取樣保持或追蹤保持。

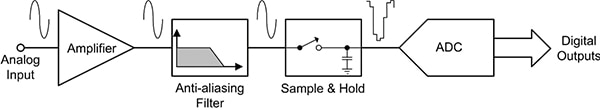

取樣保持階段會對輸入進行真實取樣,並在輸入抗交疊低通濾波器和 ADC 之間運作。低通濾波器會進行抗交疊頻段限制,而且必須在取樣保持之前完成,以便在取樣前對訊號進行頻段限制,以免發生交疊 (圖 3)。

圖 3:在數化器訊號路徑中,取樣保持元件置於抗交疊低通濾波器和 ADC 之間。(圖片來源:DigiKey)

圖 3:在數化器訊號路徑中,取樣保持元件置於抗交疊低通濾波器和 ADC 之間。(圖片來源:DigiKey)

請注意,取樣保持前的訊號都是類比訊號。取樣保持的輸出是經過取樣的波形,隨後會饋送到 ADC。

典型的取樣保持元件

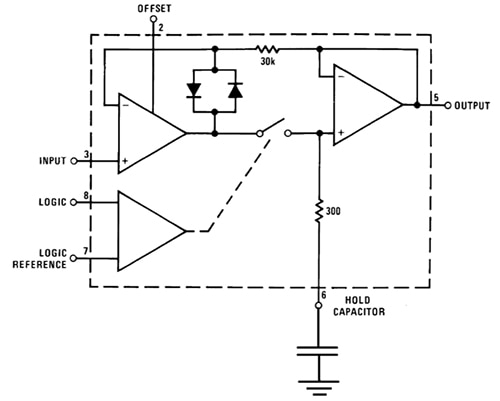

Texas Instruments 的 LF398MX/NOPB 取樣保持積體電路 (IC) 的方塊圖,顯示了基本的電路配置 (圖 4)。取樣保持的實作是使用快速開關及高品質的電容。在 LF398MX/NOPB 這個範例中,電容位於 IC 的外部。當開關關閉時,電容會充電至輸入訊號的電壓位準。當開關打開時,電容會維持該電壓,直到 ADC 對其完成數位化。此取樣保持元件採用的 bi-FET 技術結合了 FET 與雙極電晶體,可支援快速擷取 (少於 6 µs,振幅誤差為 0.01%),並具有高 DC 準確度 (通常為 0.002%),以及極低的壓降 (通常每秒低於 83 µV)。內部放大器會對開關和保持電容進行緩衝。

取樣保持元件的擷取時間視保持電容的值而定,範圍可介於 0.001 至 0.1 µF 之間。外部保持電容必須具有低介電質吸收率,以及低洩漏率。建議使用聚苯乙烯、聚丙烯以及 Teflon 電容。

圖 4:Texas Instruments 的 LF398MX/NOPB 取樣保持方塊圖展示了關鍵的元件:快速開關與外部保持電容。(圖片來源:Texas Instruments)

圖 4:Texas Instruments 的 LF398MX/NOPB 取樣保持方塊圖展示了關鍵的元件:快速開關與外部保持電容。(圖片來源:Texas Instruments)

取樣保持的特性

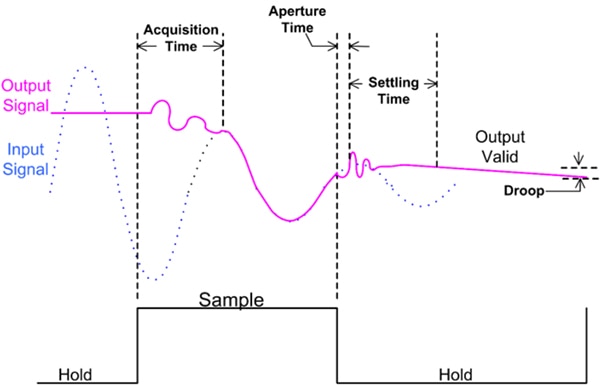

取樣保持元件具有一系列特定術語,用於描述自身的運作 (圖 5)。

圖 5:常見的取樣保持動態特性,其定義包含擷取時間、趨穩時間、孔徑時間以及振幅衰退。(圖片來源:DigiKey)

圖 5:常見的取樣保持動態特性,其定義包含擷取時間、趨穩時間、孔徑時間以及振幅衰退。(圖片來源:DigiKey)

擷取時間指的是從切換至取樣模式,到取樣保持開始追蹤輸入訊號為止的這段時間。此時間會隨著保持電容值以及開關與訊號路徑的串聯電阻而變化。當回到保持模式時,可能會出現時間延遲現象,直到元件停止追蹤輸入並開始保持某個值為止 — 這就是孔徑時間。孔徑時間會隨著驅動器與開關的傳播延遲而變化。孔徑不確定性或抖動指的是,孔徑時間因時脈變動及雜訊而發生的變異。

在保持模式中,在「進入該模式」和「元件趨穩至保持值的誤差帶內」之間會有一段時間,稱為趨穩或保持趨穩時間。在趨穩時間中,有時可能會在開關驅動器和保持電容之間進行不當的電荷傳輸;這個現象稱為保持步進或基底誤差。保持步進的幅度通常落在 mV 範圍,並且盡可能將訊號的滿量程範圍維持在高點,以便將其作用降到最低。

取樣保持的最短取樣時間,為擷取時間、孔徑時間及趨穩時間的總和。 可達成的最大取樣率,是擷取時間、孔徑時間及趨穩時間之總和的倒數。

在保持模式下,取樣保持的保持值可能會因保持電容洩漏而減小。此電壓增量情形稱為衰退。其通常以 mV/s 的衰退率來表示。

取樣保持配置

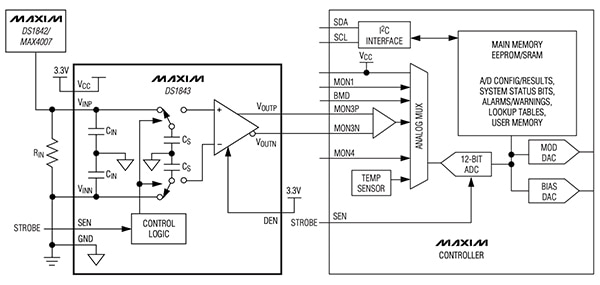

取樣保持 IC 提供多種配置,以滿足應用需求。考量一個需要差動輸入的應用,例如與加速計、應變計或光學電流監測器等差動輸出傳感器進行介接。在適合此類應用的取樣保持 IC 中,Maxim Integrated 的 DS1843D+TRL 就是個很好的範例 (圖 6)。

圖 6:如同這個典型的運作電路中所示,Maxim Integrated 的 DS1843+TRL 是一款差動取樣保持元件,其使用雙通道保持電容來實作差動取樣。(圖片來源:Maxim Integrated)

圖 6:如同這個典型的運作電路中所示,Maxim Integrated 的 DS1843+TRL 是一款差動取樣保持元件,其使用雙通道保持電容來實作差動取樣。(圖片來源:Maxim Integrated)

圖中的 DS1843+TRL 置於典型的光訊號線傳輸應用中,以進行突衝模式接收訊號強度指標 (RSSI) 量測。Maxim Integrated 的 DS1842/MAX4007 是一款電流監測器,可從連接至參考輸入的突崩光電二極體來鏡射電流。輸出電流會導向流經電阻 RIN,將其轉換為電壓。DS1843 會以差動方式測量此電壓,而該元件內含全差動取樣開關、電容 CS,以及差動輸出緩衝器。這款取樣保持元件使用兩個 5 pF 電容,一個連接至正極差動輸入,另一個接至負極差動輸入。低電容值可確保快速的擷取時間。這款元件的取樣 (擷取) 時間很短,低於 300 ns。取樣保持的保持時間超過 100 µs。

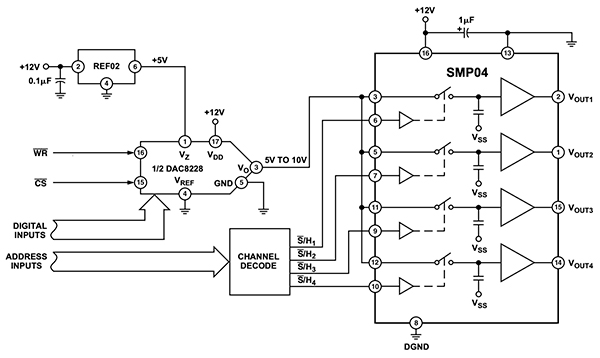

有些元件能在單一 IC 封裝中容納四個或八個取樣保持電路。Analog Devices 的 SMP04ESZ-REEL 四通道取樣保持元件就是一個範例。SMP04ESZ-REEL 是一款採用一般封裝的 CMOS 元件,當中納入四個取樣保持電路,擷取時間為 7 µs,衰退率僅為 2 mV/s (圖 7)。

圖 7 也說明取樣保持元件能如何搭配數位類比轉換器 (DAC) 使用;此例中是用於避免因 DAC 中的程式碼轉換,而導致發生輸出暫態或突波。

圖 7:Analog Devices 的 SMP04 四通道取樣保持元件內含四個獨立的取樣保持電路,以及匹配的緩衝放大器。圖中的電路使用 SMP04,以將 DAC 的輸出多工處理至四個通道。(圖片來源:Analog Devices)

圖 7:Analog Devices 的 SMP04 四通道取樣保持元件內含四個獨立的取樣保持電路,以及匹配的緩衝放大器。圖中的電路使用 SMP04,以將 DAC 的輸出多工處理至四個通道。(圖片來源:Analog Devices)

在圖中,SMP04 是用來對 DAC 的輸出進行多工處理,將單一 DAC 輸出拆分至四個多工通道。取樣保持電路可用於選擇性地將 DAC 的輸出延遲到突波之後,藉此撫平 DAC 輸出。

多個取樣保持電路可用來將多工輸入進行管線化,藉此增加 ADC 的傳輸量。此處是將多個取樣保持元件,共同連接至多工器輸出。ADC 連接到一個取樣保持元件,後者會針對轉換作業保持輸入位準。其他的取樣保持元件擷取其他的多工器通道,並依序連接至 ADC,而第一個取樣保持元件能自由連接至其他的多工通道。這樣的管線化技術,能消除 ADC 訊號路徑中的取樣保持擷取時間。

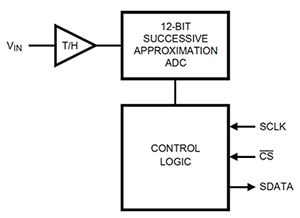

許多 ADC 都在各自的整合式封裝中,納入取樣保持或追蹤保持電路。其中一個範例是 Texas Instruments 的 ADC121S021CIMFX,這是一款 12 位元的連續漸近暫存器 (SAR) ADC,內建追蹤保持電路,取樣率範圍為 50 至 200 kS/s。該元件具有高速序列輸出匯流排,能夠簡化接線佈局 (圖 8)。

圖 8:Texas Instruments 的 ADC121S021 是一款 12 位元單通道 SAR ADC,內建有追蹤保持電路。(圖片來源:Texas Instruments)

圖 8:Texas Instruments 的 ADC121S021 是一款 12 位元單通道 SAR ADC,內建有追蹤保持電路。(圖片來源:Texas Instruments)

這款 ADC 是許多整合式 ADC 電路的典型,因其具有內部追蹤保持元件,能夠簡化電路板佈局,並有助於將元件數降到最低。外部追蹤保持電路可用於特殊的配置,例如差動輸入連接、多工輸入等等,或在 ADC 沒有內部追蹤保持或取樣保持電路時使用。

結論

從錄音到最先進的 IIoT 或 AI 分析,若要實作最基本的電路功能 — 即將類比訊號轉換為數位訊號,則需要謹慎留意取樣保持或追蹤保持電路。這些必要元件可用於在進行類比數位轉換期間,將電壓偏斜誤差降到最低,因為它們會在轉換過程中讓 ADC 的輸入電壓保持恆定。取樣保持元件可置於 ADC 的內部或外部,但必須位於抗交疊低通濾波器和 ADC 之間的訊號路徑上。如本文所述,為了滿足各種設計應用,配置種類很多,每個 IC 可配置單一元件、差動元件或多個元件。這些應用還包括能避免因 DAC 中的程式碼轉換,而導致輸出暫態或突波。

推薦閱讀

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。