ADC/DAC 教學

資料提供者:DigiKey

2017-09-13

現今的世界滿佈數位與類比訊號。雖然這些訊號的行為各有不同,但為了達成更大的目標,通常兩種訊號都會用到。想像有一位工程師要控制 HVAC 單元。若規劃要使用微控制器或微處理器,就必須具備類比溫度的判讀能力,溫度可能是無限大值,且必須轉換成以離散步進呈現的二進位表述。類比值的二進位表述接著會由微控制器或微處理器進行處理。這項資料將會由 HVAC 單元用來協助執行流程,以協助維持環境穩定。對於需要由數位系統進行處理的類比值,類比數位轉換器 (ADC) 是必備元件。同樣的,這個理論也能反過來套用在需要轉換成類比訊號的數位訊號。要在線上串流一首歌,牽涉到幾個不同的步驟,可將數位訊號轉換成類比訊號。主機裝置從伺服器接收到的訊號,匯市原始類比訊號的二進位表述。聆聽者並無法理解此二進位資料當中的聲音反應。原始的訊號屬於類比型式,因此最終呈現方式也必須是類比型式。使用數位類比轉換器 (DAC) 便能夠解決這項問題。這類型元件會取得由類比數位轉換器所編碼的二進位碼,然後將其轉換回類比電壓。

對現今的工程師來說,將訊號從類比轉數位或從數位轉類比是無可避免的工作。市面上有許多不同類型的類比數位轉換器以及數位類比轉換器。雖然彼此的架構有所不同,但最終作用非常類似。數位訊號處理作業無法用類比值來進行,這就好比說法語的人無法跟說德語的人溝通一樣,必須要有翻譯人員才行。而 ADC 與 DAC 元件可以像翻譯人員一樣提供協助。當 ADC 查覺到類比電壓時,其工作便是在指定時間內將類比電壓轉換成二進位碼。這表示,ADC 會在一瞬間對類比電壓進行取樣,然後決定如何在 ADC 的輸出端以二進位值表示。此元件每秒所取樣的樣本數會記錄在文件中。舉例來說,Maxim Integrated 的 MAX1118EKA+T 就是此類元件之一。這個元件具有 100 kHz 取樣率,因此每秒能夠對輸入端的類比電壓進行 100,000 次取樣。每秒能進行如此多次取樣,因此此元件能使用二進位表述來準確記錄類比電壓的情況。ADC 的取樣率有時候不夠高,難以精確重現輸入訊號而導致混疊。在此情況下,訊號之間會開始變得無法判別,或彼此混疊。這就像有一台攝影機,每秒只能拍攝 24 個畫格。對大部份應用來說,這樣的規格已經夠用;但若要觀看超快速度移動的畫面,就會發現影像失真。回想一下觀看九零年代末期所錄製的電視節目影片時的體驗。電視上的影像可能會出現閃爍。這是因為電視機本身的更新率比錄影的每秒畫格數快很多。影像之所以失真,是因為影片本質上是一連串的圖片。比起影片中所呈現的畫面,每張圖片之間實際上還有更多細節。使用 ADC 時,也會發生相同的情況。為了避免此情況,必須確保取樣率比需要傳輸的最高頻率高出至少兩倍。這個比例稱為奈奎斯特速率。

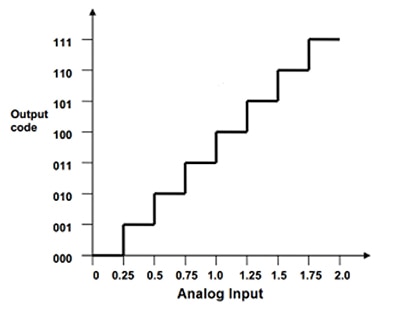

使用較高的取樣率能讓元件更加準確,但這不是控制準確度的唯一方法。由於這類元件是將類比訊號轉換成二進位碼,離散步階的數量有限,可用來表示某個時間點的電壓。可用來表示這個數字的位元數,稱之為解析度。ADC 的解析度越高,就可取得更多離散步階。為了進一步詳細說明,必須瞭解如何決定 ADC 能產生的步進數。ADC 具有二進位輸出,代表著電源電壓。若電源電壓為 10 V,且具有 8 位元 ADC,則可能有 256 階。判斷解析度時會使用 2n 這個方程式。「2」是常數,而 N 是位元數。28 表示我們會獲得 256 階。使用 256 階搭配 10 V 電源,表示每一階是 39.0625 mV。每一階的二進位碼都不同。若我們逐一檢視 ADC 從最低到最高的所有可用輸入選項,會看到階梯形的曲線。這個階梯代表 ADC 的傳輸功能。圖 1 指出 3 位元 ADC 在 2 V 參考電壓下的傳輸情況。

圖 1:3 位元 ADC 在 2 V 參考電壓下的傳輸功能。(圖片來源:Microchip Technology)

由於位元數為 3,因此可使用 2n 方程式來計算總階數,如下所示:

![]()

如圖 1 所示,000 與 111 之間共有 8 階。每一階都會提高一個 LSB。

誠如上述,ADC 有多種不同類型的架構。三種最常見的 ADC 架構分別是連續漸近暫存器 (SAR)、三角積分 (ΔΣ) 以及管線式轉換器。每個架構都可將類比訊號轉成數位輸出,但作法上彼此仍有些許差異。SAR 會對類比輸入進行取樣並保留,將其轉變成數位訊號後再送出。三角積分轉換器會對一段時間內的樣本取平均,將其轉換為數位訊號。管線式轉換器會將轉換作業分為不同階段,以達到超快轉換速度。每種架構都各有優缺點。SAR 架構相當容易使用,通常較低耗電,並且具有低延遲時間和高準確度。三角積分架構能以低耗電和低成本提供超高解析度和高穩定性,但是速度比起 SAR 與管線式架構慢很多。管線式 ADC 速度較快,且頻寬比前兩種高,但解析度較低且運作時需要消耗較多電力。

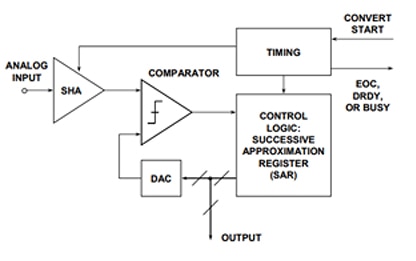

連續漸近暫存器

連續漸近暫存器是最受歡迎的 ADC 類型。這些元件通常具有 I2C 或 SPI 介面,但有時候會使用平行輸出介面。為了協助處理類比訊號,SAR ADC 會進行取樣並保留,試著維持訊號恆定。具有比較器,可測量類比輸入,並對照內部 DAC。此 DAC 此時會設定成潛在電壓的二分之一。若輸入訊號高於 DAC,比較器將會輸出 1 的訊號,將其儲存在「連續漸近暫存器」的 MSB 當中。之後 DAC 將會設定為潛在電壓的四分之一,然後重複此流程。DAC 的下一個值是 1/8、1/16,依此遞進,直到所有的位元都已載入到暫存器中為止。有個比喻可協助說明此作用,就是連續加上或不加上砝碼來測量某個物體的重量。下圖 2 說明了這點。

圖 2:連續漸近 ADC 如何從類比值得出數位值的示意圖。(圖片來源:Analog Devices)

一塊大積木 = 45 個單位;第一個測試是使用 32 個各自為 1 個單位的小積木。大積木的重量仍大於這些小積木。因為大積木的重量仍然較重,因此保留這 32 個小積木。下一個測試是再加上 16 個小積木。這樣一來 32 + 16 等於 48,反而太重。因為太重的關係,要捨棄這 16 個小積木。下一個測試是將 8 個積木加到磅秤上,因為 32 + 8 等於 40,所以可以加上這 8 個。然後還可以再加進 4 個積木,讓總數達到 44 個。之後再加進兩個積木,但這樣會變成 46 個單位,這個數量大於 45 個單位,因此要取出這兩個積木。最後會加進一個積木,讓兩邊的積木重量相等。每次要加上積木時,加入的數量會減半。這種方式便代表著 SAR DAC 的取值方式。圖 3 顯示連續漸近暫存器 ADC 的方塊圖。

圖 3:連續漸近 ADC 功能方塊圖(圖片來源:Analog Devices)

Texas Instruments 的 ADS7886SDBVT 就是 SAR DAC 的一個例子。這是一款 12 位元 ADC,表示在 0 V 與供應電壓之間可以取得 4,096 階。取樣率為 1 MHz,表示這個元件每秒會檢視輸入訊號 100 萬次。在將 ADC 納入最終產品前,必須先測試 ADC 的性能,因此製造商通常會製作評估工具來協助測試。ADS7886SDBVT 提供此類評估工具,即 ADS7886EVM。這可大幅簡化測試作業,因為板件上已經搭載所有被動元件,可提供 ADC 測試所需的必要功能。

三角積分 ∆∑

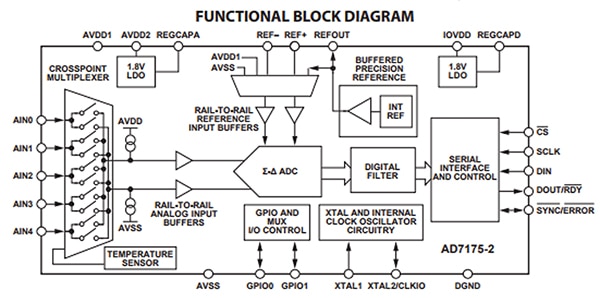

對於需要高解析度與精密度的應用,三角積分轉換器是相當受歡迎的選擇。在三角積分轉換器的應用中,錄音是個很好的例子。三角積分轉換器必須對輸入訊號進行超取樣。對於三角積分轉換器來說,奈奎斯特速率的關聯性並不高,在取樣率高於待取樣訊號的最高頻率約 20 倍時,即可達到最佳工作效果。三角積分轉換器的輸出訊號會饋入數位濾波器與降頻器,對位元流進行處理後產生最終輸出訊號。通常在數位濾波器與輸出端之間會有一個序列介面。Analog Devices, Inc 的 AD7175-2BRUZ 就是三角積分 ADC 例子之一。圖 4 指出 AD7175-2BRUZ 的「功能方塊圖」。

圖 4:Analog Devices 的 AD7175-2BRUZ 三角積分 ADC 功能方塊圖。(圖片來源:Analog Devices)

這款三角積分 ADC 具有 24 位元解析度與 250 kHz 取樣率,因此可達到最高 16,777,216 階。也就是說,此元件的解析度比上一個例子更高,但取樣率只有四分之一。如同上一個例子,AD7175-2BRUZ 同樣提供測試用的評估板。這評估板型號是 EVAL-AD7175-2SDZ,能以輕鬆的方式評估 ADC。

管線式

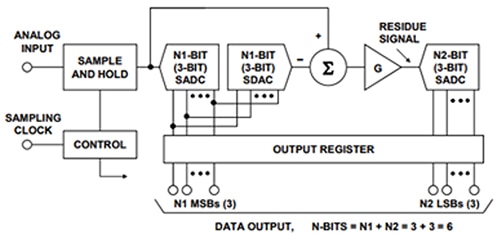

管線式 ADC 的速度最快。「ADC 架構 V:管線式子區間 ADC」一文中有個例子有助於說明如何使用 6 位元管線式 ADC。取樣與保留的做法跟 SAR 類似,但是在進行取樣與保留後,有個 3 位元的子區間 ADC 快閃轉換器會對訊號進行數位化。此 3 位元轉換作業是針對 3 個最高有效位元進行。這個過程會使用子區間 DAC 將訊號轉換回類比訊號。這個輸出訊號會從取樣與保留輸出訊號中去除,在放大後送回第二階段的 3 位元子區間 ADC,以取得剩下的三個最低有效位元。圖 5 的方塊圖能說明此論點。

圖 5:管線式子區間 ADC 功能方塊圖。(圖片來源:Analog Devices)

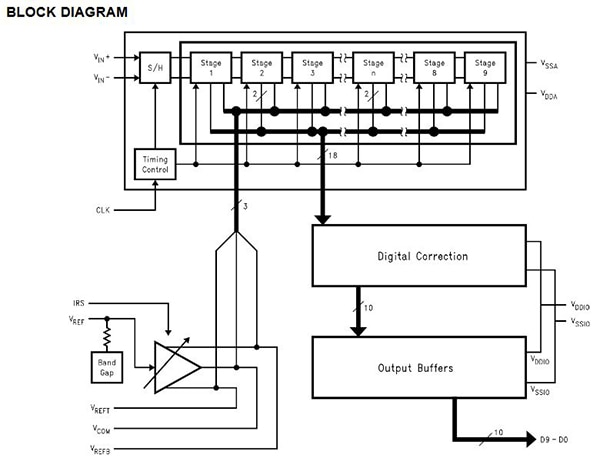

Texas Instruments 的 ADC10080CIMT/NOPB 是管線式 ADC 的一個例子。這是一款 10 位元 ADC,表示可以取得 1,024 階,且轉換率為 80 MSPS。此元件可用於超音波與造影、儀器、數據採集系統,或是任何需要快速轉換的應用。查看 ADC10080CIMT/NOPB 方塊圖後,就可瞭解此元件如何用上述方式進行設定。圖 6 的方塊圖取自 ADC1008CIMT/NOPB 的規格書。

圖 6:Texas Instruments 的 ADC10080CIMT/NOPB 功能方塊圖。(資料來源:Texas Instruments)

二進位加權 DAC

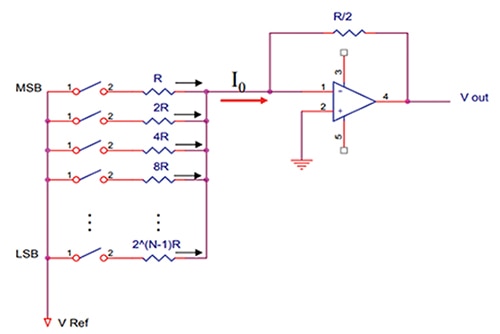

截至目前為止,本文重點都擺在資料轉換作業中的 ADC 層面,但這只是整個過程的一半而已。二進位資料通常必須轉換回類比訊號。此時就需要用到數位類比轉換器。學校教的第一種 DAC 通常就是二進位加權 DAC。其中必須使用一套電阻系統,其輸出全部都會送到同一個加總電阻。最高有效位元會輸出比最低有效位元更多的電流。只要建立反比例電阻式網路就可達到此效果。由於每個數位碼的二進位位元都具有相同的電壓值,在各個位元上使用反比電阻,更有效的位元就可讓更多電流通過。此特定轉換方法已經不常使用,因為現在有許多更簡單的方法,但這仍是說明 DAC 運作方法的良好起點。此方法最大的困難點在於找到可一同運作的不同電阻。容差必須相當嚴密,因此找幾個相似值的電阻,會比幾個不同值的電阻 (如二進位加權法所用的電阻) 更加簡單。圖 7 使用二進位加權電阻網路的線路圖來說明此架構。

圖 7:二進位加權暫存器網路的線路圖。(圖片來源:Georgia Institute of Technology)

電阻串 DAC

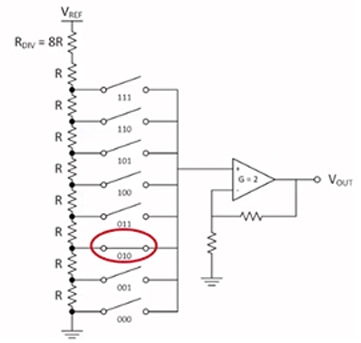

另一種常見的 DAC 架構是電阻串 DAC。這是最簡單的架構,但也是最不具有線性的架構,有時候稱為 Kelvin 分壓器。其中具有一系列串聯的等值電阻。這串電阻的頂端具有參考電壓、電阻串前有一個高阻抗電阻,且每個節點都有一個專門用於二進位碼的開關,會在元件讀取二進位碼時關閉。如此一來,就可使用類比電壓值 (受二進位輸入影響)。圖 8 取自 Texas Instruments 提供的一段影片:「電阻串 DAC 是什麼?」。十進位值 2 所選定的二進位碼為 010。010 處的開關現在會關閉,讓該節點的 DC 電壓通行到加總放大器。

圖 8:電阻串 DAC 線路圖。(資料來源:Texas Instruments)

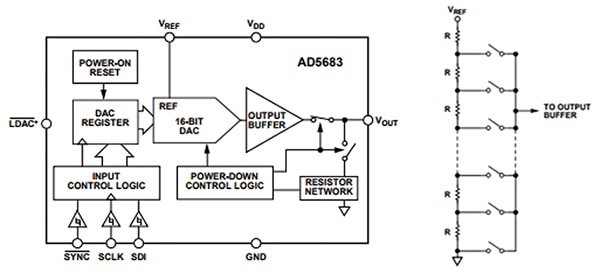

電阻串 DAC 相當容易生產,因為在電阻串的每一個部位都使用相同值的電阻 (排除高阻抗電阻)。Analog Devices Inc 的 AD5683RBRMZ 就是電阻串 DAC 的一個例子。此 16 位元電阻串 DAC 可搭配 SPI 運作。圖 9 指出此元件的功能方塊圖,圖 10 則說明電阻分壓器。此產品也提供評估工具:EVAL-AD5683RSDZ

圖 9 與 10:Analog Devices 的 AD5683RBRMZ 功能方塊圖 (左),及其電阻分壓器網路 (右)。(圖片來源:Analog Devices)

R-2R

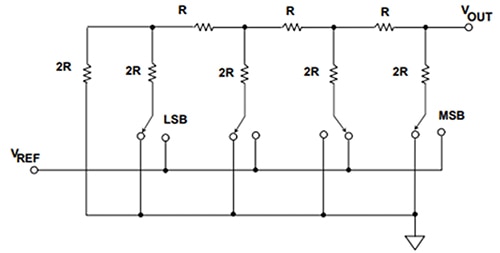

R-2R 網路是非常常見的 DAC 架構。此架構只使用兩個電阻值,只要 2R 是 R 的兩倍大,值本身便不重要,因此 R-2R DAC 極具擴充能力。無論 DAC 有多少個位元,電阻都只需要兩個值。圖 11 顯示 4 位元 R-2R 梯狀網路。

圖 11:R-2R DAC 的線路圖。(圖片來源:Analog Devices)

此分壓器網路採用 Thevenin 定理,最終目標是對整個網路取得 Thevenin 等效串聯電阻「R」。每個階段都會讓上一個階段的電壓加倍。舉例來說,若 Vref 為 5 V,則 LSB 最左邊的階段只能夠產生 0.3125 V。從左到右的比例式電壓輸出為:

![]()

這個方程式代表所有的數位輸入,X0 為 LSB,X3 為 MSB。使用 5 V 的參考電壓會得出:

![]()

在相同邏輯下,若要找出最高有效位元的類比電壓,可以透過以下計算:

![]()

若有一個二進位輸入值為 1111,輸出訊號不會等於 5 V。請回想前面對於解析度的討論。若使用 4 位元 DAC,訊號應會有 16 階。這是因為 24 會得出 16 階。LSB 為 0.3125 V,若要將 0.3125 x 16,會求得 5 的答案。這樣的結果其實具誤導性,因為其中一階包含 0 V 接地電壓,以二進位值 0000 表示。也就是說,可達到的最高電壓是供應電壓減去一個 LSB 電壓。因此可得到 4.6875 V 的結果。

![]()

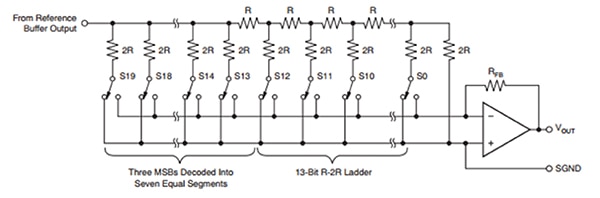

Texas Instruments 的 DAC8734SPFB 是 R-2R DAC 的例子之一。這款 16 位元轉換器能顯示此元件的擴充潛力。此元件的 R-2R 網路配置與上述說明非常類似。圖 12 顯示 DAC8734SPFB 的 R-2R 網路。DAC8734SPFB 也提供評估工具:DAC8734EVM。

圖 12:Texas Instruments 的 DAC8734SPFB R-2R DAC 線路圖。(資料來源:Texas Instruments)

ADC/DAC 架構還有許多其他類型,但本文只討論最常使用的幾種架構。在現今的數位訊號處理領域中,這些元件是不可或缺的要素。若是沒有 ADC/DAC,就無法將類比輸出整合到任何數位訊號處理機制當中,反之亦然。外行人可以將這件事視為理所當然,但對於負責將類比元件連接到數位系統的工程師來說,這是要納入考量的重大步驟之一。在想到類比轉數位時,請回想兩個人各自說不同語言的比喻。若這兩個人沒有翻譯員從旁協助,便無法彼此溝通。若未適當利用 ADC/DAC,裝置就要嚴格採用全類比或全數位架構。ADC/DAC 元件是這兩種架構之間的絕佳橋樑。

資源

- “AVR127: Understanding ADC Parameters”.May.2016.

- “Choose the right A/D converter for your application”.Retrieved 8 May.2017.

- Kester, Walt.“ADC Architectures II: Successive Approximation ADCs”.Oct. 2008.

- Kester, Walt.“ADC Architectures III: Sigma-Delta ADC Basics”.Oct. 2008.

- Kester, Walt.“ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications”.Oct. 2008.

- Kester, Walt.“ADC Architectures V: Pipelined Subranging ADCs” Oct. 2008.

- Kester, Walt.“DAC Interface Fundamentals”.Oct. 2008.

- Kester, Walt.“Basic DAC Architectures II: Binary DACs”.Oct. 2008.

- Lee, J., Jeelani K., Beckwith, J. “Digital to Analog Converter”.Retrieved 8 May.2017

- Poole, Matt.“What is a String DAC?”.April 4, 2016

聲明:各作者及/或論壇參與者於本網站所發表之意見、理念和觀點,概不反映 DigiKey 的意見、理念和觀點,亦非 DigiKey 的正式原則。