ADAU1860 Low-Power Codec

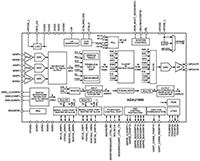

Analog Devices' ADAU1860 low-power codec has three ADCs, one DAC, and two audio digital signal processors (DSPs)

ADI's ADAU1860 is a codec with three inputs and one output incorporating two DSPs. The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise-canceling earphones. With the addition of just a few passive components, the ADAU1860 provides a complete earphone solution.

ADI's ADAU1860 is a codec with three inputs and one output incorporating two DSPs. The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise-canceling earphones. With the addition of just a few passive components, the ADAU1860 provides a complete earphone solution.

The EVAL-ADAU1860EBZ provides access to all the analog and digital inputs and outputs on the ADAU1860. The ADAU1860 core is controlled by ADI's Lark Studio™ software, which interfaces to the EVAL-ADAU1860EBZ via a USB connection. In addition, users can communicate and debug with the Tensilica HiFi 3z DSP core through the JTAG port using the mIDAS-Link emulator. Analog Devices also provides the software development kit (SDK) for code development.

The EVAL-ADAU1860EBZ can be powered by a USB bus or a 5 V supply, regulated to the voltages required on the EVAL-ADAU1860EBZ. The printed circuit board (PCB) is a 4-layer design, with a ground plane and a power plane on the inner layers. The EVAL-ADAU1860EBZ contains connectors for external microphones and speakers. The master clock can be provided externally or by the on-board 24.576 MHz oscillator.

- Programmable FastDSP audio processing engine

- Up to 768 kHz sample rate

- Biquad filters, limiters, volume controls, mixing

- Tensilica HiFi 3z DSP core

- Quad MAC per cycle: 24 x 24-bit multiplier and 64-bit accumulator

- Flexible power operation mode: 24.576 MHz, 49.152 MHz, 73.728 MHz, and 98.304 MHz

- 336 kB total memory

- JTAG debug and trace

- Low latency, 24-bit ADCs and DAC

- 106 dB SNR (signal through ADC with A-weighted filter)

- 110 dB combined SNR (signal through DAC and headphone with A-weighted filter)

- Power supplies

- Analog AVDD at 1.8 V typical

- Digital I/O IOVDD at 1.1 V to 1.98 V

- Digital DVDD at 0.85 V to 1.21 V

- Headphone HPVDD at 1.8 V typical

- Headphone HPVDD_L at 1.2 V to HPVDD

- Control/communication interfaces

- I2C, SPI, or UART control ports

- Master quad SPI (QSPI)

- UART communication port

- Programmable double precision MAC engine for maximum 24-stage equalizer

- Serial port sample rates from 8 kHz to 768 kHz

- 5 μs group delay (fS = 768 kHz) analog in to analog out with FastDSP bypass (zero instructions)

- Three differential or single-ended analog inputs, configurable as microphone or line inputs

- Eight digital microphone inputs

- Analog differential audio output, configurable as either line output or headphone drive

- Two PDM output channels

- PLL supporting any input clock rate from 30 kHz to 36 MHz

- Four channel asynchronous sample rate converters (ASRCs)

- Two 16-channel serial audio ports supporting I2S, left justified, right justified, or up to TDM16 (TDM12 in turbo mode)

- Eight interpolators and 8 decimators with flexible routing

- Self-boot from QSPI Flash

- Flexible GPIO and IRQ

- 56-ball, 0.35 mm pitch, 2.980 mm × 2.679 mm WLCSP

ADAU1860 Low Power Codec

| Image | Manufacturer Part Number | Description | Available Quantity | Price | View Details | |

|---|---|---|---|---|---|---|

|  | ADAU1860BCBZRL | 56-BUMP WAFER LEVEL CHIP SCALE P | 3671 - Immediate | $147.63 | View Details |

|  | ADAU1860-1BCBZRL | 3ADCS 1DAC LOWPOWER CODEC WITH A | 0 - Immediate | See Page for Pricing | View Details |

Evaluation Board

| Image | Manufacturer Part Number | Description | Available Quantity | Price | View Details | |

|---|---|---|---|---|---|---|

|  | EVAL-ADAU1860EBZ | EVAL BOARD FOR ADAU1860 | 27 - Immediate | $3,985.04 | View Details |