Take Advantage of I3C for Faster, Simpler, and More Flexible IC-to-IC Communication

Contributed By DigiKey's North American Editors

2024-12-17

Onboard serial interfaces for integrated circuit (IC)-to-IC communications are dominated by the Inter-Integrated Circuit (I²C) and the Serial Peripheral Interface (SPI), which have been available since the 1980s. These interfaces are widely used for connecting lower-speed sensors and ICs to microcontroller units (MCUs) for intra-board communication over short distances. However, as digital systems get faster, these interfaces, limited to typical data rates of 1 megabit per second (Mbit/s) for I²C and 10 Mbits/s for SPI, have become a limiting factor. Other limitations, including dedicated interrupt or chip enable lines, require additional signal connections, increasing the number of wires and complexity of the bus connections.

The Improved Inter-Integrated circuit (I3C) bus is intended to upgrade inter-IC communications. It offers higher data rates, greater flexibility, and a true two-wire interface with in-band interrupts (IBIs) instead of external ones.

This article discusses the characteristics of the I3C interface and why it might be a good upgrade from the I²C and SPI serial interfaces. Typical MCU, IC switch, and sensor devices will be used to show its application.

Embedded communications buses

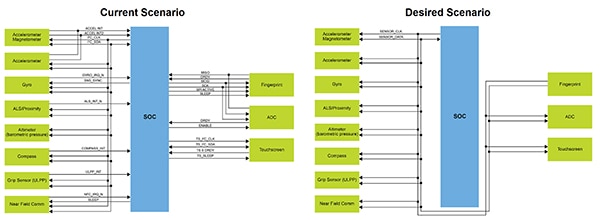

Embedded serial interconnects like I²C and SPI have been employed for many years for intra-board communications. They are primarily used as communications buses between sensors and user interface devices and their control processors. The number of sensors in typical systems has grown to ten to twenty in a phone and significantly more in vehicles. At the same time, communication requirements have become more challenging for designers as the demand increases for higher speed, lower power consumption, and fewer conductors. Designers must meet these demands while maintaining processor control via interrupts and enable lines (Figure 1).

Figure 1: Embedded communications should support higher speeds, lower power, and a minimum wire count. (Image source: NXP Semiconductors)

Figure 1: Embedded communications should support higher speeds, lower power, and a minimum wire count. (Image source: NXP Semiconductors)

Current technology implements the sensor and user control device interface using two-wire I²C or four-wire SPI interfaces. Interrupt, enable, and other control lines are separate from the clock and data lines, resulting in more lines per interface.

Designers need a more forward-looking interface approach that eliminates these extra conductors from the interconnects and handles those operations in-band using only the clock and data lines. Additionally, the bus should be able to operate at higher speeds and with lower power losses.

I3C interface

I3C was developed by the Mobile Industry Processor Interface (MIPI) Alliance to address these requirements. The interface is available both as MIPI I3C to MIPI members, and as MIPI I3C Basic with reduced functionality to non-members. Like the legacy I²C and SPI interfaces, the improved form is serial and is implemented using two wires to minimize pin counts and the number of signal paths between components. It has a data rate up to 12.5 Mbits/s with a 12.5 megahertz (MHz) clock using single data rate (SDR) mode. It operates at lower power levels and uses a simple yet flexible design architecture.

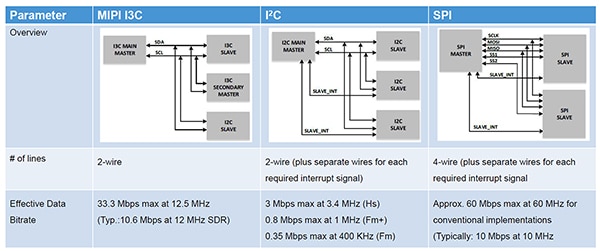

Notably, the I3C standard retains limited backward compatibility with the I²C system, allowing existing I²C devices to be connected to the I3C bus, while still allowing the bus to switch to higher data rates for communication between compliant I3C devices. A comparison of the system configurations is shown in Figure 2.

Figure 2: Comparing the basic configurations of I3C, I²C, and SPI interfaces shows I3C’s improved speed and simpler wiring. (Image source: NXP Semiconductors)

Figure 2: Comparing the basic configurations of I3C, I²C, and SPI interfaces shows I3C’s improved speed and simpler wiring. (Image source: NXP Semiconductors)

The four-wire SPI interface can operate faster and supports full duplex communication. I²C communicates using half duplex over a two-wire bus consisting of a clock (SCL) and data (SDA) lines. Both require extra lines to support interrupts and other control functions such as chip select. I3C reduces the number of wires used in the interface to two, eliminating the separate interrupt, enable, and chip select lines used in I²C and SPI. This reduction in wire count is a significant advantage in a system requiring ten to twenty individual sensors tied to the processor, each with several secondary wires. Interrupts and other control lines are replaced by IBIs. In this method, a target sensor or device imposes its address into the I3C bus address header to notify the processor of an interrupt.

The difference in clock rates between I²C and I3C is significant. I²C is generally clocked at 100 kilohertz (kHz), 400 kHz, or 1 MHz, while I3C can be clocked at 12.5 MHz. Previously, SPI was used for clock rates higher than 1 MHz. The design selection was between the clock rate and the number of wires. I3C has changed that by offering higher clock and data rates using a true two-wire topology.

Push-pull outputs, which can switch faster than open-drain or collector drivers, are significant contributors to I3C’s increased clock rate. To maintain compatibility with I²C devices, I3C can switch between open-drain and push-pull drivers depending on the bus state. The open-drain or collector design is used during initial addressing or arbitration, where both I²C and I3C devices may be on the line simultaneously. I3C uses push-pull when communication is unidirectional, and there is no chance of an I²C device communicating simultaneously.

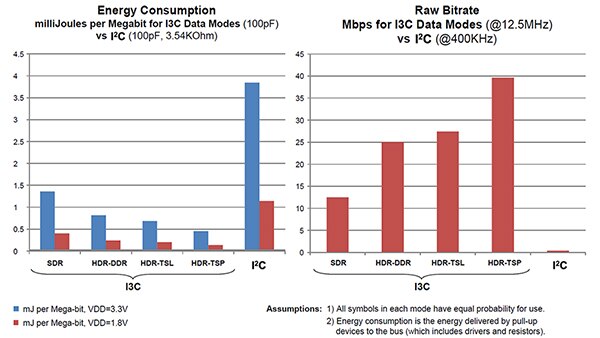

In addition to the standard SDR, I3C supports several optional high data rate (HDR) modes. These HDR modes operate with the same clock rate but transmit with a higher data density. The first of the HDR modes is HDR double data rate (HDR-DDR), where data is clocked on both edges of the clock signal, providing nearly two times the data rate. For a 12.5 MHz clock, the DDR mode achieves an effective data rate of 20 Mbits/s.

HDR ternary symbols have dual versions: HDR ternary symbol, pure (HDR-TSP) for I3C devices only, and HDR ternary symbol, legacy (HDR-TSL) for buses including both I²C and I3C devices. Ternary symbol modes achieve three data bits per clock using three-bit (ternary) symbols encoded on the SCL and SDA lines.

HDR bulk transport (HDR-BT) mode offers the highest data by supporting communications over quad, dual, or single SDA data lines. This results in eight, four, or two times the raw single data rate performance at the same clock rate.

These increases in the data transfer speed allow devices to be turned on for a shorter period, reducing the bus power duty cycle. This reduces power consumption compared with I²C (Figure 3). The change from open-collector drivers with external pull-up resistors to push-pull drivers further reduces power consumption, as the pull-up resistors require significant power to operate.

Figure 3: I3C offers improvements in data rate and power consumption compared with I²C. (Image source: NXP Semiconductors)

Figure 3: I3C offers improvements in data rate and power consumption compared with I²C. (Image source: NXP Semiconductors)

Addressing

I²C uses static addresses of either 7 or 10-bit length for each bus device. This has been changed in I3C to 7-bit dynamic addressing, where the bus master sets the device address during dynamic address assignment (DAA), and stores it in a device register. Static addressing, as in the case of an I²C peripheral, can still be used in I3C.

Due to dynamic addressing, device addresses can be changed later. This supports hot joining, which allows a new device to be added to the bus while it operates. The new device, connected to the I3C bus, signals its presence to the I3C master by sending a hot join request. The master controller acknowledges the request and assigns an address to add the device to the bus.

IBIs

I3C is a true two-wire bus that uses IBIs instead of dedicated interrupt lines like I²C. IBIs are when a target device signals its availability to the master by pulling down the SDA line. The master then starts the clock on the SCL line, and the target device transmits its address onto the I3C bus to notify the controller of an interrupt.

Common command codes

Common Command Codes (CCC) are standardized commands that the controller can transmit as a general broadcast to all I3C devices simultaneously or to a specific target device. These commands are for items related to bus management. The format of the CCC protocol begins with the I3C broadcast address, which is recognized by all I3C devices on the bus. Any I²C device on the bus will not acknowledge the request as it is a reserved I²C address.

Each command includes an 8-bit descriptor ID field and may be followed by a command payload. A command sent to a specific device passes the device address in the first byte of the payload. There are over forty CCC commands, including:

- Enter Dynamic Address Assignment (ENTDAA)

- Set New Dynamic Address Assignment (SETNEWDA)

- Enable Events (ENEC)/Disable Events (DISEC)

- Reset Dynamic Address Assignment (RSTDAA)

- Enter High Data Rate Mode (ENTHDRx)

- Get Device Characteristics Register (GETDCR)

Vendors are allowed a dedicated range of CCC IDs to implement their own commands.

Error detection and recovery

Unlike I²C, I3C includes provisions for error detection and recovery. Six error and recovery methods for target devices are mandated, and another is optional. Additional error and recovery methods are also available specifically for master-side errors.

I3C supported components

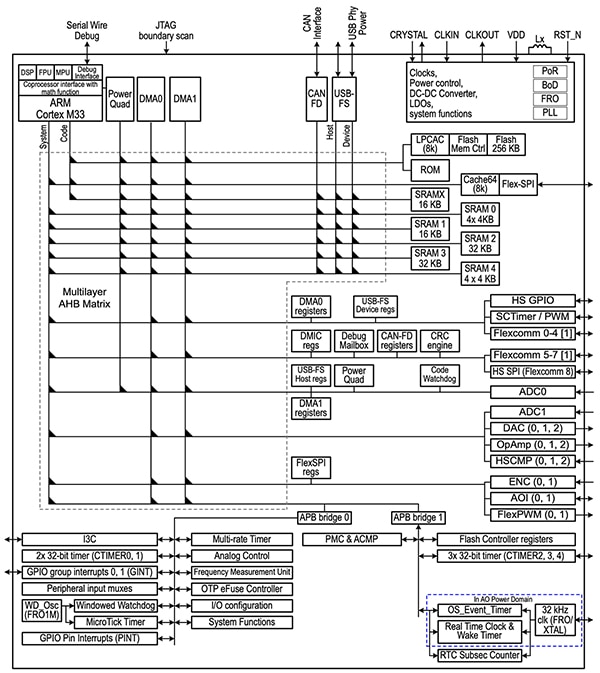

As shown in Figure 2 (left), a basic I3C network comprises at least one master controller and one or more I3C targets or slaves. The main master can be an MCU such as the NXP Semiconductors LPC5534JHI48-00MP (Figure 4). It is a 32-bit Arm® Cortex®-M33 MCU with 128 kilobytes (Kbytes) of SRAM and 256 Kbytes of Flash. Its Flexcomm interface supports eight different serial interfaces, including I3C.

Figure 4: The LPC5534JHI48/00MP MCU includes an I3C interface and seven other serial interfaces. (Image source: NXP Semiconductor)

Figure 4: The LPC5534JHI48/00MP MCU includes an I3C interface and seven other serial interfaces. (Image source: NXP Semiconductor)

The I3C bus allows the addition of secondary masters introduced to the bus as slaves. The I3C can have multiple masters, but only one can be the controller. Once enrolled, the secondary master can request the current master status, and if the current master accedes, its control is handed over to the requesting secondary master.

A typical I3C sensor is NXP’s P3T2030CUKAZ. This temperature sensor converts temperatures from -40°C to +125°C into a 12-bit digital value with an accuracy of ±2°C. It includes both an I²C and an I3C SDR mode serial interface.

A more sophisticated sensor is the ICM-42605 three-axis microelectromechanical systems (MEMS) gyroscope and accelerometer from TDK InvenSense. As a rate gyro, it measures spin rates from ±15.2 to ±2000 degrees per second (°/s). Its range as an accelerometer is ±2 to ±15 g. It detects motion, tilt, tap, or steps (pedometer). As an I3C sensor, it operates at 12.5 MHz in SDR mode and 25 MHz in DDR mode.

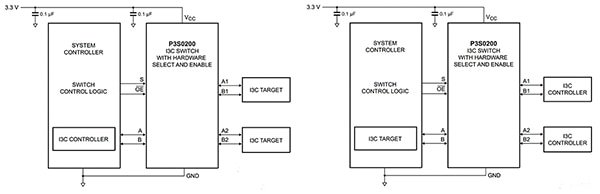

ICs such as the NXP P3S0200GMX I3C switch can reconfigure the I3C bus by routing I3C bus signals between an I3C controller and multiple sets of target devices, or between a single target and multiple I3C controllers as determined by an external MCU (Figure 5).

Figure 5: The P3S0200GMX I3C switch can be used to reconfigure an I3C bus by routing I3C bus signals between an I3C controller and multiple sets of target devices, or between a single target and multiple I3C controllers. (Image source: NXP Semiconductors)

Figure 5: The P3S0200GMX I3C switch can be used to reconfigure an I3C bus by routing I3C bus signals between an I3C controller and multiple sets of target devices, or between a single target and multiple I3C controllers. (Image source: NXP Semiconductors)

Switching between two targets might be required if both targets have the same address and cannot reside on the same bus. Alternatively, a single target might have to be shared between two processes, requiring a switch between the two I3C controllers.

Conclusion

I3C is a serial interface that extends the I²C bus by increasing its data rate, reducing the number of wires, and adding flexibility to the bus control. It is an enhancement that extends the usefulness of legacy I²C and SPI interfaces.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.